Analog-/Mixed-Signal-ICs

Beschaltung von schnellen Datenwandlern (Teil 2)

Fortsetzung des Artikels von Teil 1

Datenschnittstelle, LVDS und JESD204B

Als Datenschnittstelle trifft man bei der neuen Generation schneller Datenwandler neben LVDS immer mehr auf die serielle JESD204-Schnittstelle. Hierbei handelt es sich, ähnlich wie bei LVDS, um eine differenzielle Schnittstelle; allerdings gibt es ein paar wesentliche Unterschiede.

LVDS ist nach dem Standard TIA/EIA-644 mit 655 Mbit/s definiert. Derzeit findet man am Markt auch höhere Datenraten von 1 Gbit/s bis zu 3 Gbit/s. Der Sender speist typisch 3,5 mA in die Leitung und wird am Empfänger über einen 100-Ω-Abschluss, angepasst an die Leitung, zurück zum Sender geführt. Nach dem ohmschen Gesetz ergibt sich damit ein Spannunghub von 350 mV. Je nach Polarität wird ein Eins- bzw. Null-Signal aus dieser Spannung abgeleitet. Werden die Hin- und die Rückleitung so geführt, dass eine gute Kopplung besteht, ist dies eine störarme Übertragung.

Durch das differenzielle Übertragungsverfahren entstehen auf den Versorgungsleitungen bzw. -flächen keine ungewünschten Spannungssprünge, auch „ground bounce“ genannt, wie sie bei massebezogenen CMOS-Schnittstellen auftreten. Die LVDS-Schnittstelle benötigt mindestens 3 Signalpaare zur Datenübertragung, die da lauten: DCO (Data Clock Output), FCO (Frame Clock Output) und die Datenkanäle (D+A/D-A).

Jobangebote+ passend zum Thema

Ein relativ neuer Standard (im April 2006 wurde die erste Version des Standards veröffentlicht) ist JESD204B. Vom physikalischen Aufbau ist diese Schnittstelle vergleichbar mit LVDS, da auch hier ein Leitungspaar zur Datenübertragung genutzt wird. Die differenziellen Pegel sind etwas höher und liegen im Bereich zwischen 360 mV und 770 mV. Das führt pro Leitung zu einem höheren Strombedarf, was durch die Anzahl der benötigten Pins mehr als wettgemacht wird. Die Architektur ist basierend auf der CML (current mode logic).

Die wesentlichen Vorteile von JESD204B gegenüber LVDS liegen in den nächsten beiden Punkten, der hohen Datenrate von bis zu 12,5 Gbit/s je Kanal und der reduzierten Anzahl von Leitungen, da die oben erwähnten DCO- und FCO-Signale nicht benötigt werden. Dadurch reduzieren sich die Systemkosten, der Aufbau wird vereinfacht und gleichzeitig wird die Möglichkeit geboten, mehr Daten zu übertragen. Der Trend geht hier von einem System mit relativ geringer Geschwindigkeit und vielen Datenleitungen zum System mit hoher Geschwindigkeit und wenigen Leitungen. Auch von der FPGA-Seite wird diese Schnittstelle unterstützt, z.B. durch Xilinx (Virtex-6 und-7, Kintex-7, Artix-7, Zynq-7000) und Altera (Stratix V, Arria V, Cyclone V).

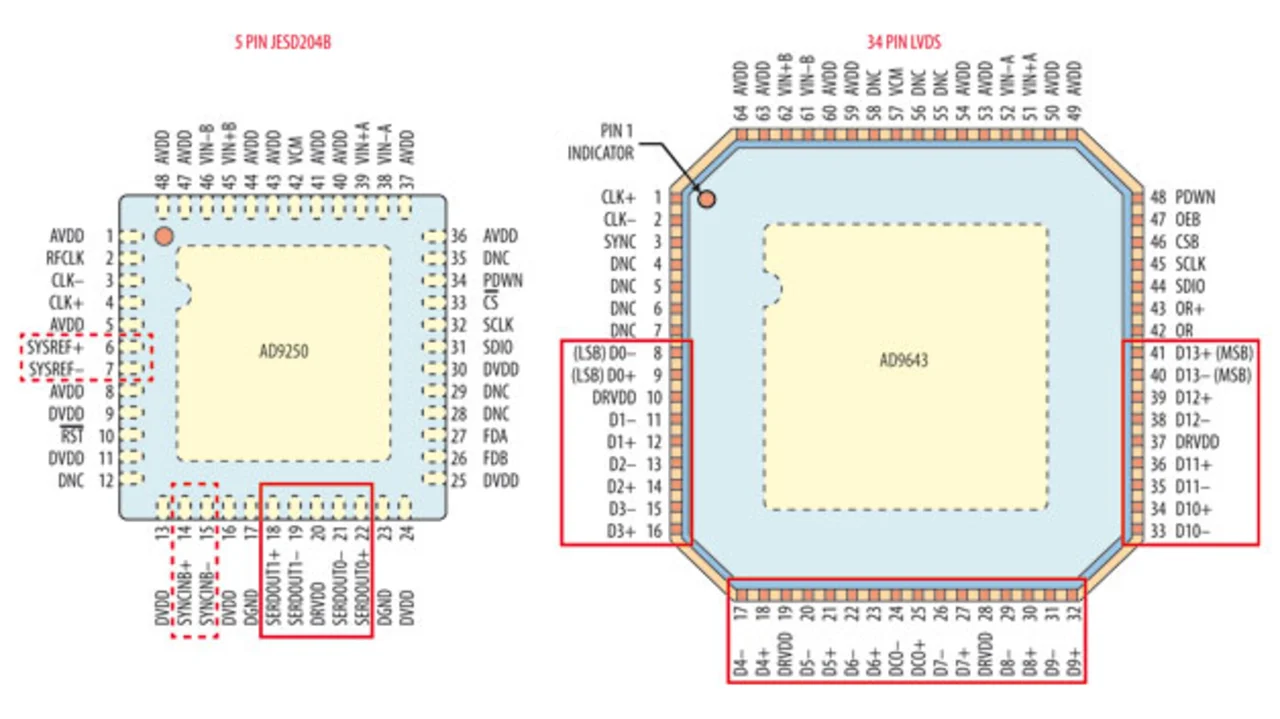

Einen Vergleich zwischen beiden Technologien zeigt Bild 4. Dort sind jeweils Zweikanal-A/D-Wandler mit 14 bit Auflösung und 250 MS/s zu sehen, der AD9250 mit JESD204B-Schnittstelle und der AD9643 mit LVDS-Schnittstelle.

Der Wandler mit der JESD204B-Schnittstelle benötigt mindestens fünf Anschlüsse für den Betrieb, wobei auch die Spannungsversorgung der Schnittstelle enthalten ist. Sollen mehrere Wandler synchronisiert werden, sind noch zwei Leitungspaare nötig, SYSREF und SYNCINB. Beim Wandler mit LVDS-Schittstelle sind mindestens 34 Anschlüsse nötig. Diese bestehen aus jeweils 14 Leitungspaaren, die die einzelnen Bits übertragen, vier Anschlüsse für die Spannungsversorgung sowie zwei Taktausgänge. Auch dieser Wandler kann synchronisiert werden, wofür ebenfalls zusätzliche Anschlüsse vorgesehen werden müssen.

- Beschaltung von schnellen Datenwandlern (Teil 2)

- Datenschnittstelle, LVDS und JESD204B

- Spannungsversorgung und Layout