PCB-Entwicklung/-Fertigung

Concurrent-Design schafft Wettbewerbsvorteile

Fortsetzung des Artikels von Teil 2

Power-Distribution-Netzwerk-Analysen

Auf ähnliche Weise wird die PDN-Analyse häufig komplett übersehen. Die Bedeutung niedriger AC-Impedanzen für High-Speed-Designs, die hohe Ströme in Verbindung mit niedrigen Core-Spannungen erfordern, kann nicht genügend betont werden. Ist die Impedanz bei der Grundfrequenz oder einer der ungeradzahligen Harmonischen hoch, sind höhere elektromagnetische Störabstrahlungen zu erwarten. Dies wiederum hat unmittelbare Auswirkungen auf die Zuverlässigkeit eines Produkts sowie auf seine Fähigkeit, die EMV-Prüfungen zu bestehen.

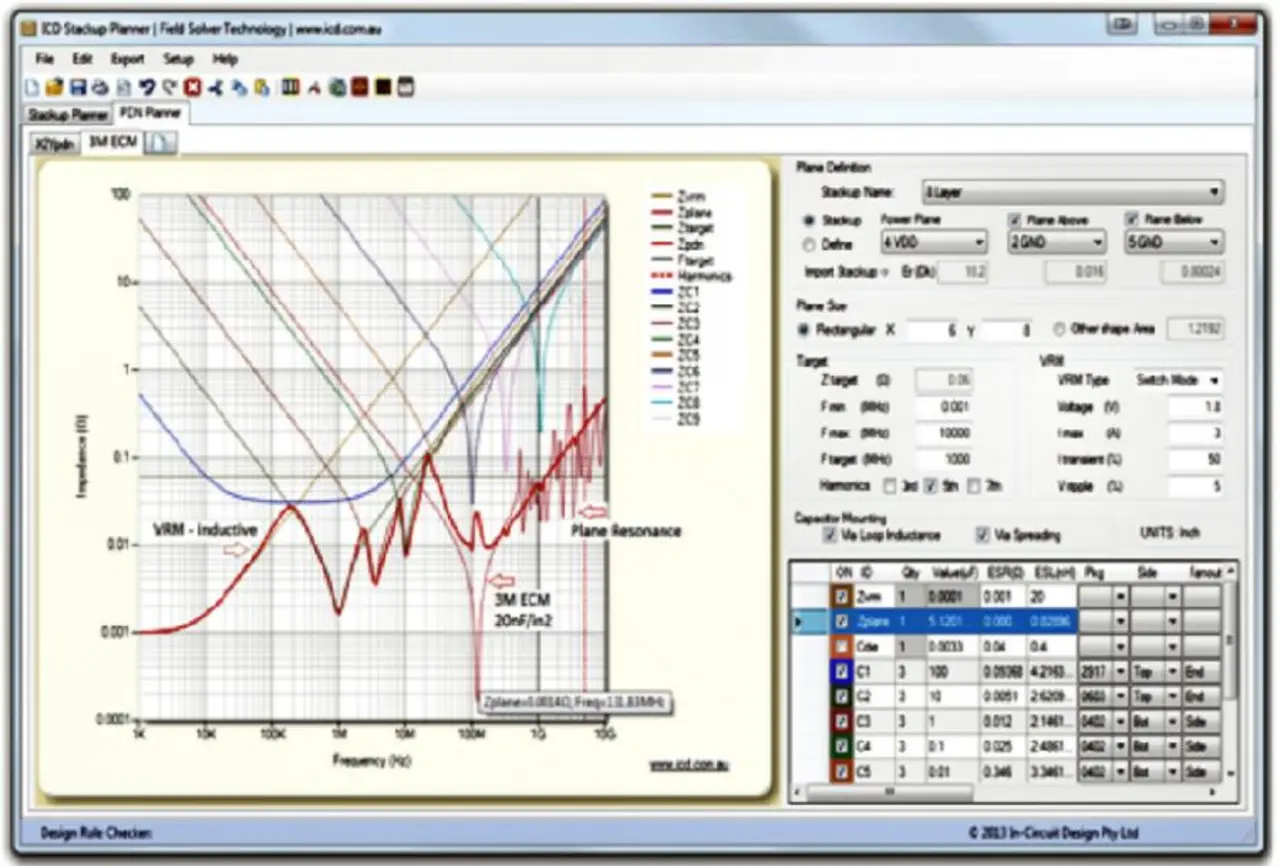

Jahrelang wurde in Applikationsschriften empfohlen, jeden Stromversorgungs-Anschluss mit drei Entkopplungskondensatoren zu versehen (meist ein 100-nF-, ein 10-nF- und ein 47-pF-Kondensator). Dahinter stand der Gedanke, dass die verschieden großen Kondensatoren bei verschiedenen Frequenzen Strom liefern – leider jedoch nicht bei den richtigen Frequenzen, denn jede Leiterplatte ist anders. Wie Bild 3 zeigt, sind mehrere Kondensatoren pro Dekade nötig, um die effektive Impedanz des PDN bis zur angestrebten Bandbreite unter dem Zielwert zu halten. Verwendet man zu wenige Kondensatoren, die außerdem zu weit über den Frequenzbereich verstreut sind, so ist die Wahrscheinlichkeit hoch, dass Antiresonanz-Spitzen im PDN das Problem sogar noch verschärfen.

Im vorliegenden Fall habe ich außerdem die Verwendung von 3M Embedded Capacitance Material (ECM) einbezogen, denn dies ist die einzige Möglichkeit, das PDN im Gigahertz-Bereich auf Low zu ziehen. Das Material schafft mit 20 nF pro Quadratzoll eine hervorragende Möglichkeit zur Ansammlung zusätzlicher planarer Kapazität. Die feste Anbindung zwischen ICD Stackup Planner und PDN Planner macht es möglich, die Auswirkungen anderer dielektrischer Werkstoffe automatisch zur Analyse an den PDN Planner zu übertragen.

Wiederverwendung von Designelementen

Soll in mehreren aufeinanderfolgenden Projekten der gleiche Schaltregler, der gleiche Prozessor mit dazugehöriger Peripherie oder identische Speicherchips verwendet werden, ist das Anlegen einer Bibliothek mit wiederverwendbaren Schaltungsblöcken für den Schaltplan und die Leiterplatte die beste Möglichkeit, vorhandene Designelemente in künftigen Projekten erneut zu nutzen. In den Schaltplan muss dann nur einfach ein fertiger Schaltungsblock hinzugefügt werden, und in der PCB-Datenbank wird ein vorgegebener Layout-Block mit der Platzierung der Bauelemente, den Leiterbahnen, Kupfer und Text geladen.

Es spielt keine Rolle, ob es um mehrkanalige Designs, kritische digitale Schaltungen, HF-Schaltungsblöcke oder das Kopieren eines häufig benötigten Layoutmusters geht – die Wiederverwendung von Designelementen spart in jedem Fall Zeit und bürgt für die Reproduzierbarkeit eines Designs, denn es steht eine bewährte, geprüfte und funktionsfähige Lösung zur Verfügung, die nur noch eingefügt werden muss.

Kooperatives Leiterplattendesign

Jahrelang schon versuchen sich Layouter im Teamdesign, um den scheinbar unvermeidbaren zeitlichen Engpass beim Entflechten der Leiterplatte zu entschärfen. In einem solchen Szenario arbeiten dann mehrere Leiterplattendesigner gleichzeitig an der Platzierung und am Routing in verschiedenen Bereichen einer Leiterplatte.

Gliederungsmöglichkeiten gibt es viele. Zum Beispiel lassen sich Schaltpläne und Layouts in verschiedene Funktionsbereiche unterteilen, wie etwa Stromversorgung, Analog, Digital oder Speicher. Auch können mehrere Layouter an verschiedenen Orten der Welt gleichzeitig an ein und demselben Abschnitt tätig sein. Ich selbst habe dies bereits mehrfach praktiziert und über Nacht Leistungen für Firmen in den USA erbracht. Das Konzept des Co-Designs impliziert, dass mehrere Layouter gleichzeitig an einem Design arbeiten können und dass ihr gesamter Design-Input akzeptiert wird. Hierbei ergeben sich jedoch viele Fallstricke, und beim Zusammenführen der Datenbestände muss irgendeine Art der Priorisierung erfolgen.

Einige EDA-Unternehmen haben in den letzten Jahren Tools entwickelt, mit denen Entwickler zusammenarbeiten und ihre Designs vergleichen und zusammenführen können. Unter anderem bieten diese Tools:

• Eine Möglichkeit für mehrere Entwickler, auf einen PCB-Datenbestand zuzugreifen und ihn zusammenzuführen

• Einen Mechanismus zum präzisen Identifizieren und Vergleichen von Datenbeständen

• Die Anzeige der Unterschiede, sodass die leitenden Entwickler bei etwaigen Konflikten fundiert entscheiden können, welches die beste Variante ist

Auch die Kollaboration in Echtzeit ist mittlerweile möglich. Jeder Entwickler definiert hierzu seinen Arbeitsbereich, welcher von den übrigen Layoutern bei geöffnetem Projekt klar zu erkennen ist. Dies grenzt die Arbeitsbereiche voneinander ab und verhindert Konflikte. Eine weitere Variante der Kollaboration ermöglicht es den Layoutern parallel zu arbeiten, ohne dass das Design in Bereiche aufgeteilt werden muss. Bei dieser Methode werden die von den einzelnen Anwendern vorgenommenen Änderungen durch ein Tool koordiniert und es werden fortlaufend Updates an das gesamte Team gesendet, sodass jeder einen aktuellen Stand des Layouts vor sich hat.

Diese Team-Kollaboration kann die Designzeit drastisch verkürzen, setzt aber auch ein hohes Maß an Disziplin innerhalb des Designteams voraus. Ein normalerweise 13 Wochen dauerndes komplexes Design lässt sich in einigen Fällen auf fünf Wochen verkürzen, was eine Produktivitätssteigerung um 60 % bedeutet.

Jobangebote+ passend zum Thema

- Concurrent-Design schafft Wettbewerbsvorteile

- Analysen vor dem Layout durchführen

- Power-Distribution-Netzwerk-Analysen

- Virtuelles Prototyping – Integration von ECAD und MCAD