PCB-Entwicklung/-Fertigung

Concurrent-Design schafft Wettbewerbsvorteile

Fortsetzung des Artikels von Teil 1

Analysen vor dem Layout durchführen

Die Pre-Layout-Analyse ermöglicht es Entwicklern, Probleme mit der Signalqualität, Übersprechen oder EMI schon in einer frühen Phase zu erkennen und zu beheben. Dies ist die effektivste Möglichkeit, eine Leiterplatte mit weniger Iterationen zu entwickeln, als wenn man Probleme nachträglich findet und eliminieren muss.

Die Pre-Layout-Analyse hat eine ganze Reihe von Facetten:

• Planung des Lagenaufbaus mit Blick auf kontrollierte Impedanz, Signalintegrität, Übersprechen und Kostenkontrolle

• Auswahl des Dielektrikum-Materials im Hinblick auf Fertigungsausbeute und Hochfrequenztauglichkeit

• PDN-Optimierung im Interesse der Produktzuverlässigkeit und der Kostensenkung

• Festlegung der I/O-Puffer und der Treiberstärke

• Topologie-Optimierung

• Terminierungs-Strategie

• Floorplanning für kritische Bauelemente

• Herleitung der Routing-Restriktionen einschließlich Breiten, Abstände und Längenanpassung der Leiterbahnen

• Signalintegritäts-Analyse zur Einhaltung der Design-Spezifikationen in Bezug auf Timing, Skew, Über- und Nebensprechen sowie Signalverzerrung

Obwohl normalerweise eine gewünschte Zielimpedanz mit dem Leiterplattenhersteller abgesprochen wird, erfolgt die Planung des physikalischen Lagenaufbaus häufig erst dann, wenn die Produktionsdaten an den Hersteller der unbestückten Leiterplatte geliefert werden. In aller Regel ergeben aber die Kombination aus dem vom Hersteller favorisierten Dielektrikum-Material und die vom Layouter verwendeten Breite und Abstände der Leiterbahnen nicht die angestrebte kontrollierte Impedanz. Der Layouter erhält in diesem Falle von CAM-Spezialist Berechnungen, die Änderungen an der Breite und den Abständen der Leiterbahnen und somit ein komplettes Re-Routing erfordern können. Dies ist sicher das Letzte, was man sich am Ende eines Designzyklus wünscht. Als Ursache dieses unbefriedigenden Ablaufs lässt sich die Tatsache ausmachen, dass die Leiterplatten-Designer kein auf einem Field Solver basierenden Planungswerkzeug für den physikalischen Lagenaufbau haben und deshalb warten müssen, bis entweder ein SI-Ingenieur das Design analysiert oder – was häufiger der Fall ist – die Berechnungen des Hersteller eintreffen.

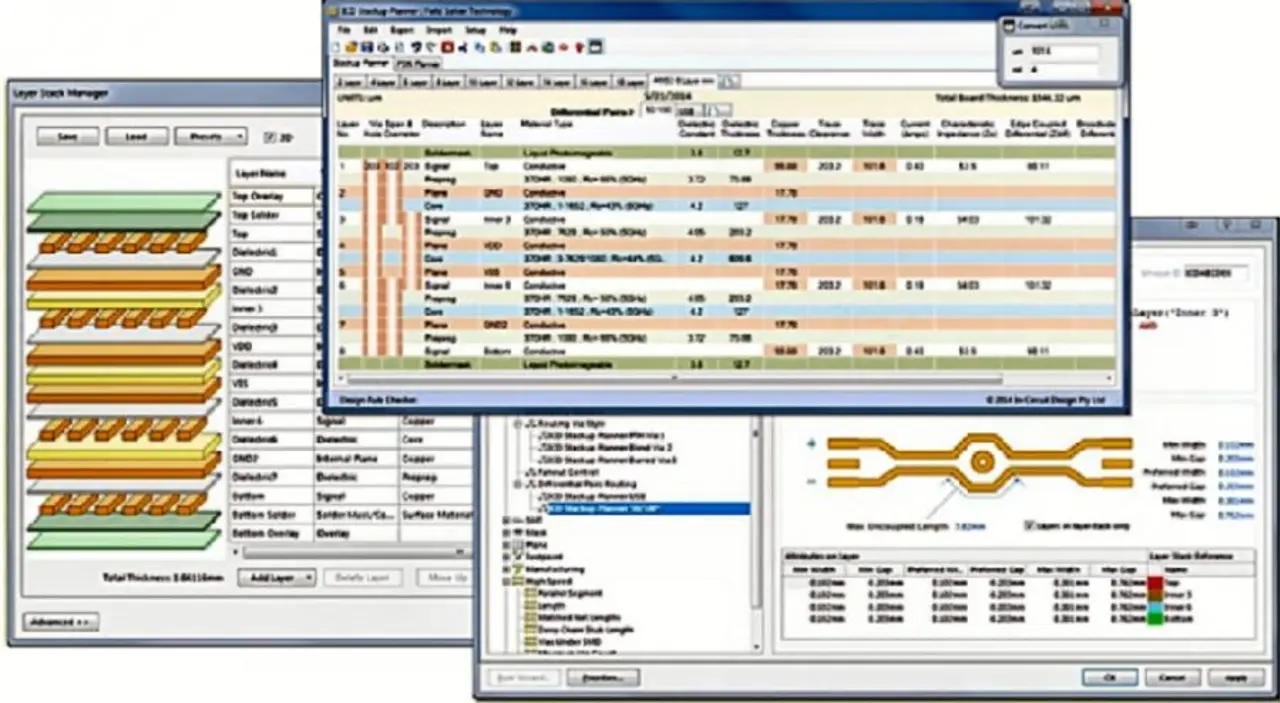

ICD hat auf diese Situation reagiert und eine bidirektionale Schnittstelle zwischen dem ICD Stackup Planner und Altium Designer entwickelt. Dieses neue Interface macht es gar möglich, den Rigid/Flex-Lagenaufbau aus dem Altium Layer Stack Manager in den Stackup Planner zu übernehmen. Zur Impedanz Berechnung stehen über 8.800 dielektrische Materialien inklusive High-Speed-taugliche Werkstoffe für bis zu 40 GHz zur Verfügung. Außerdem können mehrere differenzielle Leiterpaare mit unterschiedlichen Zielimpedanzen auf ein und demselben Substrat berechnet werden.

Nach Abschluss der Arbeiten exportiert der Entwickler die Ergebnisse inklusive Regeln für Blind-/Buried Microvias, Breiten und Abstände für Leiterbahnen und differenzielle Leiterpaare wieder zurück zum Altium Designer. Hier muss dann nur eine Zuweisung der Regeln zu Netzen oder Netzklassen vorgenommen werden. Exportiert wird zusätzlich eine Fertigungszeichnung mit dem Lagenaufbau und weiteren Berechnungsergebnissen nach Excel.

Jobangebote+ passend zum Thema

- Concurrent-Design schafft Wettbewerbsvorteile

- Analysen vor dem Layout durchführen

- Power-Distribution-Netzwerk-Analysen

- Virtuelles Prototyping – Integration von ECAD und MCAD