FED-Auszeichnung

Zollner gewinnt PCB Design Award für Supercomputing-Hardware

Zollner Elektronik wurde vom Fachverband Elektronik Design und Fertigung (FED) bei der diesjährigen Konferenz mit dem PCB Design Award 2024 ausgezeichnet. Diesen hat zum siebten Mal der FED gestiftet. Der Preis würdigt alle zwei Jahre Baugruppendesigner für exzellente Arbeiten.

Seit mehreren Jahren beschäftigt sich die PCB Design Gruppe bei Zollner Elektronik u.a. mit Designaufgaben im High Speed / High Density Bereich.

Marktfähigkeit stand im Vordergrund

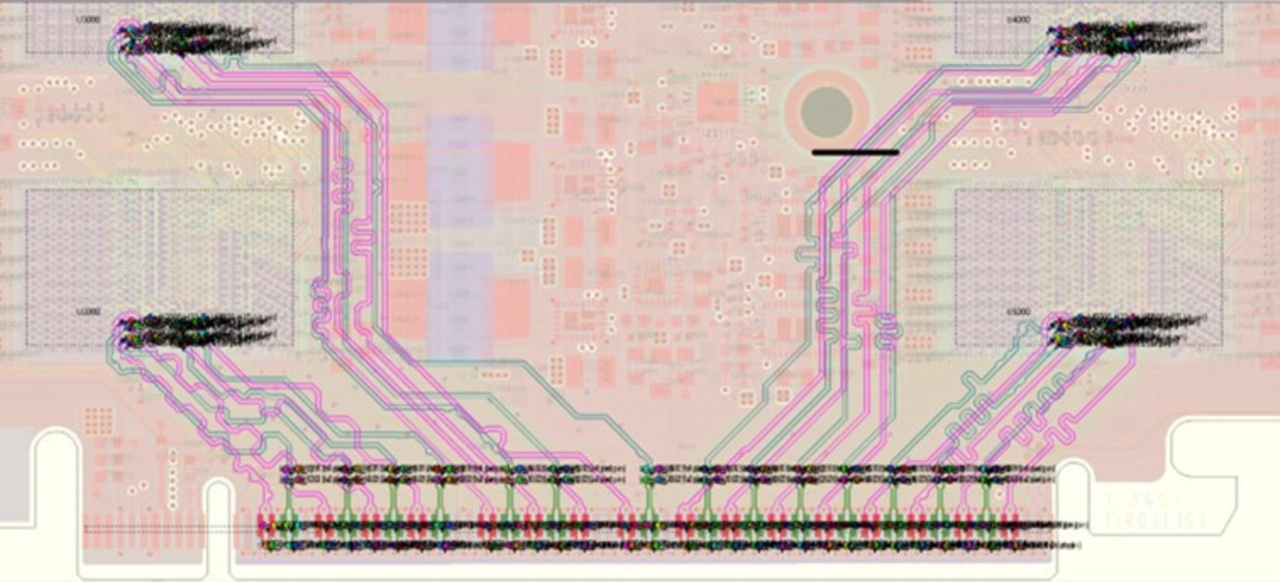

Im Rahmen eines Projektes des Bundesministeriums für Bildung und Forschung (BMBF) entstand eine PCIe Add On Card für STX-Beschleuniger-Chiplets, die in Rechenzentren zur Wetter- und Klimasimulation sowie im Bereich neuronaler Netze und maschinellem Lernen eingesetzt wird. Aufgrund der geplanten Serienproduktion stand bereits beim Demonstrator neben der Funktionalität auch die Marktfähigkeit im Vordergrund, wobei der gesamte Umfang des Research & Development Leistungsportfolios genutzt wurden.

Doppelte Rechenleistung pro Serverrack bei weniger Anschlussleistung

Neben der Hardware wurde auch die Software für die Steuerung, Diagnose und das Power-Management erstellt. Herausforderungen waren die hohen Schaltgeschwindigkeiten von PCIe 5.0 (32GT/s) und die stabile Energieversorgung mit einem Point-of-Load Konzept, das 21 teilweise getrennte Stromversorgungen umfasst. Die Baugruppe erzeugt eine maximale Verlustleistung von 225W, die luftgekühlt abgeführt wird. Durch energiesparende Maßnahmen und Halbierung der Bauhöhe konnte die doppelte Anzahl an Baugruppen in einem 19" Einschub untergebracht und somit die doppelte Rechenleistung pro Serverrack bei weniger Anschlussleistung erzielt werden.

Gemeinsam mit den Projektpartnern entstand eine Anforderungsspezifikation, die Systemarchitektur sowie die HW- und SW-Anforderungen unter Berücksichtigung aller relevanter Normen. Die Schaltungsteile wurden mithilfe von Simulationen dimensioniert, der Schaltplan abgeleitet, und der Layer Stackup in Zusammenarbeit mit den Leiterplattenherstellern definiert.

High Speed Lagenübergänge

Parallel zur Bauteilplatzierung wurden Thermosimulationen und die Kühlkörperauslegung begonnen. Im PCB-Design lag der Fokus auf den High Speed Lagenübergängen, begleitet von elektrischen Simulationen zur Signalintegrität und Power Integrity. Die Bauteilplatzierung berücksichtigte von Beginn an die Produktionsanforderungen (Design for Excellence).

Enge Zusammenarbeit entlang der Design Chain sowie die Einbindung von Vorlieferanten und der Baugruppenproduktion sicherten hohe Zuverlässigkeit, Leistungsfähigkeit und wirtschaftliche Fertigbarkeit.