Optimiert ist nicht immer optimal

Automatisierung des Entwurfs analoger ICs – Teil 2

Angesichts der Herausforderungen beim Design analoger und hybrider ICs wurden zwei neuartige Entwurfsverfahren – EDP und SWARM – an der Hochschule Reutlingen entwickelt. Sie erlauben eine signifikante Steigerung der Entwurfsproduktivität.

Ausgehend von den in Teil 1 [3] erläuterten Beobachtungen und Erkenntnissen verfolgen die Forscher an der Hochschule Reutlingen die Idee, die Entwurfsautomatisierung analoger Schaltungen nicht mittels Optimierern anzugehen, sondern indem sie Wege erforschen, wie das erfahrungsbasierte Vorgehen der Schaltungs- und IC-Layoutentwickler mit Automatismen imitiert werden kann. Einen Ansatz hierfür bieten prozedurale Verfahren, die in der EDA (Electronic Design Automation) auch als Generatoren bekannt sind.

Zwei Entwurfsverfahren, die auf diesem Paradigma der prozeduralen Automatisierung beruhen, sind:

- Expert Design Plan (EDP) zum automatischen Entwurf analoger integrierter Schaltungen und

- Self-organized Wiring and Arrangement of Responsive Modules (SWARM) zur automatischen Layouterzeugung analoger integrierter Schaltungsmodule.

Jobangebote+ passend zum Thema

Schaltungsentwurf mit Expert Design Plan

Bei der Entwicklung analoger integrieter Schaltungen führt ein Schaltungsentwickler im Wesentlichen folgende Einzelschritte durch:

- Erstellung / Veränderung der Schaltungsstruktur

- Dimensionierung der Bauteile (initiale Werte zumeist über Handrechnungen)

- Erstellung / Veränderung einer Simulationsanordnung (Testbench)

- Durchführung von Simulationen zur Überprüfung von Schaltungsfunktionen

Diese Schritte werden im Allgemeinen solange iterativ wiederholt, bis spezifizierte Eigenschaften, sog. Leistungsparameter, z.B. die Verstärkung eines Transkonduktanzverstärkers und evtl. weitere gewünschte Eigenschaften einer Schaltung, erreicht sind.

Ein Expert Design Plan (EDP) ist ein parametrierbares Skript, das diese Schritte, und damit die Vorgehensweise eines menschlichen Schaltungsentwicklers, abbildet. Neben Kommandos, die oben genannte Handlungen umsetzen, gehören hierzu auch die aus Programmiersprachen bekannten Kommandos zur Steuerung des Programmablaufs – z.B. Schleifen, Verzweigungen –, um die Entwurfsstrategie in Abhängigkeit von Zwischenergebnissen codieren zu können. Ein EDP ist typischerweise für den Schaltungsentwurf eines Schaltungstyps ausgelegt, z.B. Bandgap, OTA (Operational Transconductance Amplifier), ADU. Dabei können unterschiedliche Leistungsparameter, Halbleitertechniken und Schaltungen abgedeckt werden.

Gerade bei sicherheitskritischen Systemen, wie z.B. in der Automobilelektronik, wird zumeist auf bewährte, sogenannte »silicon-proven« Entwürfe zurückgegriffen, die lediglich auf neue Anforderungen adaptiert werden. Die Vorgehensweise in der Schaltungsdimensionierung wird dabei aus der bewährten Praxis übernommen. Die EDP-Methodik unterstützt diese Vorgehensweise.

Da ein EDP den Entwurfsablauf nicht nur automatisiert, sondern auch dokumentiert, ergibt sich die Chance, den arbeitsintensiven Dokumentationsaufwand zu reduzieren. Dies kann z.B. die Umsetzung der ISO 26262 wirksam unterstützen oder auch zum Wissenstransfer innerhalb des Entwicklerteams beitragen.

Zum Ausführen im EDA-Tool: EDP-Player

Damit ein EDP ausführbar ist, bedarf es einer Einbindung in ein industrielles Entwurfswerkzeug. Ein Ansatz hierzu ist die Erstellung einer Funktionsbibliothek in einer Skriptsprache, die innerhalb der Entwurfsumgebung ausführbar ist. Eine solche Funktionsbibliothek nennen die Forscher an der Hochschule Reutlingen einen EDP-Player: »Wir haben einen EDP-Player für die im Industrieumfeld überwiegend verwendete Entwicklungsumgebung für ICs, Virtuoso der EDA-Firma Cadence, entwickelt. Er ist in der Programmiersprache Cadence SKILL realisiert.« Dieses Werkzeug stellt derzeit einen Basissatz von Befehlen zur Schaltungsdimensionierung zur Verfügung. Der Befehlsumfang ist zum jetzigen Zeitpunkt noch nicht vollständig, es fehlen zum Teil noch Befehle zur Anpassung der Schaltungsstruktur.

EDP-Language und EDP-Recorder

Expertenwissen kann nur von Experten kommen. Die erfolgreiche Anwendung der EDP-Methodik hängt daher entscheidend davon ab, inwieweit es gelingt, echtes Expertenwissen in die EDPs zu integrieren. Damit das Erzeugen eines EDP für Schaltungsentwickler möglichst einfach und intuitiv ist, wird an der Hochschule Reutlingen hierfür derzeit eine spezifische Sprache, die EDP-Language (EDPL), entwickelt. Das Ziel hierbei ist, die Syntax und Semantik der einzelnen Kommandos so eng wie möglich an die Denk- und Arbeitsweise von Schaltungsentwicklern anzupassen, damit das Expertenwissen, das durchaus auch von Intuition geprägt ist, möglichst genuin, d.h. unverfälscht erfasst werden kann. Dies halten die Beteiligten für den wichtigsten Aspekt ihres Ansatzes. Darüber hinaus kann auch nur dann erwartet werden, dass die Methode in der Praxis Anklang findet.

Weiter heißt es: »In einem weiteren Schritt wollen wir an der Hochschule Reutlingen dann daran arbeiten, dass EDPs sogar ohne das aktive Schreiben von Code erzeugt werden können, indem EDPs auch automatisch während der gewohnten Entwurfsarbeit im Hintergrund mitgeschrieben werden – vergleichbar einem Log-File. Eine solche Funktion nennen wir EDP-Recorder.« Neue EDPs lassen sich auf diese Weise durch Ändern eines von einem EDP-Recorder erfassten Codes erzeugen.

Erste Anwendungen erreichen hohe Entwurfsproduktivität

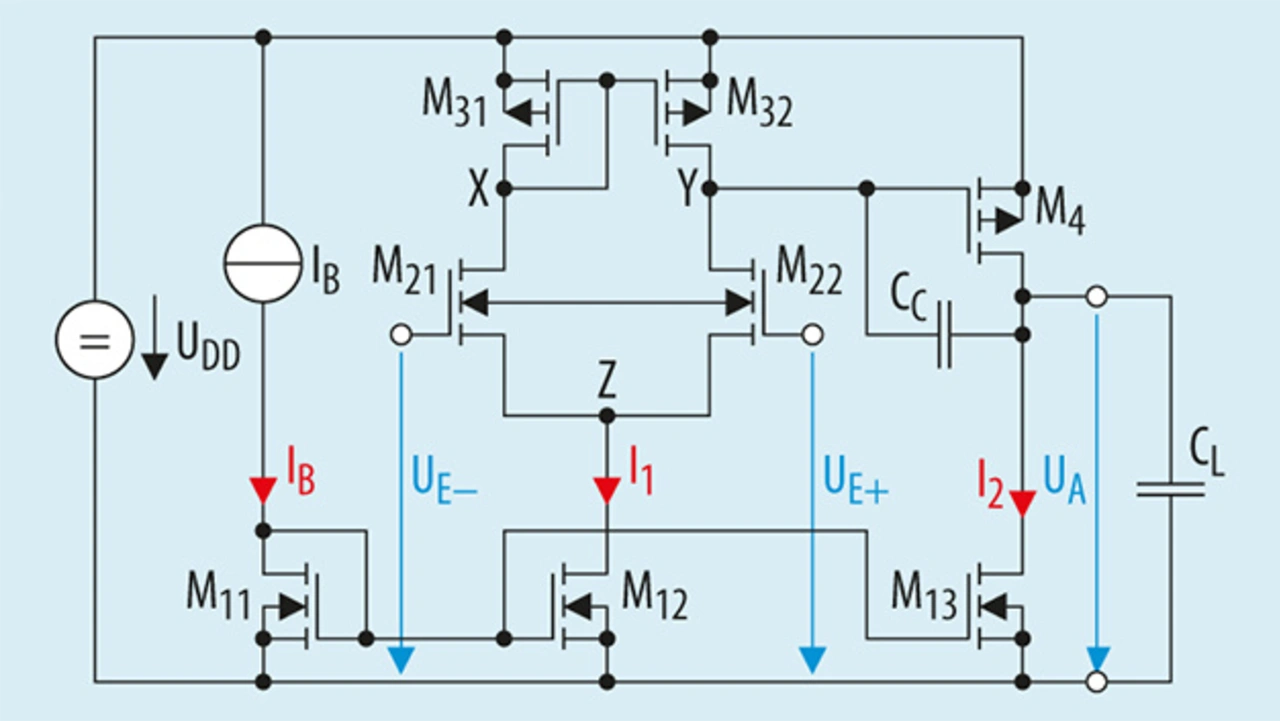

Die EDP-Methodik wurde erstmals exemplarisch an einer einfachen Source-Schaltung erprobt [4]. Mittlerweile hat die Hochschule Reutlingen EDPs für mehrere Schaltungstypen erfolgreich umgesetzt. Ein demonstratives Beispiel ist der Miller-Operationsverstärker (Bild 5), der zu den bekannten Operationsverstärkerschaltungen gehört. Mithilfe eines EDP, bestehend aus 99 Befehlen, wurde die Dimensionierung dieser Schaltung hinsichtlich sieben Leistungsparametern wie z.B. Phasenrand oder Verstärkung komplett automatisiert. Dabei wird ein breites Spektrum von Parameterwerten abgedeckt. Die Ausführung des EDP benötigt zwischen 15 und 29 Minuten auf einem üblichen Arbeitsplatzrechner und liefert stets ein korrektes Ergebnis.

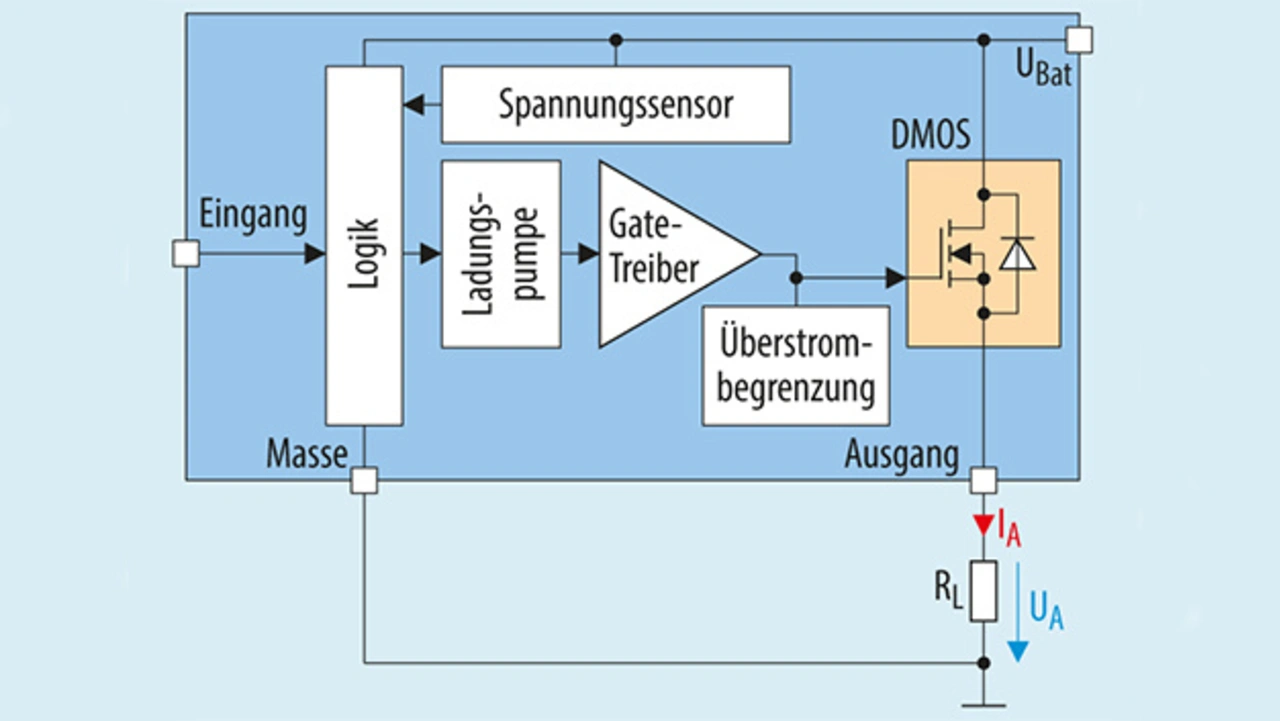

Jedoch können nicht nur einfache Funktionsblöcke per EDP dimensioniert werden. Auch weit größere Schaltungen sind möglich. In Zusammenarbeit mit Infineon Technologies wurde innerhalb eines BMBF-finanzierten Forschungsprojektes an der Hochschule Reutlingen die EDP-Methode erfolgreich auf ein industrielles Entwurfsproblem angewendet. Es handelt sich um einen vom Anwender konfigurierbaren Smart-Power-IC (High-Side Switch) der Infineon PROFET-Serie, bestehend aus DMOS-Leistungstransistor und Ansteuerschaltung (Bild 6). Dieser IC wird in Kraftfahrzeugen anstatt von Relais zum Schalten von Verbrauchern wie z.B. Scheinwerfern genutzt.

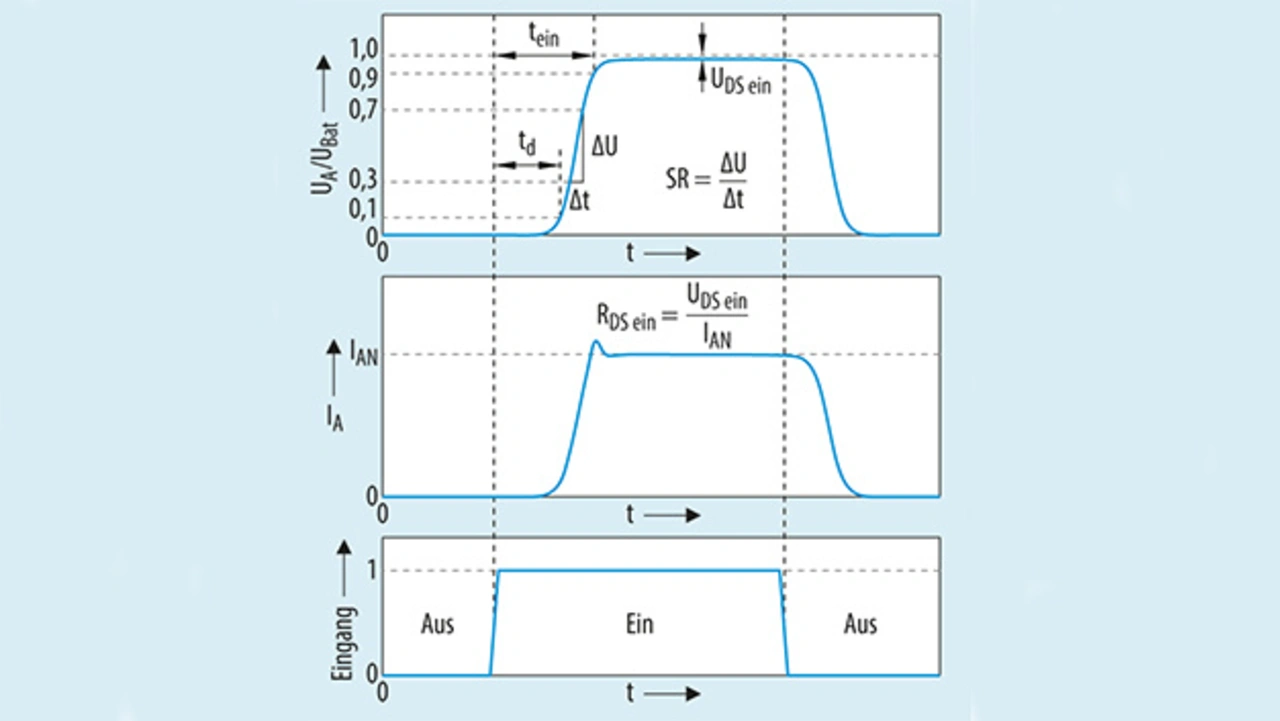

Der IC enthält verschiedene Sicherheits- und Diagnosefunktionen, die z.B. im Falle eines Kurzschlusses im Verbraucher diesen vom Bordnetz trennen und den Fehler an die Steuerelektronik melden. Die elektrischen Verluste des Schalters hängen vom Kanalwiderstand RDS ein des darin enthaltenen DMOS-FETs ab und müssen je nach Verbraucher anders gewählt werden. Das übrige Verhalten des IC, gekennzeichnet z.B. durch die Anstiegsgeschwindigkeit (SR, Slew Rate) und den maximalen Ausgangsstrom (Bild 7), soll davon jedoch unbeeinflusst bleiben.

Zur Automatisierung unterschiedlicher Entwurfsaufgaben, die bei der Anpassung des Smart-Power-IC an einen Verbraucher nötig sind, wurden insgesamt sieben verschiedene EDPs entworfen, bestehend aus zwei bis 27 EDP-Befehlen. Diese decken nicht nur den oben beschriebenen Anwendungsfall ab, sondern können auch zur Anpassung weiterer Kenngrößen des ICs genutzt werden.

Es zeigte sich, dass die Verwendung dieser EDPs stets zu korrekten und verlässlichen Ergebnissen führt. Die Ausführungszeit dieser EDPs beträgt zwischen 6 und 53 Minuten. Im Vergleich zur händischen Dimensionierung, die im Bereich von ein bis zwei Arbeitstagen liegt, ergibt sich eine Steigerung der Entwurfsproduktivität um deutlich mehr als eine Größenordnung.

Der Initialaufwand zur Erstellung der EDPs betrug etwa drei Tage, sodass sich eine Amortisation bereits bei etwa zwei Anwendungen ergibt. Mit Verwendung der heute noch nicht verfügbaren Elemente EDPL und EDP-Recorder lässt sich dieser Wert nochmals verbessern. Aus diesem Beispiel wird bereits das große Potenzial des EDP-Ansatzes ersichtlich.

Lösungsansatz für den Entwurf: Selbstorganisierendes Layout

Im Layoutentwurf analoger ICs haben sich Generatoren längst als unerlässliche Automatismen etabliert, um die physikalische Auslegung grundlegender Schaltungselemente, z.B. Transistoren und Widerstände, über einen kontinuierlichen Variantenbereich hinweg parametergesteuert zu generieren.

Deutlich anspruchsvoller ist die Aufgabe, diese Bauteile dann für eine spezifische Schaltung kompakt anzuordnen und miteinander zu verbinden, denn dies erfordert die Berücksichtigung einer Vielzahl diverser – oftmals gegenläufiger – Randbedingungen und Optimierungsziele. Randbedingungen sind harte Anforderungen, wie z.B. strikte Überlappungsfreiheit, Optimierungsziele dagegen sind graduelle Qualitätskriterien, wie z.B. ein möglichst geringer Abstand bestimmter Bauteile [5].

Die Verfügbarkeit immer besserer EDA-Werkzeuge wie dem PCell Designer von Cadence [6] ermöglicht heute die wirtschaftliche Umsetzung von Layoutgeneratoren, die diese Aufgabe für kleine Grundschaltungen (Module) übernehmen, insbesondere wenn das zu erzeugende Layout einer stark regelmäßigen Anordnung gleicher Bauteile folgen soll – z.B. matrixartig. Bei den typischerweise unregelmäßigen Strukturen komplexerer Analogschaltungen stoßen Generatoren aber recht schnell an die Grenze, was sich an parametrischer Variabilität »vorausdenken« lässt. Hierfür wären prinzipiell klassische Optimierer geeignet – allerdings unter der Voraussetzung, dass Modulgeneratoren mit ihrer »Basisarbeit« bottom-up ein solides Fundament für die top-down arbeitenden Optimierer schaffen.

Da Generatoren und Algorithmen in dieser Hinsicht komplementär sind, sind sie auf der anderen Seite auch inkompatibel. An der Hochschule Reutlingen hat man sich daher die Frage gestellt, wie zwei derart konträre Automatisierungsstrategien in Einklang zu bringen sind, und eine Lösung gefunden.

- Automatisierung des Entwurfs analoger ICs – Teil 2

- Die Natur als Vorbild