Halbleitertechnologie

Foundry-Leistungen und Back-End-Prozessablauf für Automobilanwendungen

Ein Wafer-Fertigungsprozess für die Automobilindustrie muss ein heraus-ragendes Qualitäts- und Zuverlässigkeitsniveau erreichen. So sind für Produktionsprozesse Kundenfehlerraten (Field Failure Rates) von weniger als 0,1 ppm (parts per million) spezifiziert. Um Mikro-Chips auf diesem Anforderungs-Niveau zu fertigen, sind deshalb Defektdichten von weniger als 0,1 D/cm² erforderlich.

Wie sieht ein derartiger Prozess für Automotive-Produkte aus, wenn er darauf ausgelegt ist, parallel zu Prozessen für industrielle oder Konsumelektronikanwendungen zu laufen? Die wichtigsten fünf Teilbereiche werden nachfolgend beschrieben.

Wafer-Fabriken (Fabs) mit Wafer- Produktion sowohl für Automotive als auch für industrielle oder Konsumelektronikanwendungen können bestimmte Produktionsanlagen für Prozesse mit höheren Qualitätsstandards reservieren; hier besteht jedoch das Risiko einer verringerten Flexibilität, sobald der Produktionsprozess die volle Kapazitätsauslastung erreicht hat. Die bessere Lösung ist es daher, Fabs durchgängig mit Anlagen auf Automotive-Qualitäts- Niveau auszurüsten.

Generell sollte ein Defect Engineering, d.h. die kontrollierte Einflussnahme auf prozessbezogene Defekte, durchgeführt werden. Für bestimmte Schlüsselschritte innerhalb des Prozesses ist dabei der Einsatz eines optischen Systems zur Erkennung und Klassifizierung von Defekten notwendig. Falls Defekte auf der Wafer-Oberfläche festgestellt werden, ist eine Reinigung mit Hilfe von Spezialanlagen wie Scrub-Reinigern möglich, eine Nacharbeitung harter Schichten ist jedoch im Allgemeinen nicht erlaubt. Die Nacharbeitung weicher Schichten wie Fotolack kann in gewissen Fällen zugelassen werden.

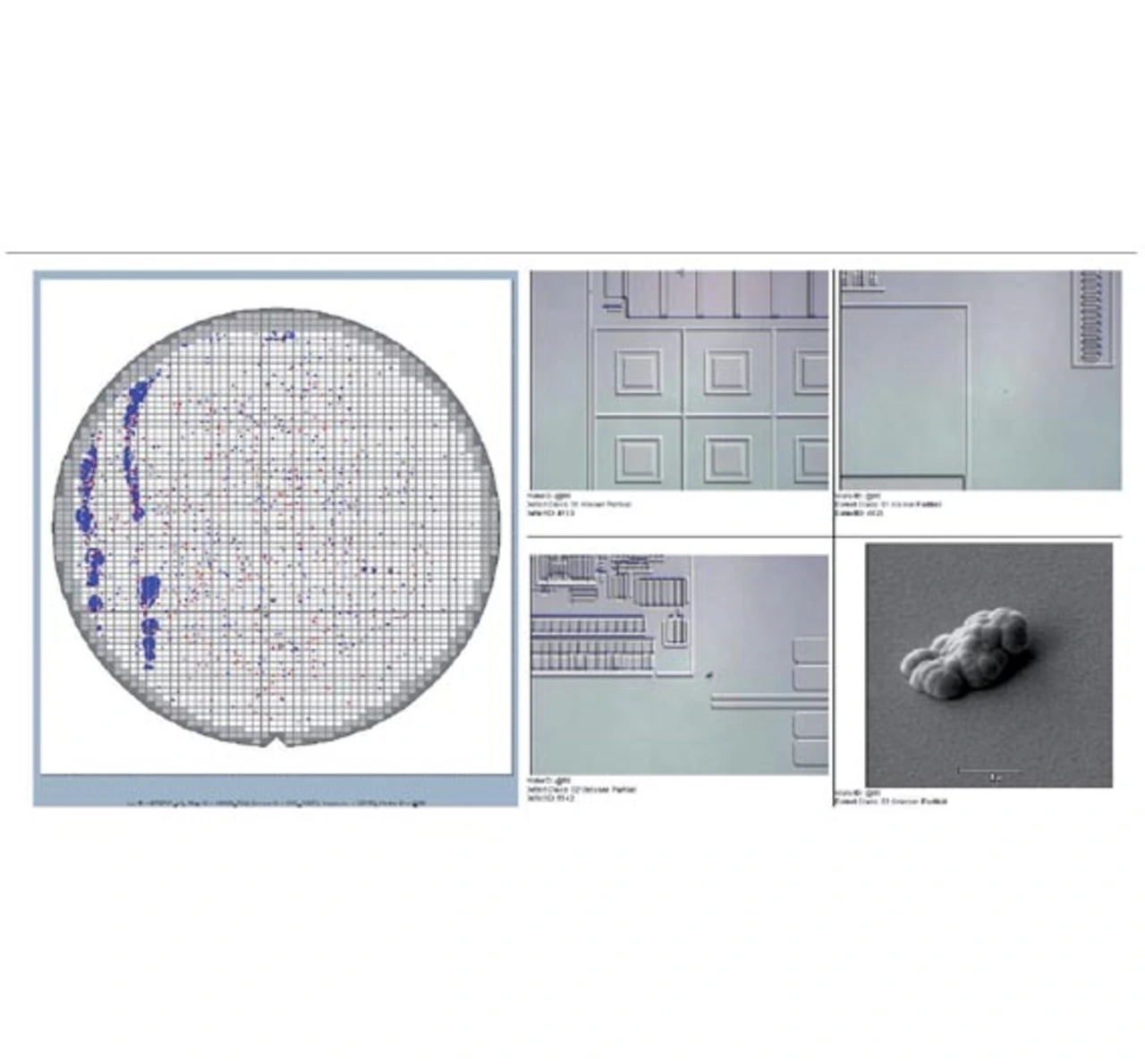

Bild 1 zeigt die elektronischen Ausgabewerte eines Werkzeugs zur Defektmessung. Solche graphischen Daten werden als vorab bereitgestellte Information für den Wafer-Handler direkt mit den elektrischen Wafer- Test-Stationen verknüpft. Die Implementierung von Wafer-Testverfahren auf Basis von Wafer-Karten wird als „Geographic Part Average Testing“ (GPAT; geografischer Teiledurchschnittstest) bezeichnet. Wird beispielsweise im Rahmen des Defektmessprozesses ein Kratzer auf einem Silizium-Wafer festgestellt, ist es nicht ausreichend, nur diejenigen Schaltkreise zu identifizieren, die von dem Kratzer direkt betroffen sind. Schaltkreise in der Nachbarschaft des Kratzers können ebenso Zuverlässigkeitsprobleme aufweisen. Daher definiert das GPAT-Verfahren eine Schutzzone um solche Defekte herum.

Am Ende des Wafer-Fertigungsprozesses wird ein elektrischer Wafer- Akzeptanztest (WAT) durch Prüfung spezieller Teststrukturen durchgeführt, die sich üblicherweise innerhalb der Sägestraßen des Wafers befinden. Normalerweise existieren zwei Kategorien von WAT-Parametern: „Pass/Fail“ und „Info“. Für Anwendungen im Automotive-Bereich sollten weitere Kategorien wie „Performance“ und „Reliability“ definiert werden.

Diese speziellen Kategorien können unterschiedliche Akzeptanzkriterien haben. So kann zum Beispiel der Zuverlässigkeitsparameter in WAT-Tests ein Akzeptanzkriterium von „fünf von fünf Mess-Stellen“ haben, während die anderen Parameter auf dem branchen-üblichen Standard-Niveau von „drei von fünf Mess-Stellen“ verbleiben. Im Falle des Nichtbestehens des Tests können spezielle Verfahren wie „100 % WAT“ angewendet werden, was bedeutet, dass jede Teststrukturauf jedem Wafer eines verdächtigen Loses gemessen werden muss.

Bevor ein Los freigegeben wird, ist es in jedem Fall notwendig, eine automatische optische Inspektion (AOI) jedes Quadratmikrometers für alle Wafer durchzuführen.

- Foundry-Leistungen und Back-End-Prozessablauf für Automobilanwendungen

- Wafer-Test senkt Unzuverlässigkeitsrisiko

- Packaging mit speziellen Anforderungen

- End-Test für Automotive-Produkte

- Sicheres Produkteinführungskonzept für Automotive