Mikrocontroller

40-nm-Flash-Technologie für Automotive

Fortsetzung des Artikels von Teil 3

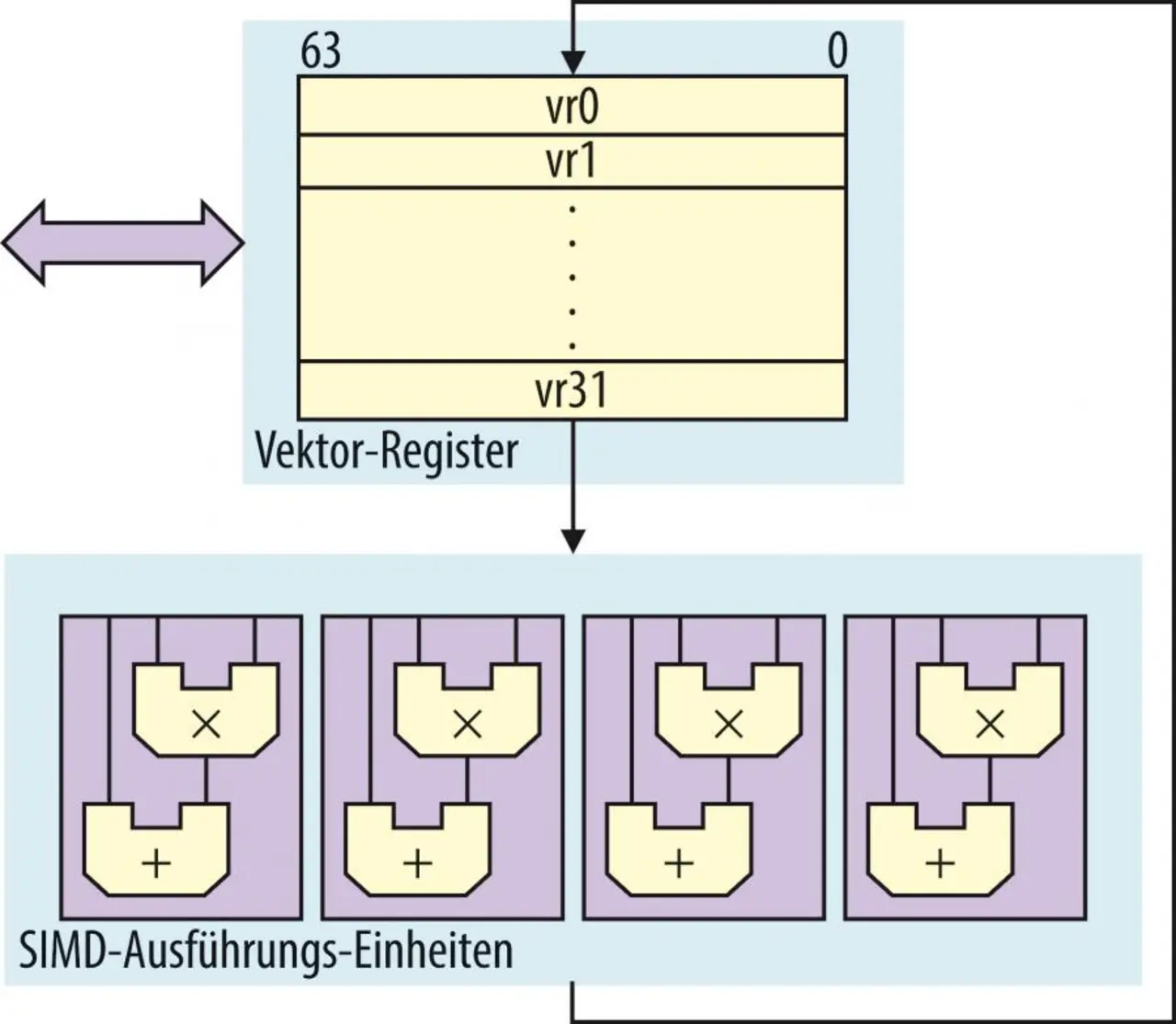

SIMD-Architektur

SIMD steht für Single Instruction Multiple Data, also die Verarbeitung mehrerer Operanden mit einem Befehl. Damit eignet sich diese Einheit insbesondere für die digitale Signalverarbeitung, die in der Regel einfache Grundoperationen wie Multiplizieren und Aufaddieren benötigt, diese aber sehr häufig und schnell ausführen muss. Wie das vereinfachte Blockdiagramm in Bild 2 zeigt, hat die SIMD-Einheit Zugriff auf 32 eigene und nicht anderweitig verwendete 64‑bit-Vektorregister. Sie bearbeitet mit einem Befehl 64 bit breite Vektoren, die in zwei 32‑bit- oder vier 16‑bit-Daten aufgeteilt sind.

Die SIMD-Einheit hat vollen Zugriff auf den Datenbus der CPU und kann daher eigenständig ihre Register aus dem Speicher lesen und die Ergebnisse dorthin zurückschreiben. Dazu wurden Adressierungsarten implementiert, die bei Filterberechnungen von großem Vorteil sind, nämlich die Modulo-Adressierung und das automatische Adress-Inkrementieren. Darüber hinaus wird die Bit-Reverse-Adressierung unterstützt, die bei der schnellen Fourier-Transformation (FFT) benötigt wird. Neben 16-bit-, 32-bit- und 64-bit-Integer unterstützt die SIMD-Einheit auch Festkommazahlen.

Der Befehlssatz der SIMD-Einheit lässt sich grob in die folgenden Kategorien einteilen:

- Logische Operationen und Verschiebeoperationen

- Datenoperationen, zum Beispiel Lesen, Schreiben, Vertauschen oder Typenumwandlungen

- Vergleiche, Suchen von Maximum und Minimum

- Arithmetische Operationen wie Addition, Multiplikation reeller und komplexer Zahlen, Multiplikation und Addition mit und ohne Sättigung oder Rundung für reelle Zahlen und für den Real- sowie den Imaginärteil komplexer Zahlen, Biquad-Operation für IIR-Filter, Negierung, Absolutwertbestimmung.

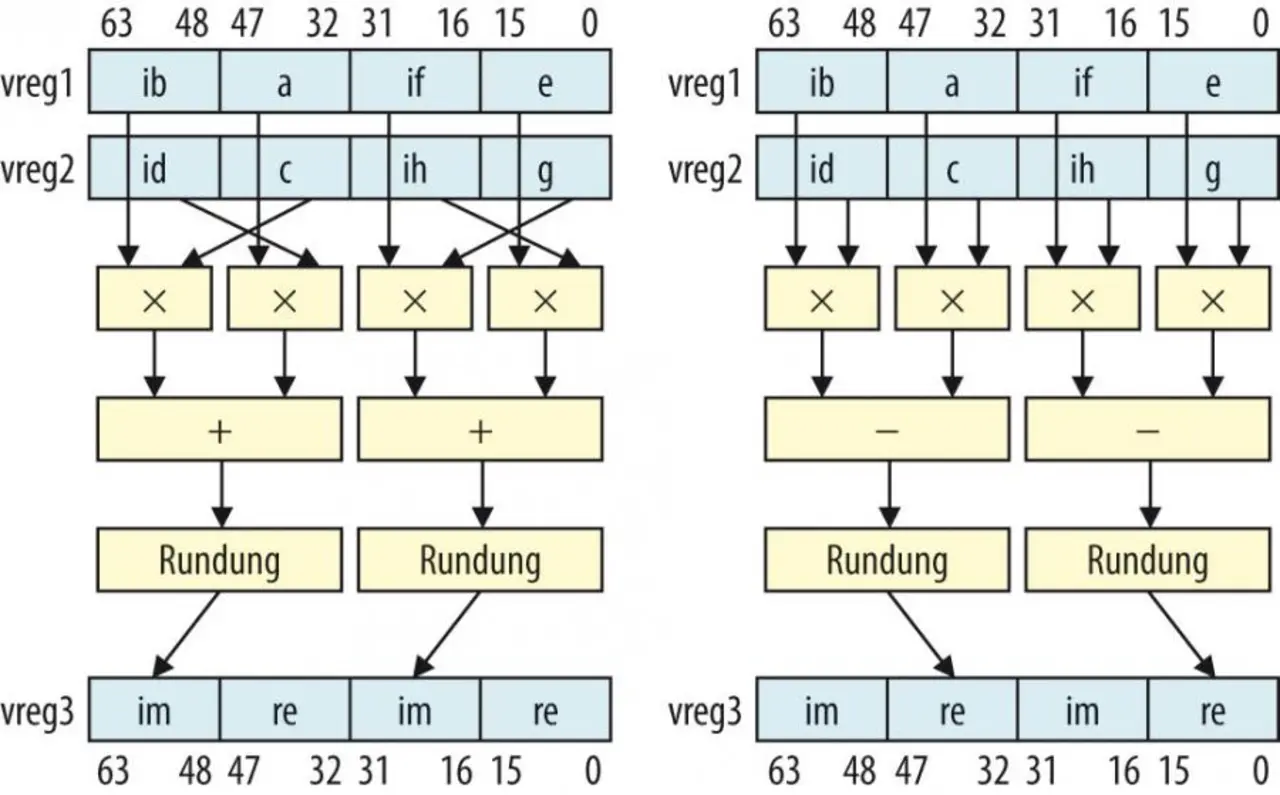

Die allermeisten der SIMD-Befehle werden in einem Taktzyklus ausgeführt und in der Regel steht bereits nach diesem einen Takt das Ergebnis fest. Einige wenige Instruktionen haben eine Latenzzeit von drei Takten. Das heißt, das Ergebnis liegt nach drei Takten vor. Die nachfolgend exemplarisch dargestellte VMULCX.W-Instruktion (Bild 3) ist die einzige, die zwei Takte Ausführungszeit benötigt und zwei bis vier Takte Latenzzeit hat: VMULCX.H (Vector multiply halfword with complex number) im Format VMULCX.H vreg1, vreg2, vreg3.

Die beiden Eingangsvektoren in vreg1 und vreg2 werden als komplexe Zahlen mit einem 16-bit-Real- und einem 16-bit-Imaginärteil aufgefasst. Nach den Rechenregeln komplexer Arithmetik werden jeweils zwei dieser Zahlen miteinander multipliziert, gerundet und das Ergebnis in vreg3 gespeichert.

Real- und Imaginärteile sind jeweils vorzeichenbehaftete 16-bit-Integerzahlen. Hier ist nur die Variante mit 16-bit-Datentypen gezeigt, eine Instruktion für 32-bit-Datentypen ist aber ebenso verfügbar.

- 40-nm-Flash-Technologie für Automotive

- Die RH850G3M-Architektur erweitern

- Hardware-Threading zur Unterstützung virtueller Betriebssysteme

- SIMD-Architektur

- Automatisches In- und Dekrementieren unterstützen

- Einsatz in Body, Chassis, Safety, Audio oder ADAS

- Der Autor