Mikrocontroller

40-nm-Flash-Technologie für Automotive

Fortsetzung des Artikels von Teil 1

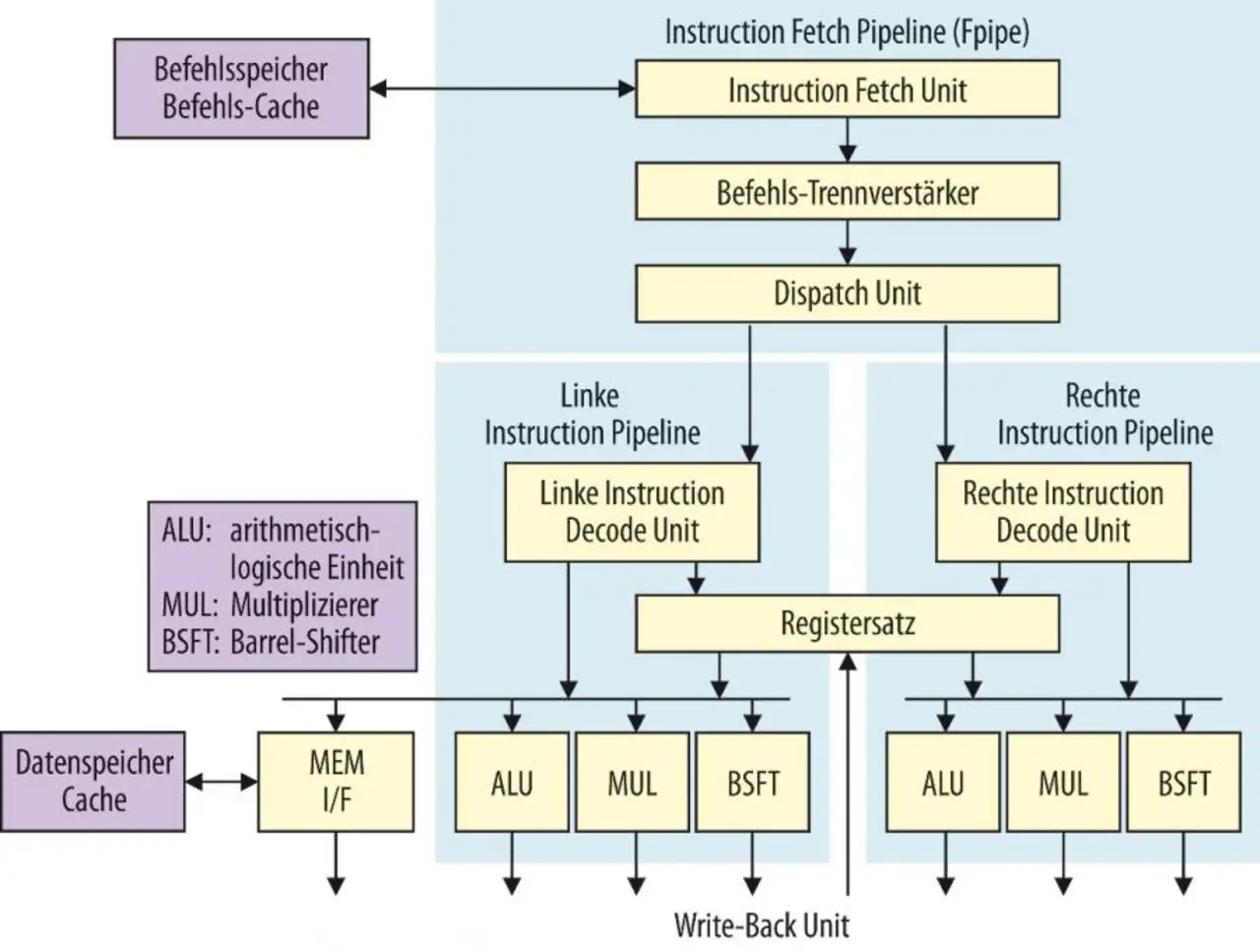

Die RH850G3M-Architektur erweitern

Die RH850G3M-CPU verfügt über zwei Instruktions-Pipelines. Seine Architektur ist in Bild 1 vereinfacht dargestellt. Die gelesenen Instruktionen werden von der Dispatch Unit der passenden Pipeline zur Bearbeitung zugewiesen. So lassen sich bis zu zwei Instruktionen gleichzeitig ausführen. Jede Pipeline verfügt über ihre eigene arithmetisch-logische Einheit (ALU), Multiplizierer (MUL) und Barrel-Shifter (BSFT), so dass die meisten Befehle tatsächlich parallel ausgeführt werden können. Obwohl zwei Pipelines implementiert sind, werden alle Befehle in der Reihenfolge ausgeführt, in der sie im Programm-Code stehen. Die RH850G3M-Architektur weist optional eine Gleitkomma-Einheit (FPU) auf, die die Grundrechenarten in einfacher (32 bit) und doppelter (64 bit) Genauigkeit beherrscht. Diese ist in Bild 1 nicht dargestellt. Darüber hinaus werden Multiply-and-Accumulate-, die Quadratwurzelberechnung und verschiedene Datentyp-Umwandlungen unterstützt. So wie die Basisinstruktionen benötigen auch die meisten FPU-Instruktionen nur einen Takt Ausführungszeit und zwar unabhängig von der Genauigkeit.

Weil zu den Einsatzbereichen der RH850G3M-Bausteine auch sicherheitskritische Anwendungen wie Automotive-Applikationen zählen, wurden mehrere Systemschutzfunktionen implementiert. Deren Grundlage ist die Einführung unterschiedlicher Privilegierungsstufen. In der niedrigsten Stufe, dem User Mode, sind keine Manipulationen an sicherheitsempfindlichen Einheiten – insbesondere an den Schutzmechanismen – möglich. Das Betriebssystem kann so jedem Benutzer-Task seine Ressourcen frei zuweisen. Dazu gehören neben dem Speicherbereich auch die Peripheriebausteine und die maximale Ausführungszeit eines Tasks. So lässt sich beispielsweise verhindern, dass ein Task unerlaubt auf eine Peripherieeinheit zugreift oder dass er beispielsweise durch das Unterbinden von Interrupts die CPU monopolisiert.

Alle bisher genannten Funktionen stehen auch in der neuen RH850G3M-Architektur zur Verfügung. Wichtige Neuerungen sind die Unterstützung für virtuelle Betriebssysteme mit optionalem Hardware-Threading, der SIMD-Koprozessor sowie die Branch Prediction.

Die Zukunft der Embedded-Prozessoren ist bereits von deren größeren Geschwistern im PC-Bereich vorgezeichnet. Auch im Embedded-Bereich fordert der Anwender stetig höhere Rechenleistungen, ohne jedoch bei der elektrischen Leistungsaufnahme kompromissbereit zu sein. Das im PC-Bereich übliche Maximum liegt in der Größenordnung von ca. 100 W, während im Embedded-Bereich selten mehr als 1 Watt zulässig ist. Das beschränkt die möglichen Taktfrequenzen je nach Architektur und Fertigungsprozess auf etwa 200 bis 500 MHz, mit Ausnahmen nach beiden Seiten. Immer kleinere Fertigungsgeometrien erlauben zwar, immer mehr Funktionen auf einer vorgegebenen Fläche zu implementieren, aber sie bringen auch nicht mehr vernachlässigbare Leckströme mit sich. Diese steigen überproportional mit steigender maximaler Taktfrequenz der Transistoren, einfach aus dem Grund, dass schnelle Transistoren nicht mehr richtig ausschalten.

Daher bleibt nur der Ausweg, bei moderaten maximalen Taktfrequenzen mehrere CPU-Kerne auf einem Chip zu integrieren, um so die Gesamtrechenleistung zu vervielfachen. Bei den heute üblichen Architekturen greifen diese Kerne jeweils auf denselben Programmspeicher zu. Allerdings verfügen sie über eigene Caches und eigenes Daten-RAM. Wie bei PC-Prozessoren auch, funktioniert das mit zwei bis vier Kernen recht konfliktfrei. Darüber hinaus begrenzt aber der interne Datenverkehr eine wesentliche Steigerung der Rechenleistung. Dual-Core-Prozessoren sind – abgesehen von pathologischen Fällen – nur wenige Prozent langsamer als zwei einzelne voneinander unabhängige Prozessoren. Buskonflikte sind also die Ausnahme, nicht die Regel.

- 40-nm-Flash-Technologie für Automotive

- Die RH850G3M-Architektur erweitern

- Hardware-Threading zur Unterstützung virtueller Betriebssysteme

- SIMD-Architektur

- Automatisches In- und Dekrementieren unterstützen

- Einsatz in Body, Chassis, Safety, Audio oder ADAS

- Der Autor