Funktionstest

Boundary Scan für alle

Fortsetzung des Artikels von Teil 1

Voraussetzungen für Boundary Scan

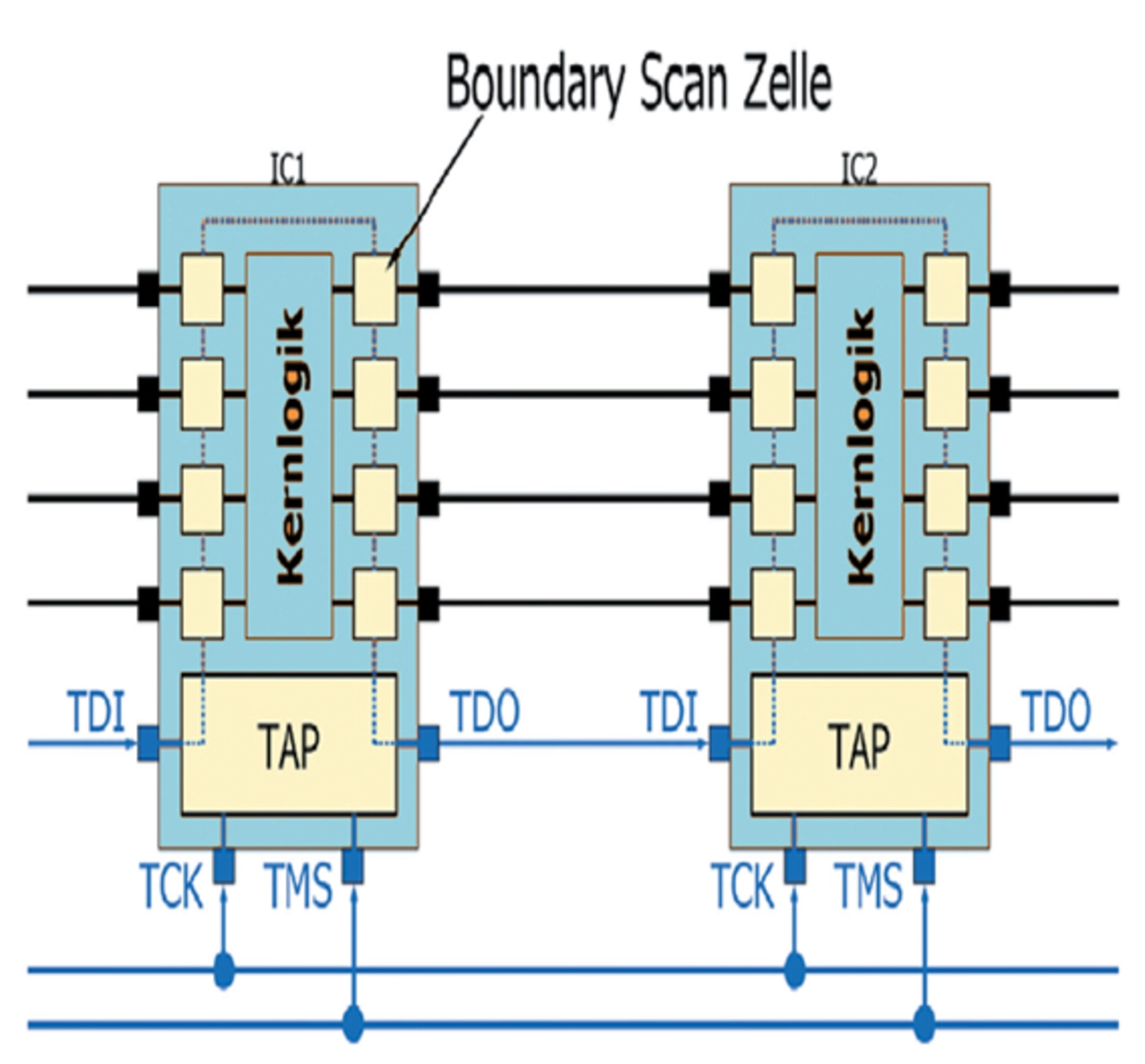

JTAG-fähige Bauteile sind im Inneren rundum mit Scan-Zellen ausgerüstet. Zusätzlich müssen zur sicheren Funktion eines jedes JTAG-Bauteils bestimmte Details integriert sein. So enthält jedes Bauteil je einen TAP (Test Access Port), einen TAP-Controller und zwei Schieberegister, das "IR Instruction Register" und das "DR Data Register" (Bild 1).

Zur Steuerung des Ablaufs ist der TAP mit vier Steuerleitungen (eine fünfte Leitung ist optional) ausgestattet. Für die Signaleingabe steht mit dem TDI (Test Data Input) der serielle Eingang der Schieberegister bereit. Über den TDO (Test Data Output), den seriellen Ausgang der Schieberegister, werden die in den ICs ermittelten Zustände ausgegeben. Für die Aufgabenerfüllung ist der TCK (Test Clock) unerlässlich. Dieser bestimmt die gesamte Testlogik. Die Leitung TMS (Test Mode Select Input) legt fest, welcher Status innerhalb des Zustandsautomaten des TAP bei der nächsten steigenden Flanke des TCK-Taktsignals eingenommen wird. Das Signal TRST (Reset der Testlogik) ist kein fester Bestandteil und demzufolge optional.

Jeder Baustein hat seine eigene ganz spezielle Boundary-Scan-Struktur. Ohne Kenntnis dieser Struktur ließe sich kein vernünftiger Test generieren. Zwar gibt der Standard IEEE 1149.1 einiges dazu zwingend vor, doch es gibt noch genügend Raum für Individualität. Zur Beschreibung dieser Individualität wurde die BSDL (Boundary Scan Description Language) entwickelt. Sie bildet das Bindeglied zwischen Chiphersteller und Testingenieur. In dieser Datei sind sämtliche Informationen enthalten, die zum Testen via Boundary Scan unabdingbar sind (Bild 2).

Jobangebote+ passend zum Thema

- Boundary Scan für alle

- Voraussetzungen für Boundary Scan

- Boundary Scan wird einfacher

- Was ist Adaptive Clocking?