Test-Automatisierung

Board-Test made by FPGA

Fortsetzung des Artikels von Teil 1

Automatisierung macht den Unterschied

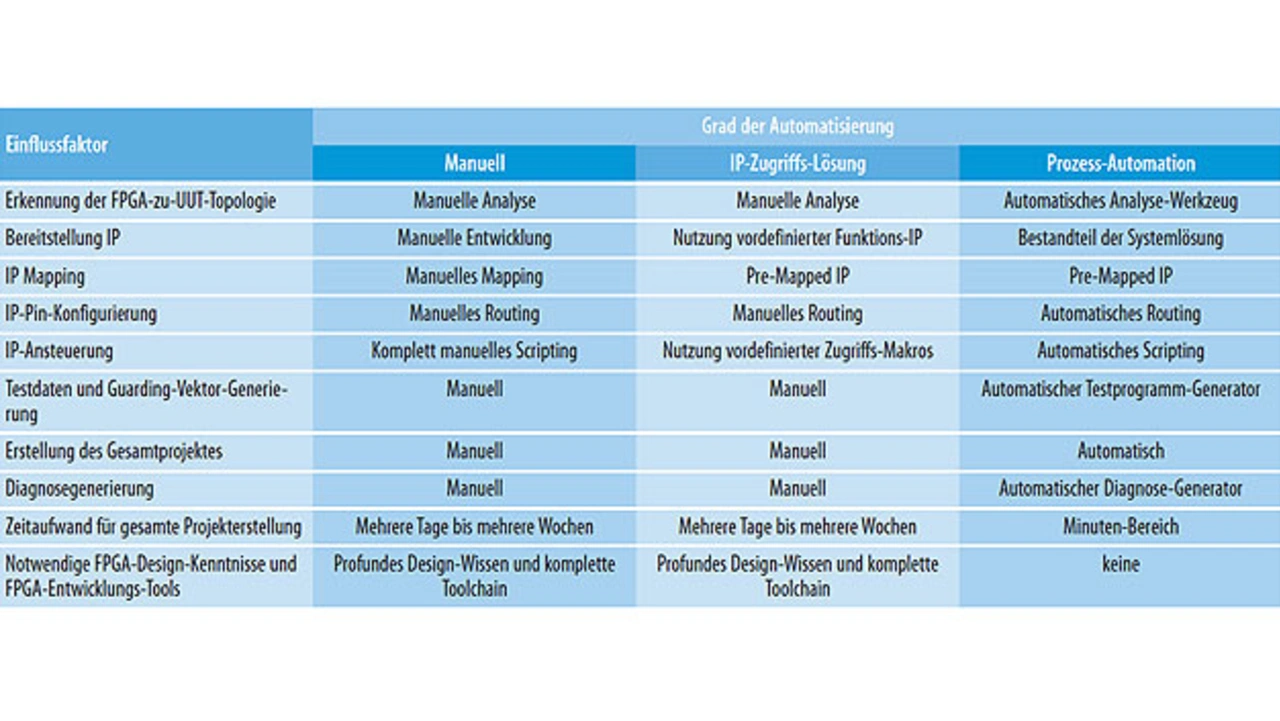

Während der Einsatz von FPGA-embedded Instruments auf den ersten Blick relativ trivial und geradlinig erscheint, führt eine genauere Analyse zu einer ganzen Reihe von Einflussfaktoren und grundlegend zu treffenden Entscheidungen. Die wichtigsten sind:

- Wie erfolgt die Erkennung der FPGA-zu-UUT-Topologie?

- Wer liefert das Instrument-IP?

- Wie wird das JTAG-Mapping durchgeführt?

- Wie erfolgt die IP-zu-Pin-Konfigurierung?

- Wie wird die IP-Ansteuerung realisiert?

- Wer erzeugt die Testdaten und die Guarding-Vektoren?

- Wie erfolgt die Gesamtprojekterstellung?

- Wie erfolgt die Diagnose?

- Wie groß ist der Zeitaufwand für die komplette Projekterstellung?

- Welche FPGA-Design-Kenntnisse und Tools sind notwendig?

Die Bandbreite der Antworten kann in der Praxis sehr groß ausfallen und zieht auch gravierende Unterschiede in den anfallenden Aufwendungen nach sich. Unter dem Blickwinkel der Automatisierung ergibt sich jedoch in groben Zügen eine Einteilung in drei Kategorien (siehe Tabelle 1).

Jobangebote+ passend zum Thema

Bei der rein manuellen Implementierung werden sowohl das IP als auch die notwendigen Prozessschritte durch den Anwender vorgenommen. Das erfordert sowohl umfassendes Design-Wissen über den Target-FPGA als auch die Verfügbarkeit der kompletten Toolchain. Der Aufwand einer solchen Strategie kann sehr groß werden, erfordert jedoch nur minimale Investitionen. Im Endeffekt entsteht eine vollständig applikationsspezifische Lösung.

Eine weitere Variante ist der Einsatz von vorkonditionierten IP-Zugriffslösungen. Bei dieser Variante kommt eine Art IP Kit von einem Systemanbieter zum Einsatz. Das IP beinhaltet die reine Instrumentenfunktion und auch das JTAG Mapping. Außerdem gehören vordefinierte Zugriffsroutinen wie Read- und Write-Prozeduren zum Beispiel auf Basis von Tcl (Test Command Language) zum Lieferumfang. Durch den Einsatz solcher kommerziell verfügbaren Lösungen verkürzt sich die Projektentwicklungszeit. Sie bieten auch den Charme relativ überschaubarer Investitionen, obwohl die Lizensierungskosten eines IP bereits recht hoch sein können. Das hängt unter anderem auch mit einer oftmals notwendigen Volumenlizenz zusammen. Dennoch müssen viele Prozessschritte auch bei dieser Variante manuell getätigt werden.

Die dritte Kategorie ist eine komplette Systemlösung auf Basis eines Framework mit durchgehender Prozessautomatisierung, wie sie zum Beispiel ChipVORX [3] von Göpel Electronic repräsentiert. Hierbei übernehmen Analysatoren, Konfigurations-Tools und Generatoren die Arbeit des Designingenieurs und des Testingenieurs fast vollständig. Basis dieser Vorgehensweise sind die CAD-Daten des Board und eine IP-Bibliothek. Die Adaption des IP auf das Target erfolgt ohne manuellen Eingriff. Automatische Testgeneratoren und Diagnoseprozessoren vervollständigen die Systemlösung. Der Aufwand zur Projekterstellung liegt typischerweise im Minutenbereich und der Anwender braucht keinerlei spezielle FPGA-Tools oder Designerfahrung. Durch die Integration von ChipVORX in die Systemplattform System CASCON [4] ist auch ein Mix von FPGA-embedded-Instruments-Applikationen mit anderen Embedded-Board-Test-Prozeduren wie Boundary Scan oder Prozessoremulation problemlos möglich.

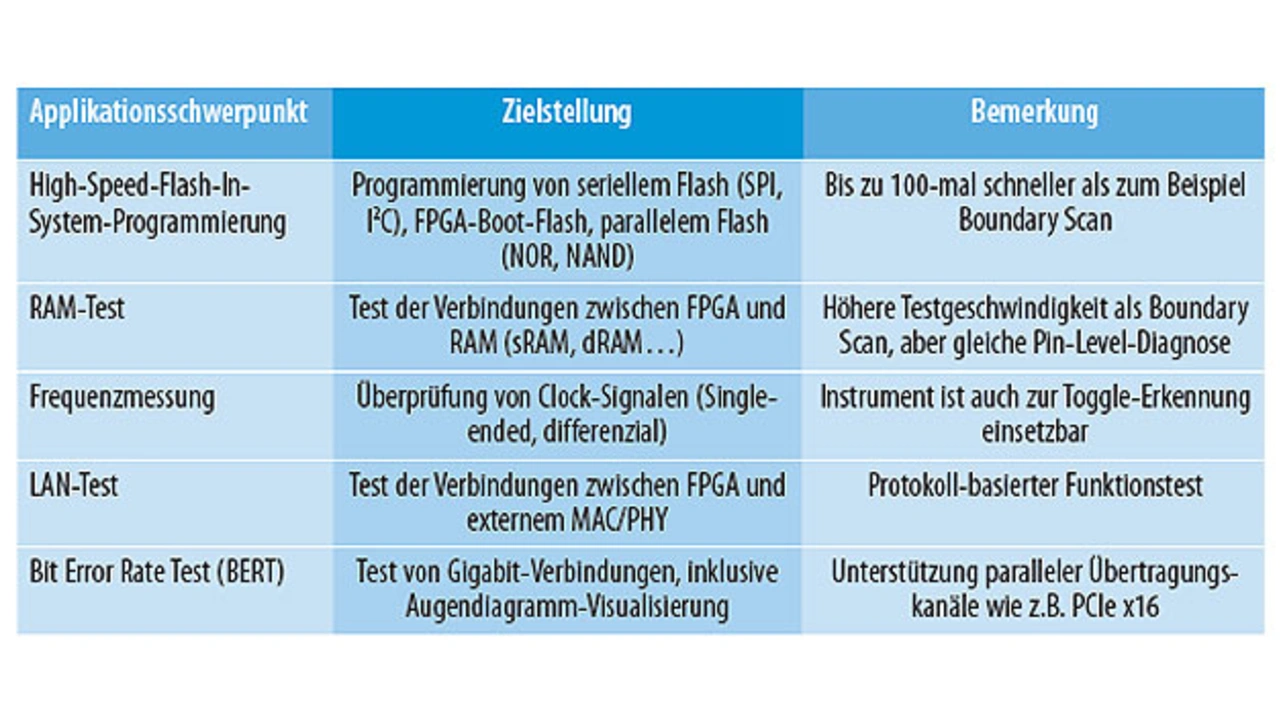

Viel Freude am Testen und Programmieren

Durch den mittlerweile verfügbaren Automatisierungsgrad von FPGA-embedded Instruments zum Board-Test haben sich das Interesse und die Zahl der Applikationen in den letzten Jahren rasant vermehrt. Dabei geht es gemäß Tabelle 2 nicht nur um höhere Testabdeckung, sondern auch um schnellere Flash-Programmierung und bessere Möglichkeiten zur Validierung von Embedded Systems, wo kein physischer Zugriff mehr möglich ist.

Der Zugewinn an Testabdeckung kommt insbesondere durch die höhere Geschwindigkeit der Instrumente zustande. Dadurch können Probleme, wie sie zum Beispiel der Boundary Scan durch die geringe Vektorfolgefrequenz hat, gelöst werden. Das betrifft insbesondere die Flash-Programmierung aufgrund der immer größer werdenden Datenvolumen, aber auch den Test neuer DDR-RAM-Typen, da hier gewisse dynamische Mindestanforderungen einzuhalten sind. Insofern sind FPGA-embedded Instruments eine ideale Ergänzung für den Embedded-Board-Test via Boundary Scan.

Etwas anders sieht die Situation bei Bit Error Rate Tests (BERT) für Gbit/s-Verbindungen aus, die nur mit nominaler Betriebsgeschwindigkeit beziehungsweise unter Stresskonditionen durchführbar sind. Eine rein numerische Beurteilung der Übertragungsqualität reicht hier nicht aus; es werden auch Augendiagramme benötigt. Um derartige Applikationen zu unterstützen, haben die FPGA-Anbieter ausgeklügelte Abtastmechanismen (sogenannte Sampler) direkt hinter dem Gigabit-Receiver fest ins Silizium integriert.

Testen und Programmieren Bilder 5 bis 8

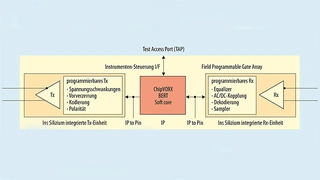

In diesem Fall übernehmen die ChipVORX-IP auch die Ansteuerung dieser Instrumente, harmonisiert mit der notwendigen Schnittstellen-Parametrisierung, sowie den im IP enthaltenen BERT-Patterngenerator und Analysator (Bild 5). Da sämtliche Tx/Rx-Einstellungen interaktiv ohne erneute Designsynthese justierbar sind, erhält auch der Designingenieur ein wirksames Mittel zur Link-Validierung.

Zur flexiblen Ablaufsteuerung existieren verschiedene Modi:

- interaktives Debugging bei der Projekterstellung

- interaktive Messwertvisualisierung mit Gegenbestätigung im Run-Time-Modus

- Standard-Run-Time-Modus mit numerischem Soll/Ist-Vergleich von Messwerten

- Steuerung des Gesamtablaufs durch übergeordnete Instanzen (Systemintegration)

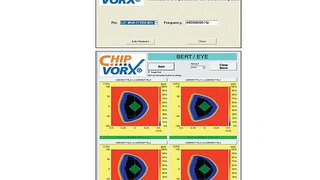

Die Visualisierung von Messwerten erfolgt hierbei in Form von Panels (Bild 6).

Mit den bisher diskutierten Konzepten ist der Einsatz von FPGA-embedded Instruments aber noch lange nicht abgehandelt. Über das Prinzip der Embedded-Testzentren hinaus lassen sich FPGAs auch hervorragend zum Design flexibler, externer Test-Hardware verwenden. Als Beispiel seien an dieser Stelle die ChipVORX-Module (Bild 7) genannt. Die Idee dahinter ist recht einfach. Die Module werden durch Mapping auf das gleiche Beschreibungsniveau wie das zu testende Board gebracht und damit von Seiten der Tools als Einheit verarbeitet. Alle Features und Prozeduren bleiben daher identisch, obwohl es sich um eine externe Zusatzelektronik handelt. Durch entsprechende Konfektionierungsmodule lassen sich auf dieser Basis auch Standardschnittstellen wie PCIe, SATAe oder USB 3.0 testen. Für Boundary-Scan-Zwecke bieten all diese Module auch IEEE-1149.1- und IEEE-1149.6-Untersützung [5].

Die Ansteuerung dieser Module erfolgt über den normalen Test Access Port, wobei auch mehrere Module gleichen oder unterschiedlichen Typs kaskadiert werden können. Ein derartiger Testplatz (Bild 8) lässt sich einfach konfigurieren und unterstützt selbst den Test von Objekten, die keine On-Board-FPGAs haben. Darüber hinaus können solche Module auch sehr einfach in Fixtures montiert werden und über Nadeln kontaktierte Testpunkte ansteuern.

Das eigentliche Non plus ultra für den Produktionstest entsteht aber erst durch die Kombination sämtlicher Embedded-Test-Verfahren wie Boundary Scan, Processor Emulation Test, In-System-Programmierung und FPGA-embedded Instruments in einer Umgebung unter Einbeziehung von externen I/O-Modulen und weiteren externen Standard-Instrumenten. Dafür sind entsprechend ausgereifte Hardware- und Software-Plattformen wie System CASCON unabdingbar. Diese Plattform unterstützt natürlich auch die komplett manuelle Projektentwicklung auf Basis eigener IP und ihre komfortable Ansteuerung auf Sprachniveau.

Schlussfolgerungen

Die ständigen Innovationen bei FPGAs sichern die Zukunftsfähigkeit derartiger Lösungsansätze für den Embedded-Test nachhaltig. Auch auf Seiten der Gerätetechnik hat sich in den letzten Jahren sehr viel getan. Der Anwender kann für seine individuellen Bedürfnisse aus einer großen Anzahl von unterschiedlichen Lösungsansätzen auswählen. Vor allem die fast vollständig automatisierten Systemlösungen gewährleisten hierbei kurze Realisierungszeiten und befreien den Anwender von den Hürden spezifischen FPGA-Wissens und entsprechender Entwicklungswerkzeuge. Das sind insbesondere für EMS-Dienstleister sehr wichtige Entscheidungskriterien.

Der Applikationsbandbreite sind bei FPGA-embedded Instruments nahezu keine Grenzen gesetzt. Selbst für Gigabit-Links existieren mittlerweile sehr ausgereifte Werkzeuge und das Produktportfolio an IP wird ständig erweitert. Darüber hinaus bieten externe FPGA-Module die Möglichkeit, die Testbarkeit auf nativem Wege zusätzlich zu verbessern. Wenn dann alle genannten Vorteile noch auf einer Plattform mit weiteren Embedded-Test-Strategien gemixt werden, steht der Freude am Board-Test made by FPGA nichts mehr im Wege.

Literatur

[1] IEEE Std.1149.1-2013, Standard Test Access Port and Boundary Scan Architecture.

[2] IEEE Std. 1687, Standard for Access and Control of Instrumentation Embedded within a Semiconductor Device.

[3] ChipVORX Technologie, Produktprospekt, Göpel electronic, 2015.

[4] Boundary Scan Software SYSTEM CASCON, Produktinformation Göpel electronic, 2015.

[5] IEEE Std. 1149.6-2015, Standard for Boundary Scan Testing of Advanced Digital Networks.

Die Autoren

| Thomas Wenzel |

|---|

| ist Geschäftsführer Embedded JTAG Solutions bei der Göpel Electronic GmbH |

| Sven Haubold |

|---|

| ist Hardware-Entwickler Embededd JTAG Solutions bei der Göpel Electronic GmbH |

- Board-Test made by FPGA

- Automatisierung macht den Unterschied