Positionsbestimmung mit IEEE 802.11az

Standorte per Deep Learning bestimmen

Fortsetzung des Artikels von Teil 2

Bau eines Prototyps

Der letzte Schritt dieses Arbeitsablaufs besteht in der Realisierung der vortrainierten Netze mit einem FPGA. Matlab Deep Learning für HDL bietet vorgefertigte Bitströme für einen auf dem FPGA laufenden Prozessor. Diese sind auf eine Frequenz von mehr als 200 MHz eingestellt. Hierdurch können der Ressourcenbedarf und die Leistung abgeschätzt werden, bevor ein HDL-Code generiert oder auf einem FPGA-Modul implementiert wird.

Für individuelle Ziele können die Bitströme neu erstellt werden.

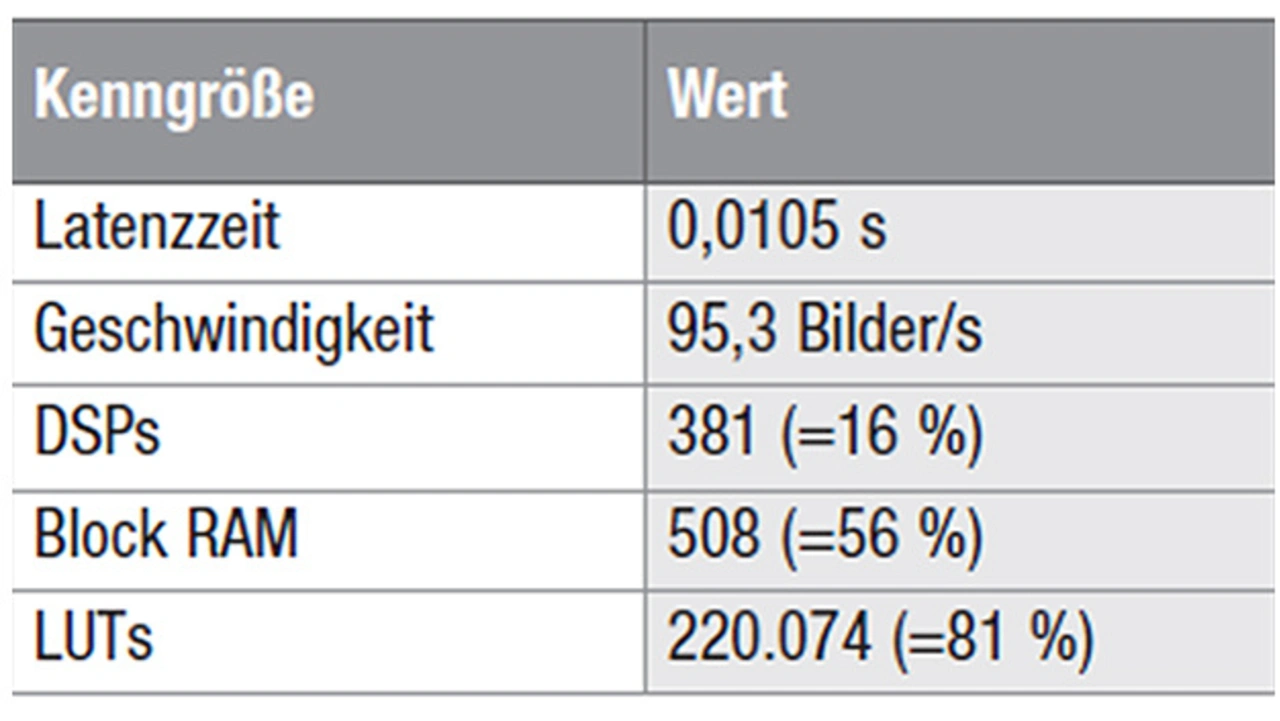

Es bietet sich an, sich in einem ersten Schritt ein Bild vom Speicherbedarf und der Leistung des Netzes mit einzelnen Gleitkommadatentypen zu machen. Die Ressourcen- und Leistungsabschätzung für das Entwicklungsmodul Zynq UltraScale+ MPSoC ZCU102 von Xilinx ist in Tabelle 3 dargestellt.

Jobangebote+ passend zum Thema

Es ist zu beobachten, dass für ein relativ kleines Netz von zehn Schichten viele Ressourcen – vor allem LUTs und Block-RAM (BRAM) – gebraucht werden. In einer gängigen Anwendung dient die Bereitstellung eines einzelnen Datentyps als Benchmark, auf den Optimierungen angewendet und miteinander verglichen werden.

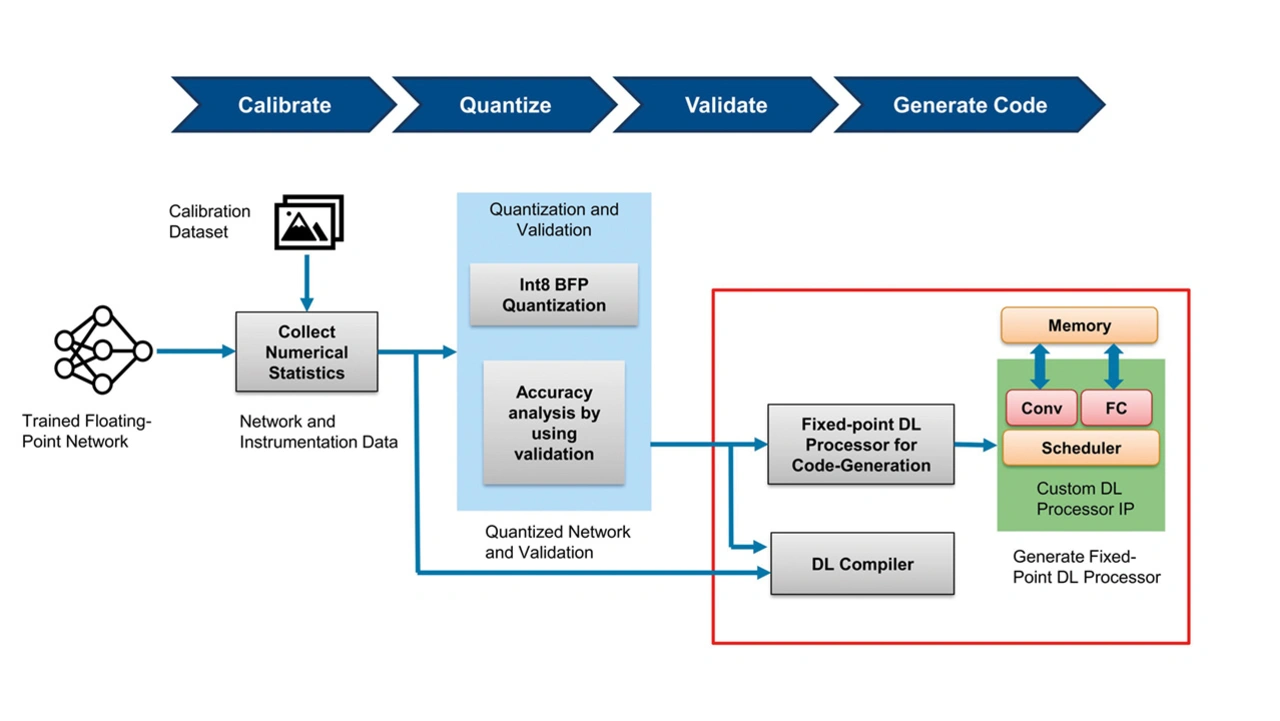

Eine dieser Optimierungen ist die Quantisierung des Netzwerks zur Verwendung von int8-Festkomma-Datentypen. Durch die Quantisierung wird die Anzahl der Bits, die für jeden Koeffizienten im Netz benötigt werden, reduziert und damit der Ressourcenbedarf verringert sowie die Leistung verbessert. Mit den Tools von Matlab lässt sich dabei ein Netzwerk wie in Bild 9 gezeigt automatisch quantisieren.

Anhand der in Bild 9 dargestellten Schritte können die Leistung des quantisierten Netzes verglichen werden. Die Ergebnisse sind in Tabelle 4 aufgeführt.

Die Latenzzeit und die Verarbeitungsgeschwindigkeit haben sich bei der Verwendung von int8-Festkomma-Datentypen drastisch erhöht. Ferner ist eine deutliche Reduzierung der BRAM- und LUT-Nutzung zu verzeichnen. Es ist also festzustellen, dass der Einsatz von DSPs zugenommen hat. Der Grund hierfür liegt in der Tatsache, dass aufgrund des geringeren Speicherplatzbedarfs mehr Verarbeitungsthreads verwendet werden können, was zu einer Leistungssteigerung führt. Damit ist eine Optimierung erreicht, das Netzwerk kann im FPGA programmiert werden, um es in Echtzeit zu klassifizieren. Der Arbeitsablauf vom Netzwerkentwurf bis zur FPGA-Implementierung ist damit abgeschlossen.

Die Autoren

Dr. Ahmad Saad

ist Senior Application Engineer bei MathWorks und hat sich auf Funkkommunikation und Signalverarbeitung spezialisiert. Bevor er zu MathWorks kam, war er bei der Fraunhofer-Gesellschaft in München als Forscher und Teamleiter tätig, wo er an Projekten beteiligt war, die sich mit der Entwicklung und der Modellierung von kognitiven Kommunikationssystemen für Anwendungen in ultrazuverlässigen industriellen und fahrzeuggestützten Systemen befassten. Seine Promotion in Kommunikationssystemen, die er 2019 abschloss, wurde gemeinsam von der Fraunhofer-Gesellschaft in München und der Universität Augsburg betreut.

ahmads@mathworks.com

Florent Busnoult

ist Senior Application Engineer bei MathWorks. Sein Schwerpunkt liegt auf Matlab und Simulink für Funkkommunikation in den USA. Vor seiner Tätigkeit bei MathWorks arbeitete er in der Forschung und Entwicklung bei Intel, bevor er Anwendungsingenieur bei Azimuth Systems, einem Unternehmen für HF-Testgeräte, und bei Honeywell Security in Europa wurde. Busnoult hat einen Master-Abschluss in Telekommunikation von der École des Mines Télécom Atlantique (IMT Altlantique).

fbusnoul@mathworks.com

Nadia Shivarova

ist Senior Application Engineer bei MathWorks. Sie ist spezialisiert auf die Unterstützung von Kunden in der Unterhaltungselektronik-, Halbleiter-, Luft- und Raumfahrtindustrie bei der Modellierung und Simulation von Funksystemen, vom Entwurf von DSP-Algorithmen bis zur Hardware-Implementierung. Zu Shivarovas jüngsten Interessen gehört die Einbindung von KI in Funkanwendungen. Sie hat 2016 ihr Studium in Elektronik und Elektrotechnik an der University of Strathclyde, Glasgow mit einem Master (MEng) abgeschlossen.

nshivaro@mathworks.com

- Standorte per Deep Learning bestimmen

- Datenaufbereitung

- Bau eines Prototyps

- Literatur