MIMO Needs FinFET

7 Key Changes, Analog Designers Will Need to Make

Fortsetzung des Artikels von Teil 7

7. Simulations Are Slow

FinFET models are complex, which leads to slow simulations. And, since the parasitic resistance cannot be ignored, most of the simulations will be performed with an extracted netlist including thousands of components.

This means a brute force approach, relying on big servers and multi-core simulators is necessary for thorough verification of the design. However, our recommendation is to adapt the simulation strategy to this challenge and increase the hierarchical levels in the design.

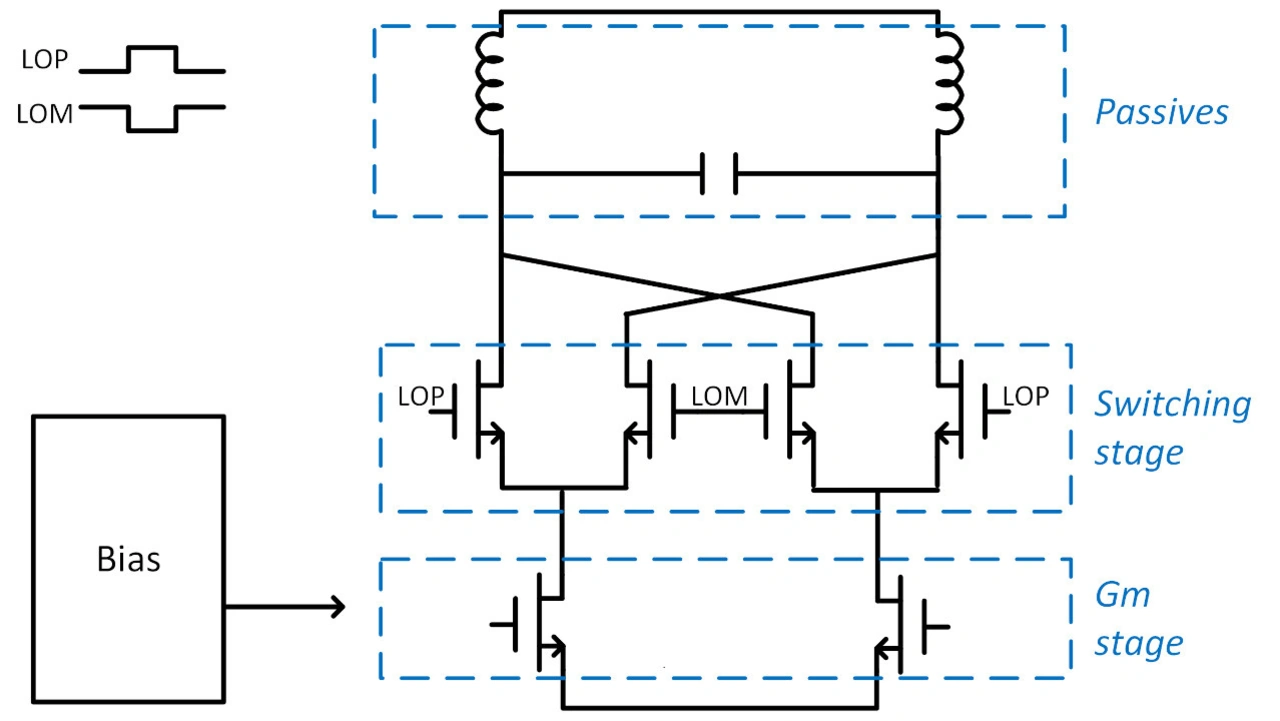

For example, Figure 4 proposes a more structured hierarchy for a simple Gilbert-cell mixer. Obviously, given the limited number of components, the whole circuit could be drawn flat. However, after layout extraction this choice leads to a large flat netlist, with limited simulation and debugging options.

On the other hand, a more granular hierarchy like the one we suggest separates the different sections of the design based on their functionality. Depending on the simulation, this gives the designer flexibility to use accurate (fully extracted) views for critical sub-blocks whilst using more coarse models for the other sections.

As a rule of thumb, we should be keeping most of block-level simulation times to below one hour and resort to brute force tests only in the final verification stage.

- 7 Key Changes, Analog Designers Will Need to Make

- 1. Do not Mix Devices Having Different Dimensions

- 2. Use Repeatable Patterns

- 3. Estimate Interconnect Parasitics From the Start

- 4. Use Digital Calibration to Correct Analog Errors

- 5. Current Density limits the Transmitter Output Power

- 6. High Flicker Noise Corner Frequency

- 7. Simulations Are Slow