Lattice:

PLD-Familie MachXO2 adressiert kosten- und energiesensitive Designs

Bis zu 30 % geringere Kosten und Senkung der Stromaufnahme auf weniger als 1/100 im Vergleich zur Vorgängerfamilie sollen für Lattice neue Märkte in der Industrie und bei Konsumeranwendungen erschließen. Dafür hat Lattice an zahlreichen Schrauben gedreht.

Mit den High-End-FPGAs mit ihren hunderttausenden Logik-Elementen von Xilinx und Altera will und kann Lattice nicht konkurrieren. Die MachXO2-Familie soll einerseits Low-End-FPGAs wie Cyclone, Spartan und Igloo Marktanteile abnehmen und andererseits Low-End-ASICs, wie sie z.B. in Handys zum Multiplexen von I2C- oder SPI-Bus eingesetzt werden, ersetzen.

Bei Bausteine werden in einem 65-nm-Low-Power-Prozess mit Embedded Flash-Technologie aufgebaut. Gegenüber der MachXO-PLD-Familie wird damit eine dreimal höhere Logik-Integrationsdichte, zehnmal mehr Embedded-Speicher, eine Verringerung des statischen Stromverbrauchs um mehr als den Faktor 100 sowie eine Kostenreduktion um bis zu 30 % erreicht. Die reduzierte Stromaufnahme kann nicht alleine durch das Schrumpfen der Prozessgeometrie erklärt werden: Vielmehr hat Lattice eine Mischung von Transistoren mit unterschiedlichen Gate-Längen und (und damit Leckströmen) eingesetzt, um die Schaltzeiten dem tatsächlichen Bedarf anzupassen. Ebenso wurde Power-Gating implementiert, mit dem ganze Blöcke dynamisch ein- und abgeschaltet werden können. So nimmt alleine ein LVDS-I/O rund 10 mW auf (2,5 V und 3,5 mA), das bei Nicht-Benutzung natürlich abgeschaltet werden kann.

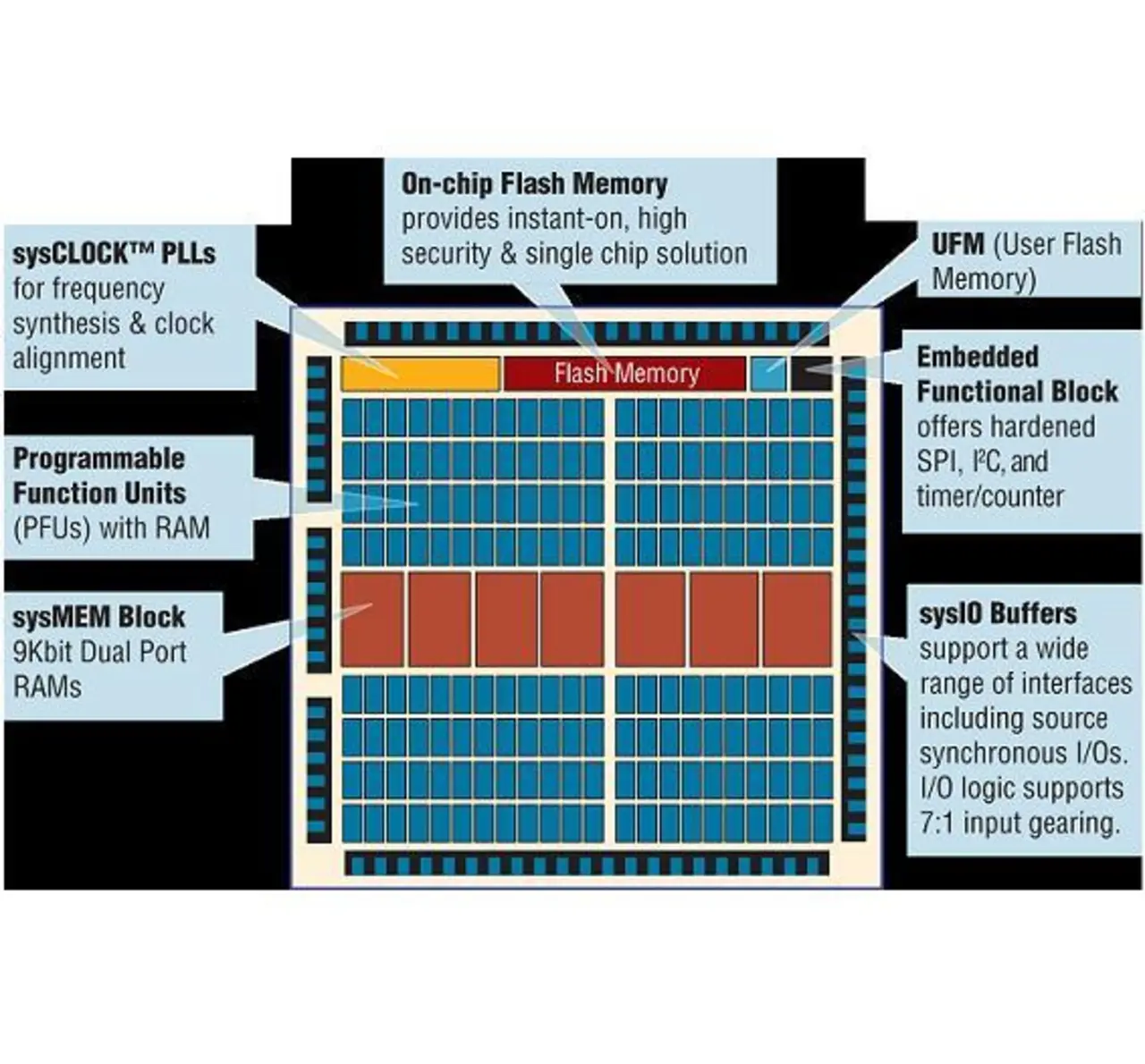

Eine Reihe von Funktionen, die in Low-Density-PLD-Anwendungen gerne eingesetzt werden, wurden zusätzlich als Hardware-Macros in die MachXO2-Bausteine integriert: Flash-Speicher (UFM), I2C, SPI und Timer/Zähler. Damit erhält der Entwickler ein "Universal-PLD" für kostensensitive Großserien-Designs.

Unverzichtbar für die Zielmärkte sind möglichst geringe Kosten pro I/O. Lattice hat diese daher in unsymetrisch großen Bänken angeordnet (Bild), um keine I/Os zu verschwenden. Häufig werden nämlich viele I/Os mit 3,3 V und vergleichsweise wenige mit 1,2/1,8 V benötigt.

Drei Produkt-Optionen

MachXO2-ZE-Bausteine enthalten zwischen 256 und 7K Look-up-Tabellen (LUTs), arbeiten mit einer nominellen Versorgungsspannung von 1,2 V und unterstützen einen Systemtakt bis zu 60 MHz. Mit einer statischen Leistungsaufnahme von nur 19µW und Gehäuseformaten bis hinab zu 2,5 x 2,5 mm sind diese für kostensensitive und Strom sparende Konsumelektronik-Anwendungen wie Smartphones, GPS-Geräte und PDAs optimiert.

MachXO2-HC-Bausteine enthalten zwischen 256 und 7K LUTs, arbeiten mit einer nominellen Versorgungsspannung von 3,3 V oder 2,5 V und unterstützen einen Systemtakt bis zu 150 MHz. Ein interner Spannungsregler reduziert die Eingangsspannung auf 1,2 V. Mit bis zu 335 nutzbaren I/O-Kanälen eignen sich diese Bausteine für Steuerungs-Anwendungen in Endmärkten wie Telekommunikations-Infrastruktur, Rechnertechnik, Industrieelektronik und medizinische Geräte.

MachXO2-HE-Bausteine weisen zwischen 2K und 7K LUTs auf, arbeiten mit einer nominellen Versorgungsspannung von 1,2 V und unterstützen einen Systemtakt bis 150 MHz. Diese Bausteine sind für Systemanwendungen mit kritischen Stromverbrauchs-Anforderungen optimiert.

Für eine schnelle Entwicklung und den Einsatz gängiger Funktionen in System- und Konsumelektronik-Anwendungen stehen mehr als 20 Referenz-Designs mit MachXO2-Bausteinen kostenlos zum Download auf der Lattice-Website bereit. Zusätzlich plant Lattice, zwei Entwickler-Kits bereitzustellen, mit denen sich die Evaluation der MachXO2-Bausteine beschleunigen lässt.

Die MachXO2-Bausteine LCMXO2-1200ZE und LCMXO2-1200HC sind jetzt als Alpha-Muster verfügbar; Entwicklungsmuster sind voraussichtlich im Dezember 2010 erhältlich und Produktions-Bausteine werden im März 2011 lieferbar sein. Die Preise für den LCMXO2-256ZE/HC TQFP100 betragen 0,75 Dollar beziehungsweise 2,00 Dollar für den LCMXO2-1200ZE/HC TQFP100, jeweils in Stückzahlen von 500.000 Einheiten. Alle Mitglieder der MachXO2-Produktfamilie werden voraussichtlich bis zum Ende des dritten Quartals 2011 in Serie gefertigt und lieferbar sein.