Managed NAND – eine Alternative zu NOR-Flash-Bausteinen

Fortsetzung des Artikels von Teil 1

NAND Failure Modes

Die NAND-Technik steht der NOR*Technik in einem nach: Aufgrund verschiedener Ausfalleffekte ist sie weniger zuverlässig. Diese Effekte bei der NAND-Technik lassen sich in zwei Fehlerarten kategorisieren:

- Block-Status-Fehler: Ein Schreiboder Löschvorgang kann für einen bestimmten Block nicht erfolgreich abgeschlossen werden.

- Bit Error Rates: Fehlerhafte Bits können über den entsprechenden Grad der Fehlerkorrektur (ECC, Error Code Correction) wieder hergestellt werden. Diese Korrektur führt nicht zu einem Datenverlust oder einem Statusfehler.

Die Fehlerraten lassen sich ebenfalls unterscheiden: in RBER (Raw Bit Error Rate – Fehler, bevor eine Fehlerkorrektur durchgeführt wurde), und in UBER (Uncorrectable Bit Error Rate – Fehlerrate nach der Korrektur). Die UBER kann mit Hilfe der gemessenen RBER und einem spezifischen Level der Fehlerkorrektur errechnet werden. Je höher der Grad der Fehlerkorrektur, desto geringer ist die Anzahl der UBER. Hierdurch lassen sich Fehlerraten von 1 × 10–19 bis 1 × 10–15 UBER erreichen. NAND-Speicher werden damit ebenso zuverlässig wie NOR-Speicher.

Jobangebote+ passend zum Thema

Wissenswertes zum NAND Failure Mechanism

Dass NAND-Techniken fehleranfälliger sind, lässt sich auf folgende Fehlermechanismen zurückführen, die zu Störungen und damit zu Bit- oder Blockfehlern führen können:

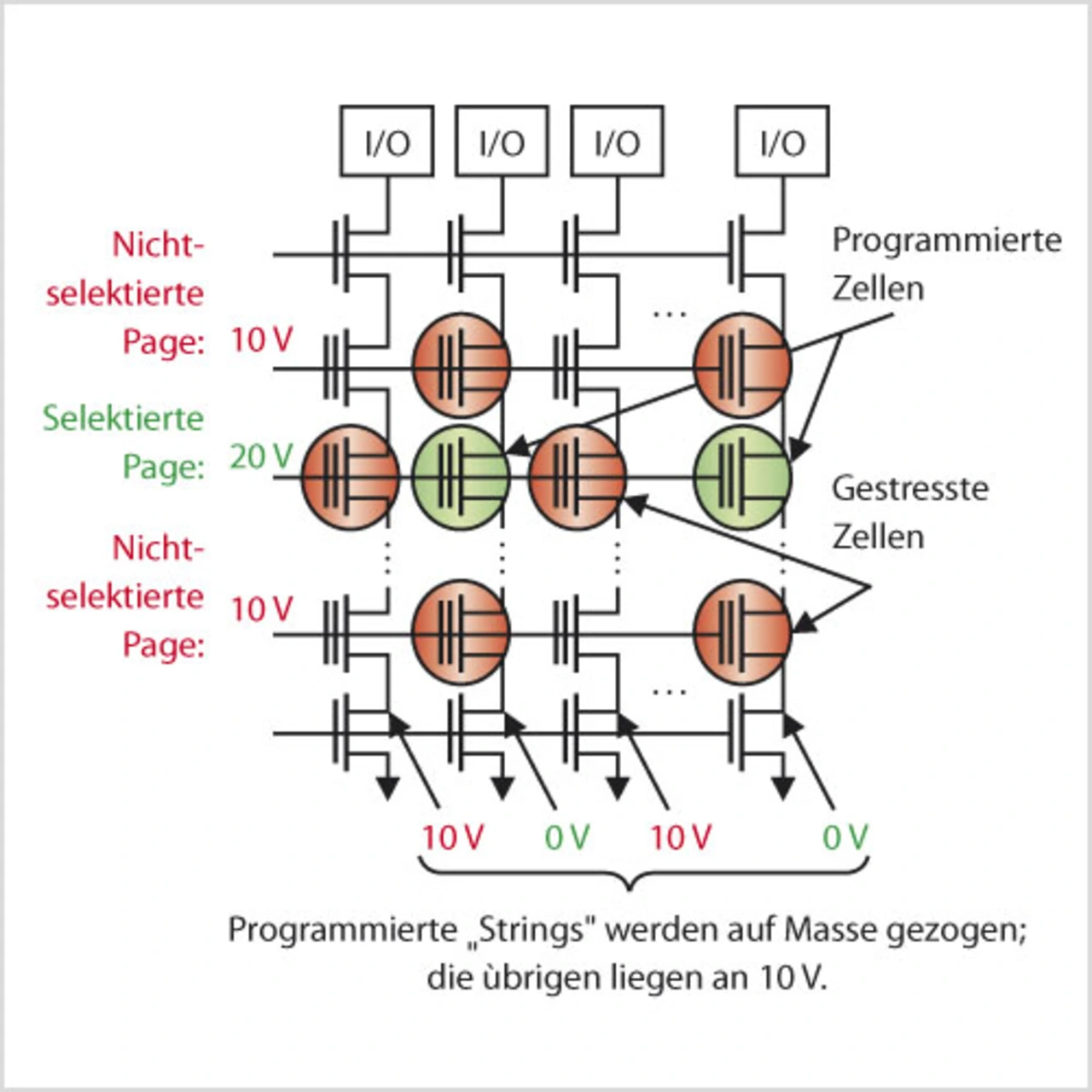

- Program Disturb (Bild 2): Um eine Page zu programmieren, wird eine Spannung von 20 V angelegt. Dabei fließen die Elektronen in das Floating Gate. Hierbei kann es vorkommen, dass sich bei benachbarten Zellen (Stressed Cells) am Floating Gate ebenfalls Ladung ansammelt. Die Zelle erscheint dadurch als unzureichend programmiert. Nur teilweise programmierte Pages erhöhen die Möglichkeit einer Störung. Andererseits werden die Stressed Cells dabei nicht beschädigt. Ein Löschvorgang versetzt die Zelle wieder in einen störungsfreien Zustand. Entsprechende Bitfehler lassen sich mit Hilfe von ECC (Fehlerkorrektur) korrigieren.

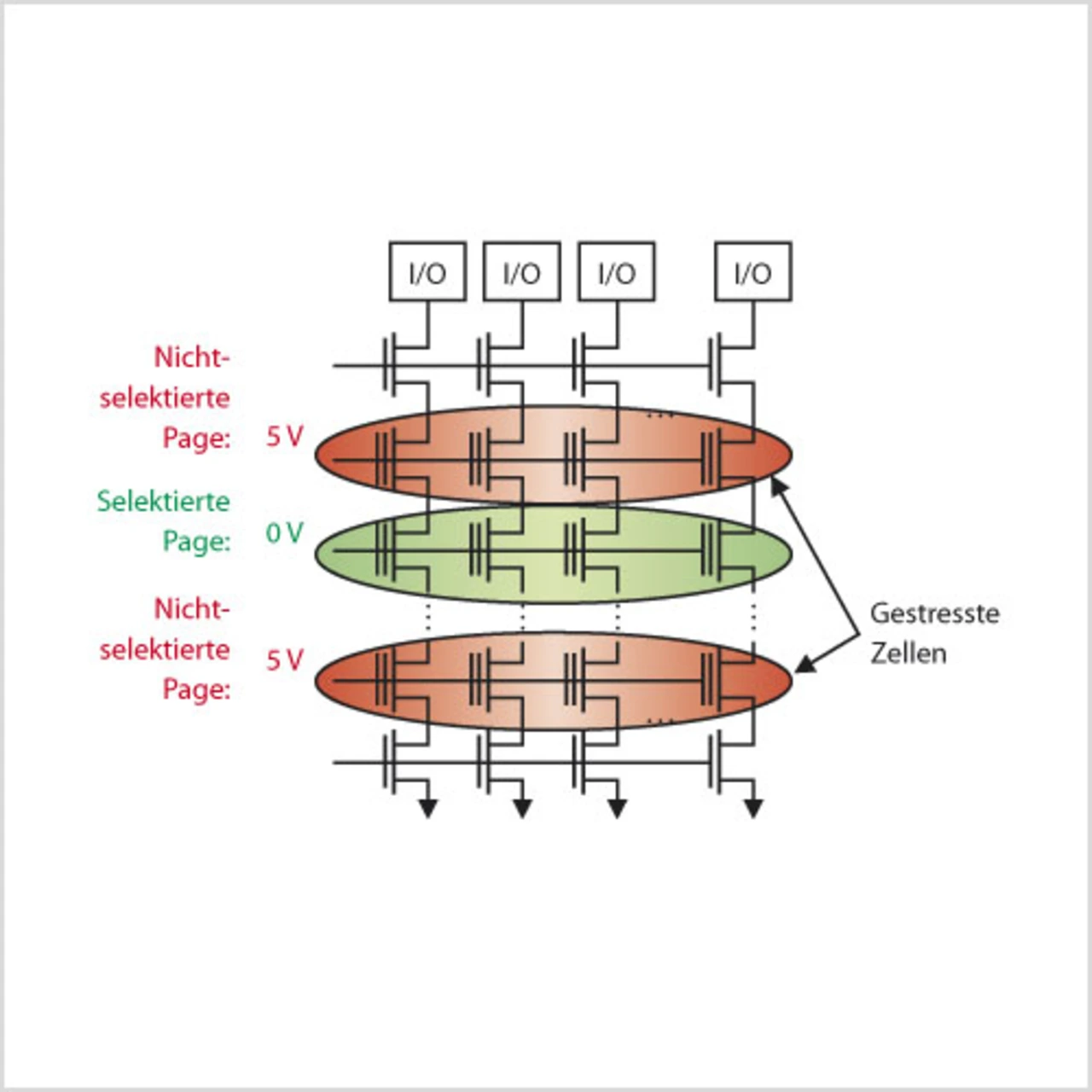

- Read Disturb (Bild 3): Das Auslesen einer NAND-Zelle erfolgt über das Messen der Ladung im Floating Gate. Bei jedem Lesevorgang geht ein sehr geringer Teil der Ladung verloren, so dass das Gate ab einem bestimmten Wert als unzureichend programmiert erscheint. Die Daten müssen dann über ECC korrigiert und neu abgespeichert werden. Als Faustregel für die maximale Anzahl der Lesevorgänge bis zum nächsten Löschvorgang innerhalb eines Blocks gelten 1 Million Zyklen bei SLC und 100 000 Zyklen bei MLC. Nach dem Löschvorgang wird der Read-Disturb-Zähler auf Null zurückgesetzt. Wird die maximale Anzahl an Lesezyklen überschritten, sollte der Inhalt in einen anderen Block übertragen und der bisherige als ungültig markiert werden.

- Data Retention: Im Zeitverlauf entsteht ein Ladungsverlust am Floating Gate, durch den der Schwellwert der Spannung bis zum Ruhezustand absinkt. Die Zellen sind unbeschädigt und können sicher gelöscht und wiederbeschrieben werden. Die Programmier-, Lösch- und Lesevorgänge beeinflussen die Dauer des Datenerhalts. Bei Blöcken, die einen langen Datenerhalt benötigen, empfiehlt es sich, die Programmier- und Löschzyklen sowie die Lesevorgänge zu begrenzen. So lassen sich Read Disturbs vermeiden.

- Endurance: Schreib- und Löschzyklen führen zu einer Abnutzung des Tunneloxyds. Dadurch können Teile der Ladung im Dielektrikum eingefangen werden; sie verursachen dann einen Fehler beim Schreib- oder Löschvorgang. Um die Lebensdauer der Zellen zu verlängern, gilt es immer, den Status zu prüfen: Finden die Schreib- oder Löschoperationen fehlerfrei statt? Schlägt ein Schreibvorgang fehl, sollten die Daten aus dem Block in einen anderen übertragen werden, der Block als Bad Block markiert und nicht weiter verwendet werden. Die Fehlerkorrektur behebt zwar auftretende Fehler, doch sollte man die Metadaten des Block-Managements in einem zusätzlichen Bereich mit ECC sichern. Auch das gleichmäßige Beschreiben aller gültigen Blocks (wear leveling) sorgt für eine längere Lebensdauer der Zellen.

- Managed NAND – eine Alternative zu NOR-Flash-Bausteinen

- NAND Failure Modes

- Platz, Zeit und Kosten: dreifache Ersparnis

- Autor:<br><br>