Robuster 30-V-P-Kanal-Trench-MOSFET mit niedrigem Widerstand

Fortsetzung des Artikels von Teil 1

Robuster 30-V-P-Kanal-Trench-MOSFET mit niedrigem Widerstand

Die Fehlerbereiche befanden sich in der Mitte zwischen den N+-Body-Streifen, übereinstimmend mit dem sekundären MOS-Durchbruch aufgrund eines parasitären Einschaltens des bipolaren NPNTransistors.

Jobangebote+ passend zum Thema

Bipolares Einschalten [3] ist proportional zum Basis-Widerstand (Rb) mit einem Mittelpunkt zwischen den Streifen, der sich am weitesten entfernt vom N+-Body-(Basis-)Kontakt befindet – bei höchstem Rb. Sobald sich der Einschaltvorgang in einer kleinen Fläche ereignet, wird die sich ergebende hohe Stromdichte zu einem großen Fehlergebiet führen. Diese Transistoren konnten nur geringe Ströme von wenigen Ampere bewältigen. Sobald der N+-Body-Abstand auf unter 20 µm gesenkt wurde, beobachtete man die typischen UIS-Kurven bei unterschiedlichen Induktivitätswerten.

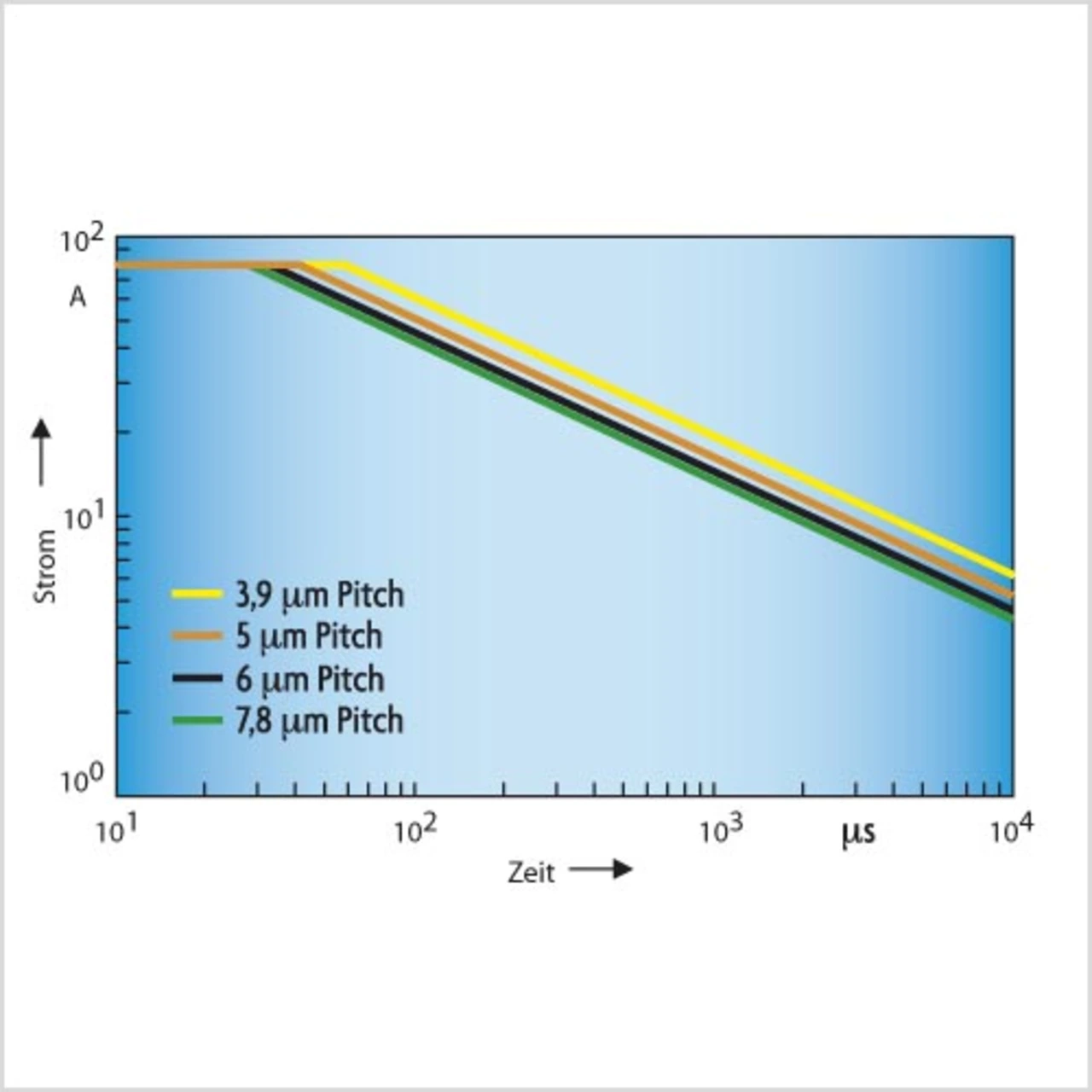

Bild 12 zeigt die Ergebnisse eines Experimentes, bei dem der N+-Abstand zwischen 3,9 µm und 7,8 µm variiert wurde. Dieser Siliziumtest zeigt eindeutig, dass das Verringern des N+- Abstandes parasitäres bipolares Sperren verhindert und das Hochstrom- UIS-Verhalten verbessert.

Abschließend wurde das Design auf robustes UIS-Strom-Verhalten mit optimierter N+-Body-Tiefe, Streifenbreite und optimiertem Streifenabstand abgestimmt. Um ein optimales MOSFETDesign zu erreichen, wurden die Elemente in der Schaltung bezüglich unterschiedlicher Induktivitätswerte getestet, um die UISEigenschaften bei hohen Strömen sowie kurzen und breiten Impulsen herauszufinden. Das abschließend gewählte N+-Body-Design musste sekundäre Durchbrüche bei hohen Strömen vermeiden, kombiniert mit gutem UIS-Verhalten bei geringem Strom und breiten Impulsen. Gerhard Stelzer

Literatur:

[1] Narazaki, A.; et al: A marvelous low on-resistance 20V rated Self Alignment Trench MOSFET in 0,35 µm LSI design rule with both high forward blocking voltage and yield and large current capability. Proceedings of ISPSD 2004, S. 393 – 396.

[2] Kinzer, D.; Asselanis, D.; Carta, R.: Ultra-Low Rdson 12V P-channel trench MOSFET. ISPSD 2000.

[3] Jayant Baliga, B.: Power Semiconductor Devices. PWS Publishing Co., 1999.

| Ashok Challa ist Senior Device Engineer bei Fairchild Semiconductor und befasst sich mit der technologischen Entwicklung von Niederspannungs-Leistungs- MOSFETs. Zuvor war er Device Engineer bei National Semiconductor in Salt Lake City. Der gebürtige Inder studierte Metallurgical Engineering (Metallurgie und Werkstofftechnik) und verfügt über einen BS-Abschluss des National Institute of Technology in Warangal und einen MS-Abschluss des Indian Institute of Technology in Mumbai, beide Indien. Außerdem besitzt er einen Ph.D. in Science Engineering of Materials der Arizona State University. |

| Paul Thorup ist seit 1997 Prozessingenieur bei Fairchild Semiconductor, nachdem er 1991 in dieser Position zunächst bei National Semiconductor angefangen hatte. Sein Spezialgebiet ist die Entwicklung von Prozessen und Architekturen von Leistungs-MOSFETs. Er besitzt einen BSAbschluss der University of Utah und einen MS-Abschluss als Elektronikingenieur des Rensselaer Polytechnic Institute. paul.thorup@fairchildsemi.com |

Verwandte Artikel:

Was man wissen muss

Verlustarm mit Grabentechnik

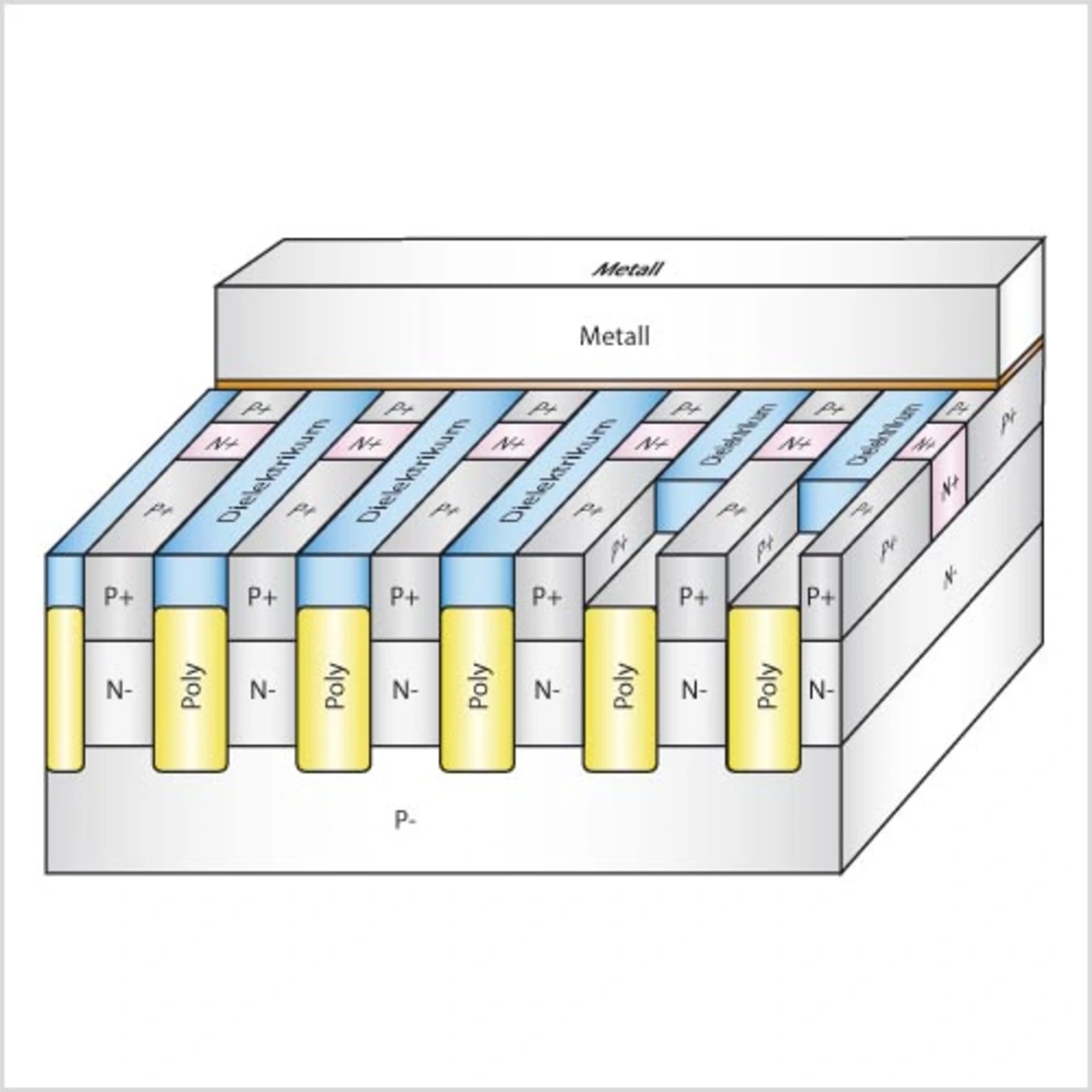

Typische Herstellungsschritte wie in Bild 3 bestehen aus geätzten „Submicron“- Trenches, denen die Gate- Oxidation folgt. Dann wird das Polysilizium aufgetragen und dotiert. Nachdem das Polysilizium unter die Siliziumfläche eingeätzt ist, folgen die Implantierung einer N-Wanne sowie eine dotierte Aufbringung des ILD (Interlevel Dielectric). Diese ILD-Ebene ist die Isolation zwischen dem Source-Metall und dem Polysilizium-Gate. Nach der ILD-Abscheidung wird die ILD-Ebene zurückgeätzt, wobei die flache Silizium-Mesafläche der Endpunkt ist. Konsequenterweise ist die ILD-Isolation planar und die normalerweise von der ILD-Schicht beanspruchte Fläche vollkommen beseitigt. In diesem neuen Verfahren werden die Kontaktdefinitionen hinsichtlich der aktiven Trench-Region selbstjustierend. Die Gate-Source- Durchbruchanforderung von ±25 V wird nunmehr durch das ILD zwischen dem Gate-Poly und dem Source-Metall garantiert, das die Spannung sicher halten kann. Die Einbettungs-Spezifikationen hängen von den Herstellungsvarianten der Gate-Poly-Vertiefung in Kombination mit der ILD-Vertiefung ab.

Der nächste Herstellungsschritt sind die P+-Source- und N+-Body-Fotoresist- Masken. Bild 4 zeigt das Streifen- Layout, wobei die Trenches senkrecht dazu verlaufen. Mit diesem Layout vermeidet man jegliche kritische Positionierung der Ebenen. Deren Größe hängt zudem nicht von der Elementegröße ab. Jedem Source- und Body-Maskenschritt folgt die N+- und P+-Implantation. Die Aktivierung der Dotierung erfolgt durch einen Fertigungsschritt mit Hitzezufuhr im Ofen. Zuletzt wird das Source-Metall aufgebracht, gefolgt von einer Abschleifung der Rückseite auf die geforderte Dicke und der Aufbringung des Drain-Metalls.

Optimierung auf Durchlasswiderstand und Spannungsnennwert

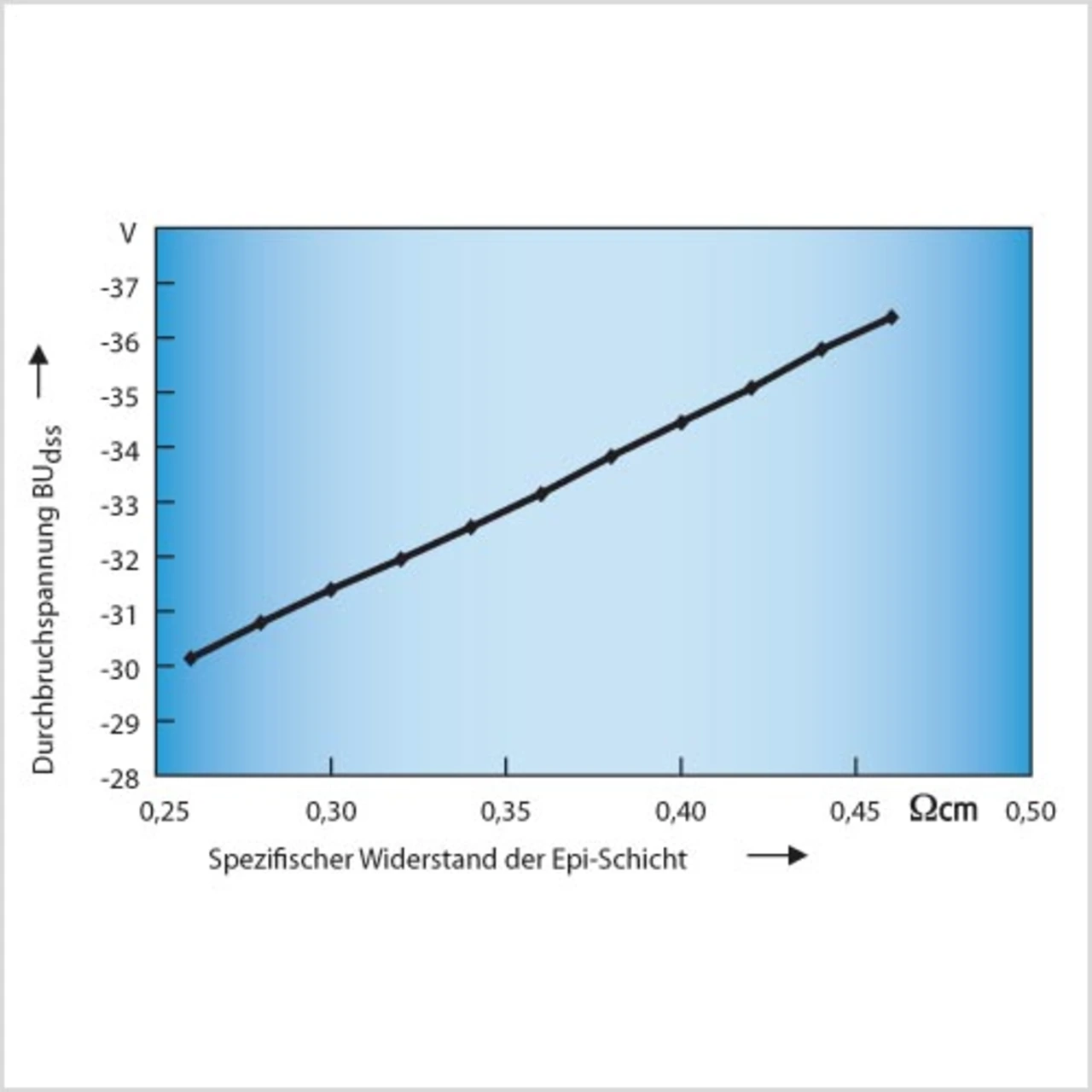

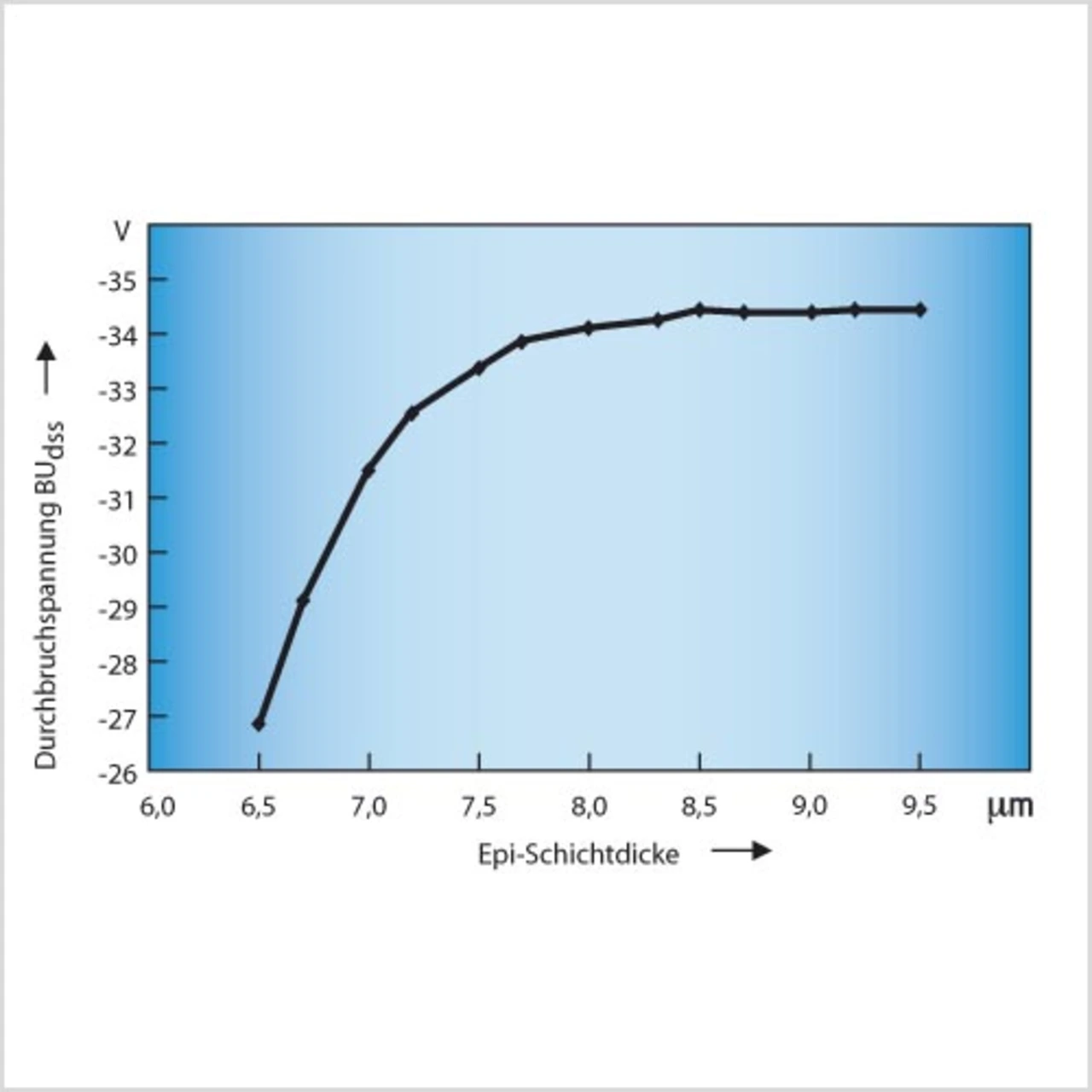

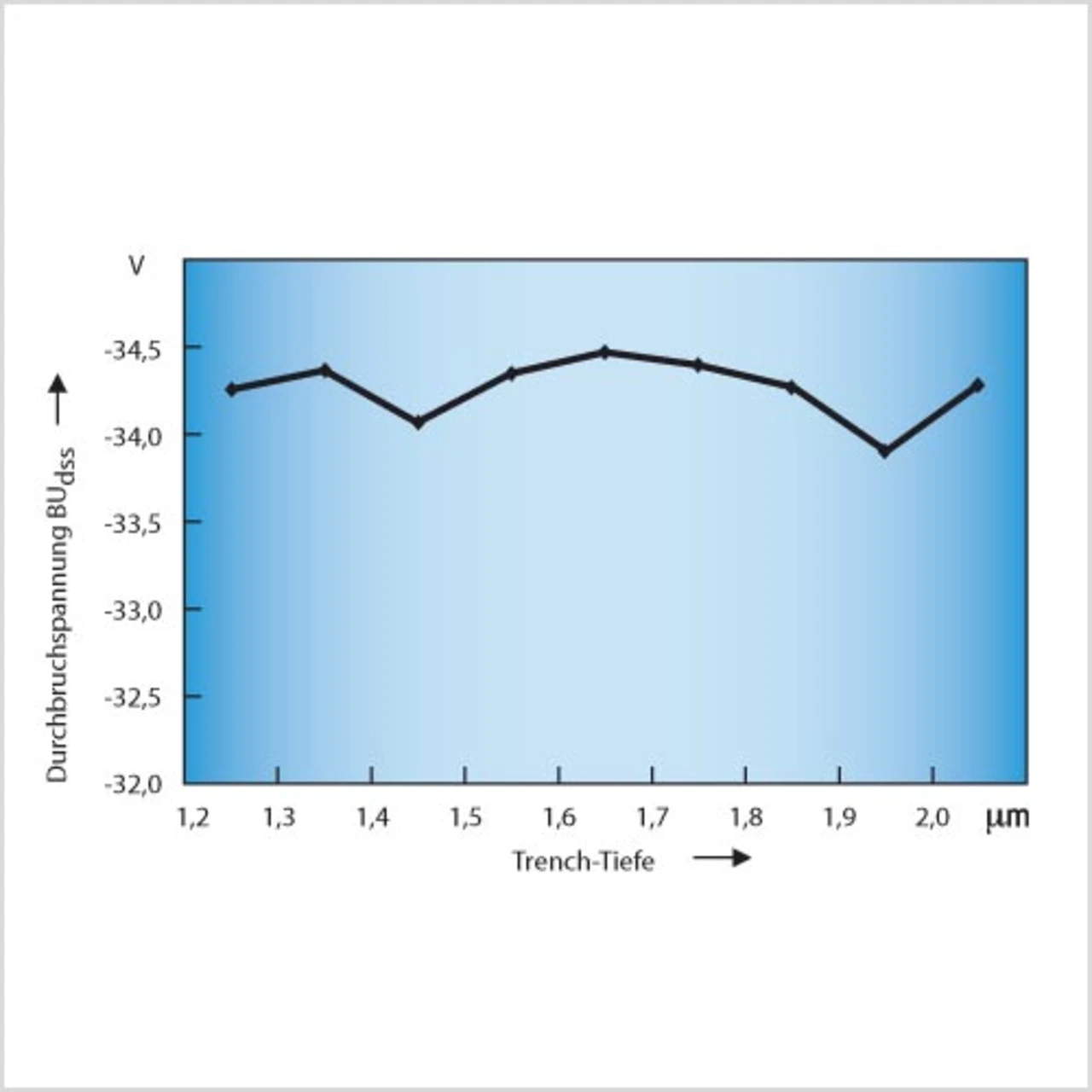

Die Optimierung des Leistungs- MOSFET erfolgte mit 2D-Simulationen, gefolgt von der Silizium- Verifikation. Als wichtiger Parameter kristallisierte sich die Abhängigkeit des Durchlasswiderstandes vom EPI-Widerstandswert sowie dessen Dicke und Trench-Tiefe heraus. Wie Bild 5 zeigt, wurde der Epi-Widerstand so gewählt, dass eine 30-V-Durchbruchgarantie auch bei typischen Variationen des Epi-Wachstumsprozesses gewährleistet bleibt. Die minimale Epi-Dicke basierte auf Simulationen gemäß Bild 6. Es ist zu erkennen, dass ein Abnehmen der Epi- Dicke unter 8 µm die Durchbruchspannung beeinflusst und ein weniger robustes Design mit sich bringt. Varianten der Trench-Tiefe (Bild 7) bei sehr unterschiedlichen Prozesszielen zeigen keinen signifikanten Einfluss auf die Durchbruchspannung (BUdss).

- Robuster 30-V-P-Kanal-Trench-MOSFET mit niedrigem Widerstand

- Robuster 30-V-P-Kanal-Trench-MOSFET mit niedrigem Widerstand

- Robuster 30-V-P-Kanal-Trench-MOSFET mit niedrigem Widerstand