Robuster 30-V-P-Kanal-Trench-MOSFET mit niedrigem Widerstand

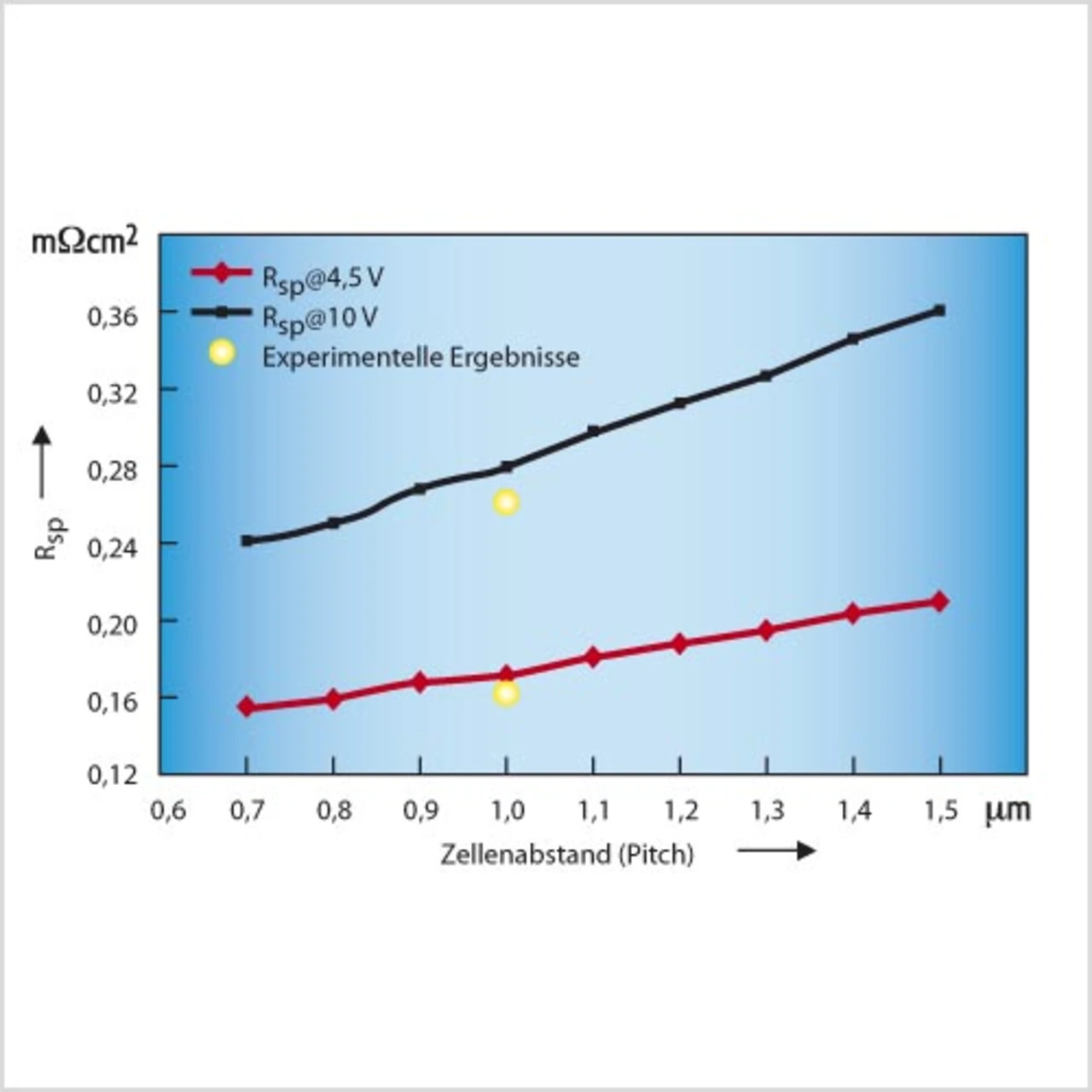

Für die neuesten tragbaren 30-V-Applikationen wurde ein neuer P-Kanal- Trench-Transistor mit einem Pitch von 1 µm entwickelt. Die neue Trench- Struktur bietet einen verbesserten Durchlasswiderstand bei trotzdem sehr guten UIS-Eigenschaften und einer ausgezeichneten Robustheit.

Für die neuesten tragbaren 30-V-Applikationen wurde ein neuer P-Kanal- Trench-Transistor mit einem Pitch von 1 µm entwickelt. Die neue Trench- Struktur bietet einen verbesserten Durchlasswiderstand bei trotzdem sehr guten UIS-Eigenschaften und einer ausgezeichneten Robustheit. Die Sperrspannung liegt bei 30 V bei einem Gatespannungs-Nennwert von 25 V und einem niedrigen spezifischen Durchlasswiderstand von nur 17 mΩmm2.

Jobangebote+ passend zum Thema

INHALT: |

Während der letzten Jahre erfreuten sich Niederspannungs- MOSFETs eines zunehmenden Interesses [1, 2]. Der Grund dafür liegt in der steigenden Zahl an tragbaren Geräten und den entsprechenden Applikationen. Gegenwärtige Untersuchnungen an „Ultra- low“-Trench-MOSFETs (Grabenstruktur) konzentrieren sich auf die Reduzierung des Bauelemente-Platzbedarfs, und zwar durch eine Vereinfachung der herkömmlichen Designspezifikationen, wie zum Beispiel des Abgleichs des kontinuierlichen N+- Body-Kontaktes mit dem Trench- Edge-Source-Kontakt. Das Grundkonzept der neuen Technologie vermeidet Designeinschränkungen und ermöglicht ein vereinfachtes Maskenlayout. Nur die Trench-Maske wird hierbei auf einem hochauflösenden Stepper erstellt, wobei alle folgenden Ebenen sich miteinander von selbst justieren.

Vereinfachtes N+-Body- Design quer zum Trench

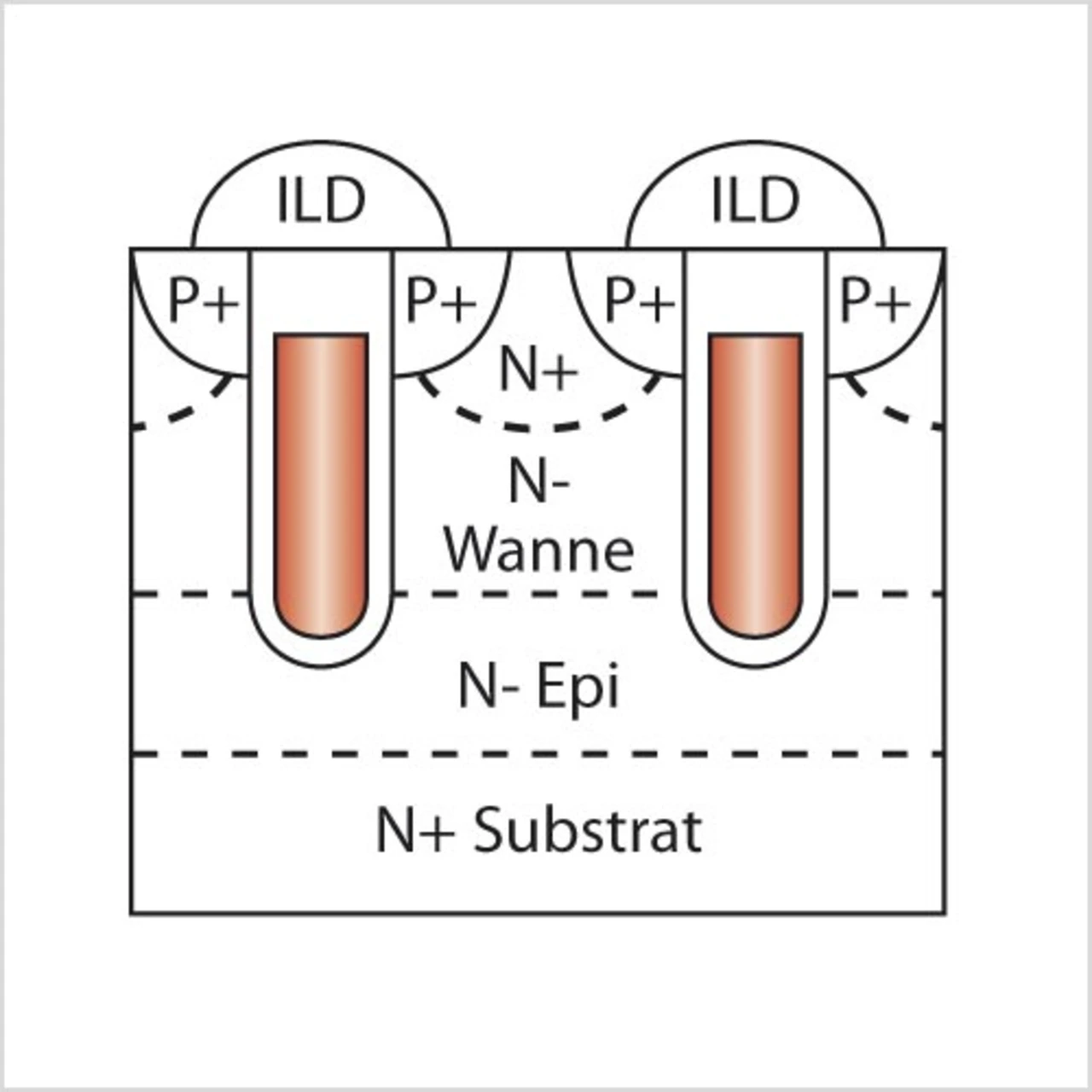

Bild 1 zeigt ein herkömmliches Design mit einer N+-Body-Maske, die mit dem Trench abgestimmt ist. Die dielektrische Isolationsebene (ILD) zwischen Source-Metall und dem Polysilizium- Gate überlagert Teilbereiche der flachen Oberfläche des P+- Source-Bereiches. Daher wird der minimale Zellenabstand der herkömmlichen, selbstabgleichenden Elementestruktur limitiert durch den Kontaktabstand der Oberflächen-ILD-Ebene sowie durch die Möglichkeit, kleine Bereiche der N+-Body- und P+- Source-Bereiche abzubilden und zu justieren. Dieser Nachteil lässt sich durch einen speziellen Bauelemente- Aufbau umgehen (Bild 2).

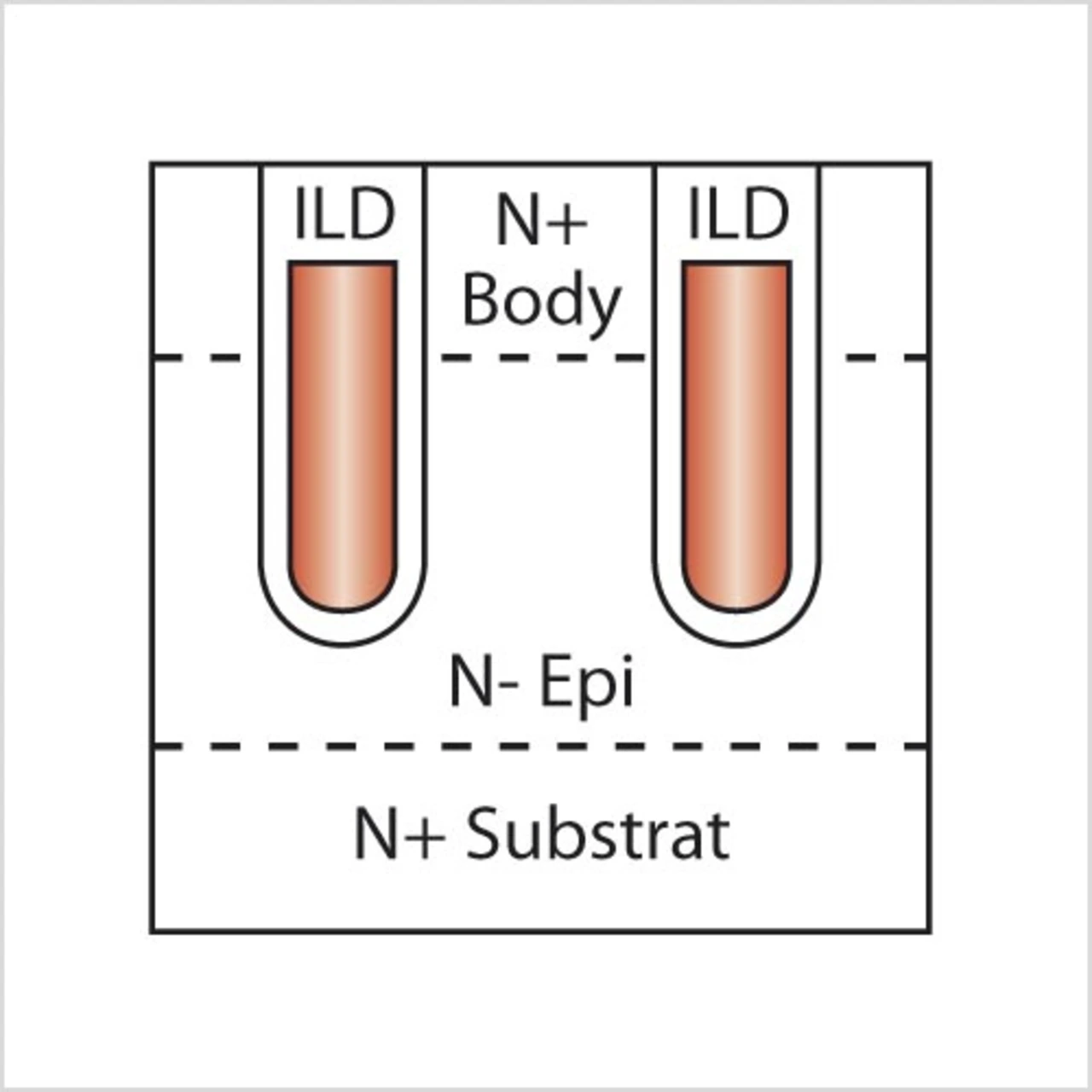

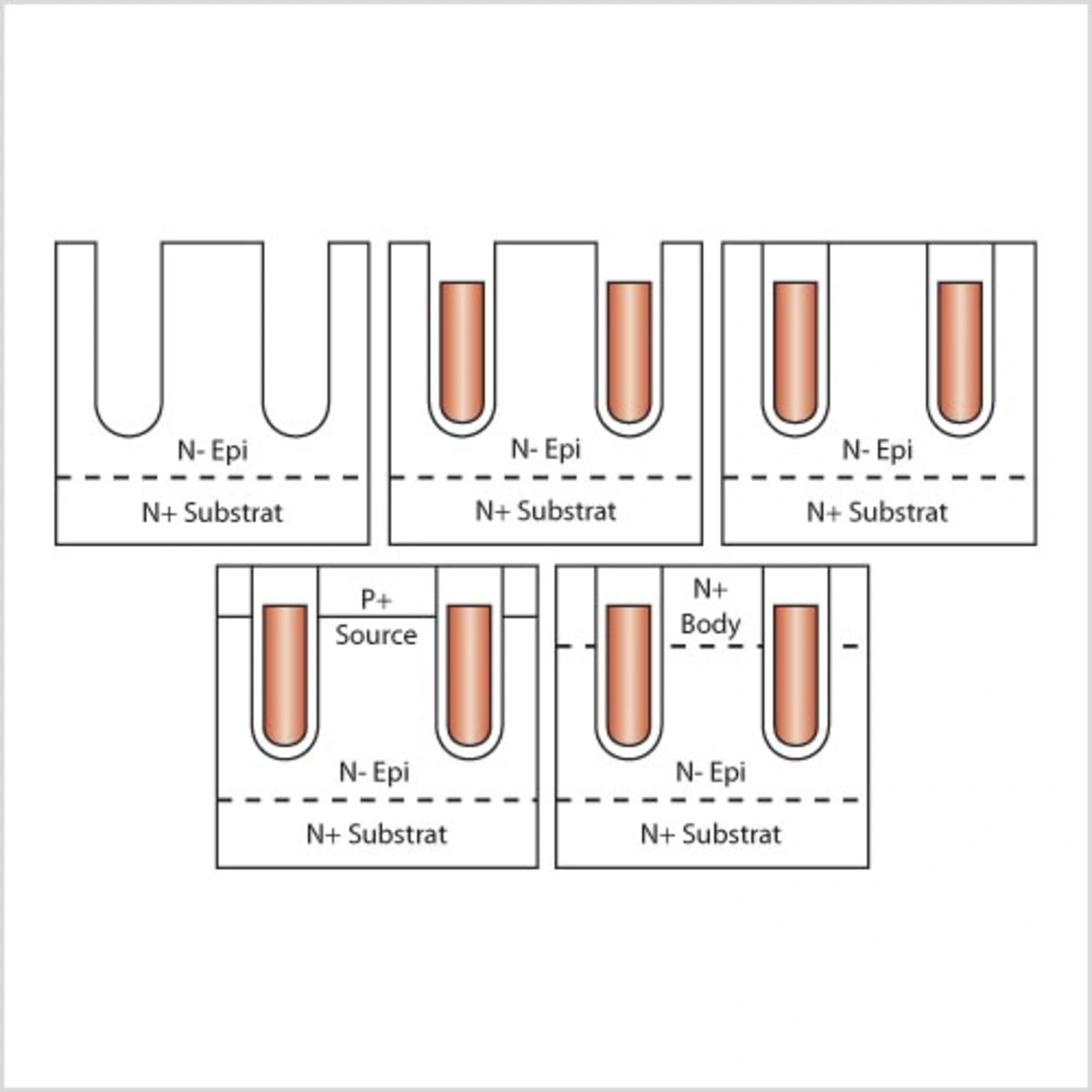

Bei dieser neuartigen Bauelementestruktur wird das Polysilizium-Gate ausreichend tief in den Trench hinein verlagert, um der ILD-Füllung genügend Raum zu geben. Die Poly-Einbettungstiefe und die damit abhängige ILD-Dicke werden durch die angestrebte maximale Gate/ Source-Nennspannung bestimmt. Dieses Design-Element erlaubt ein vereinfachtes N+-Body-Design, das quer zum Trench erzeugt wird (Bild 3) und damit nicht länger die minimale Elementegröße beeinflusst. Mit diesem Prozess wurden experimentelle Bauelemente mit variierenden Strukturgrößen von 0,8 bis 1 µm hergestellt.

Realisiert wird das hochdichte Trench-Design durch die Schaffung eines N+-Body-Kontaktes, der quer angeordnet und dabei unkritisch bezüglich der Justierung ist. Im Gegensatz dazu steht der herkömmliche kontinuierliche Kontakt in der Mesa-Mitte.

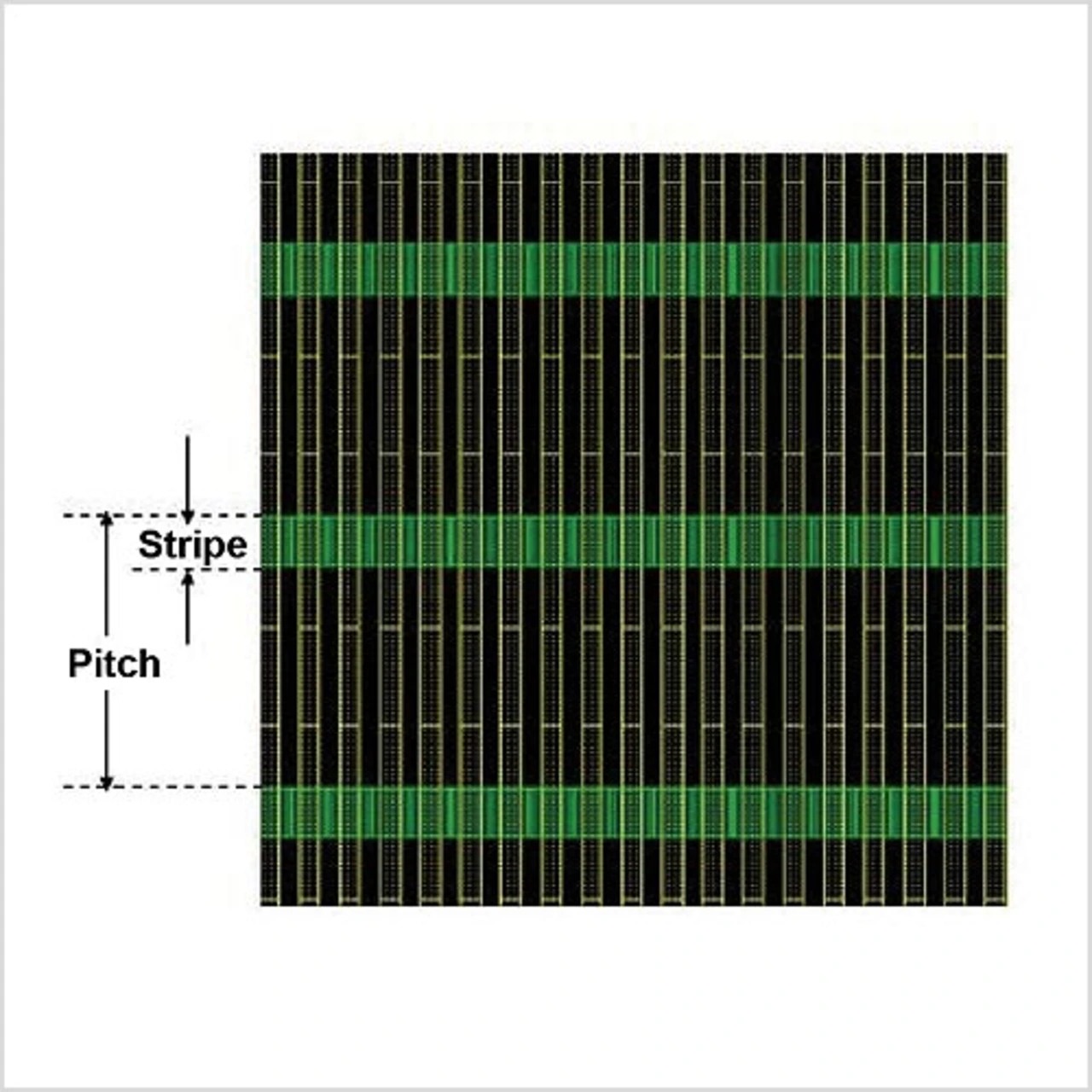

Dieses sich wiederholende Streifendesign wurde optimiert, um eine robuste Lawinenenergie-Festigkeit aufweisen zu können. Die wichtigsten Variablen waren die N+-Body-Tiefe, die Breite der Streifen und der sich wiederholende Abstand (Pitch). Bild 9 zeigt diese Definitionen grafisch auf.

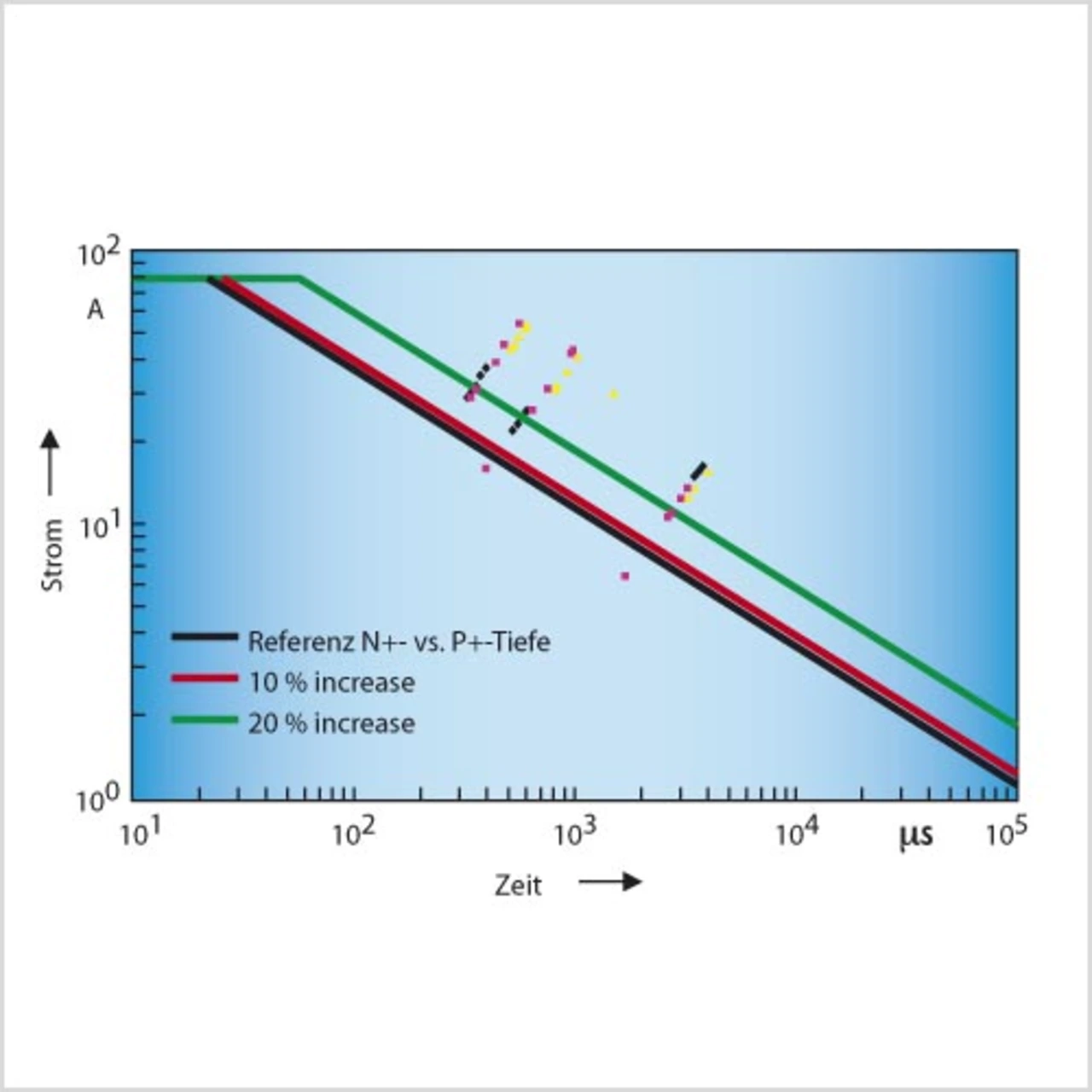

Bild 10 zeigt die UIS-Leistung (Unclamped Inductive Switching) bei drei unterschiedlichen Induktivitätswerten (0,5, 1 und 10 mH) für unterschiedliche Tiefen des N+-Body bezogen auf die P+-Source. Während dieses Tests werden die Transistoren bis zum Ausfall getrieben; die entsprechenden maximalen Stromwerte wurden aufgezeichnet. Es ist zu erkennen, dass eine signifikante Verbesserung im UIS-Pegel bei tieferen N+-Body- Designs vorherrscht, und zwar bei gleichen N+-Streifen-Breiten und -Abständen.

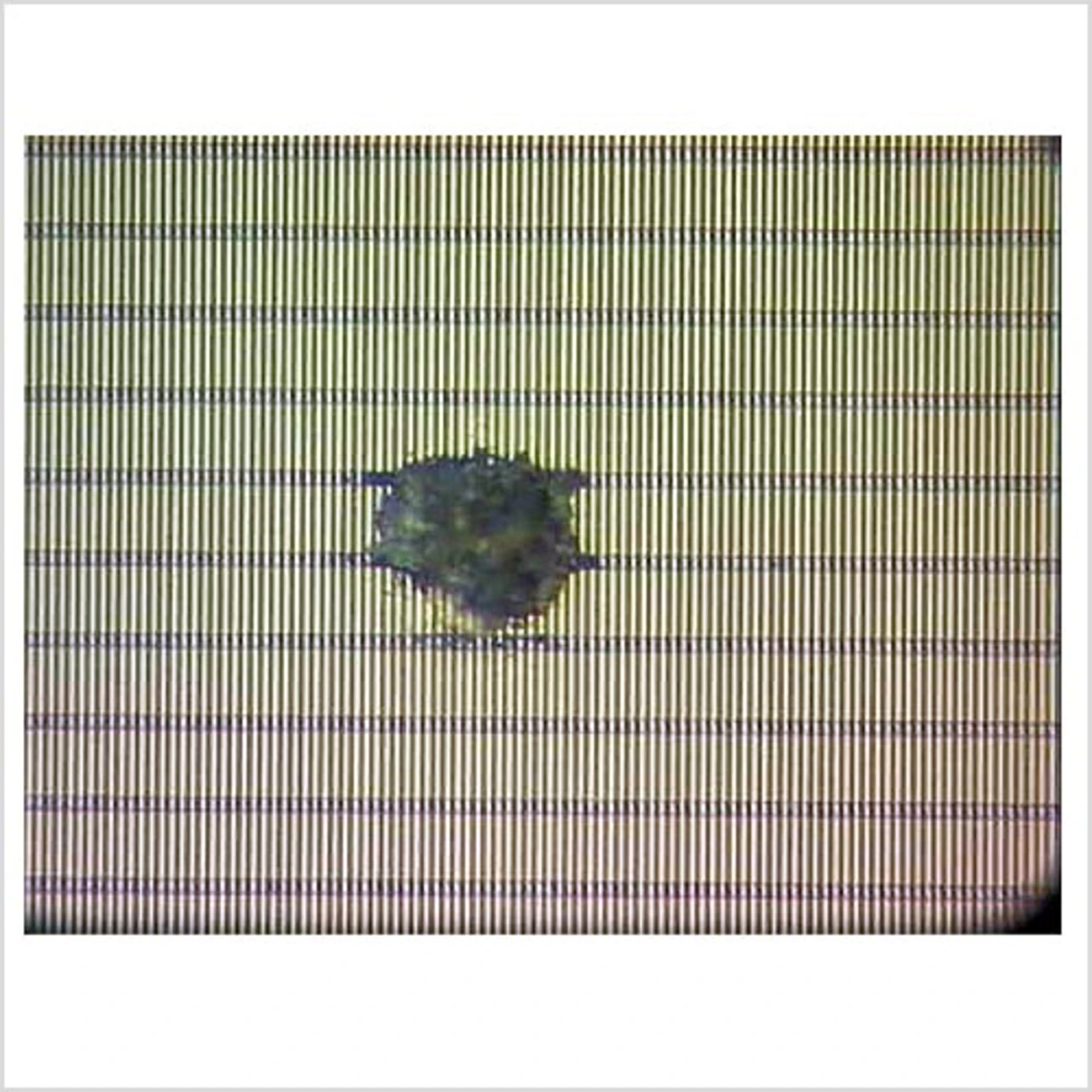

Im nächsten Schritt wurden die Breite und der Abstand des N+-Body untersucht. Dabei kamen sehr unterschiedliche sich wiederholende Abstände zum Einsatz, und zwar von 40 µm bis hinunter zu 4 µm. Bei Abständen von mehr als 20 µm ergab sich nur eine geringe Stromtragfähigkeit. Es war klar erkennbar, dass alle Fehler die gleiche Handschrift aufwiesen (Bild 11).

- Robuster 30-V-P-Kanal-Trench-MOSFET mit niedrigem Widerstand

- Robuster 30-V-P-Kanal-Trench-MOSFET mit niedrigem Widerstand

- Robuster 30-V-P-Kanal-Trench-MOSFET mit niedrigem Widerstand