Das Temperaturverhalten von Power-FETs bei Rückschlagpulsen

Fortsetzung des Artikels von Teil 3

Das Temperaturverhalten von Power-FETs bei Rückschlagpulsen

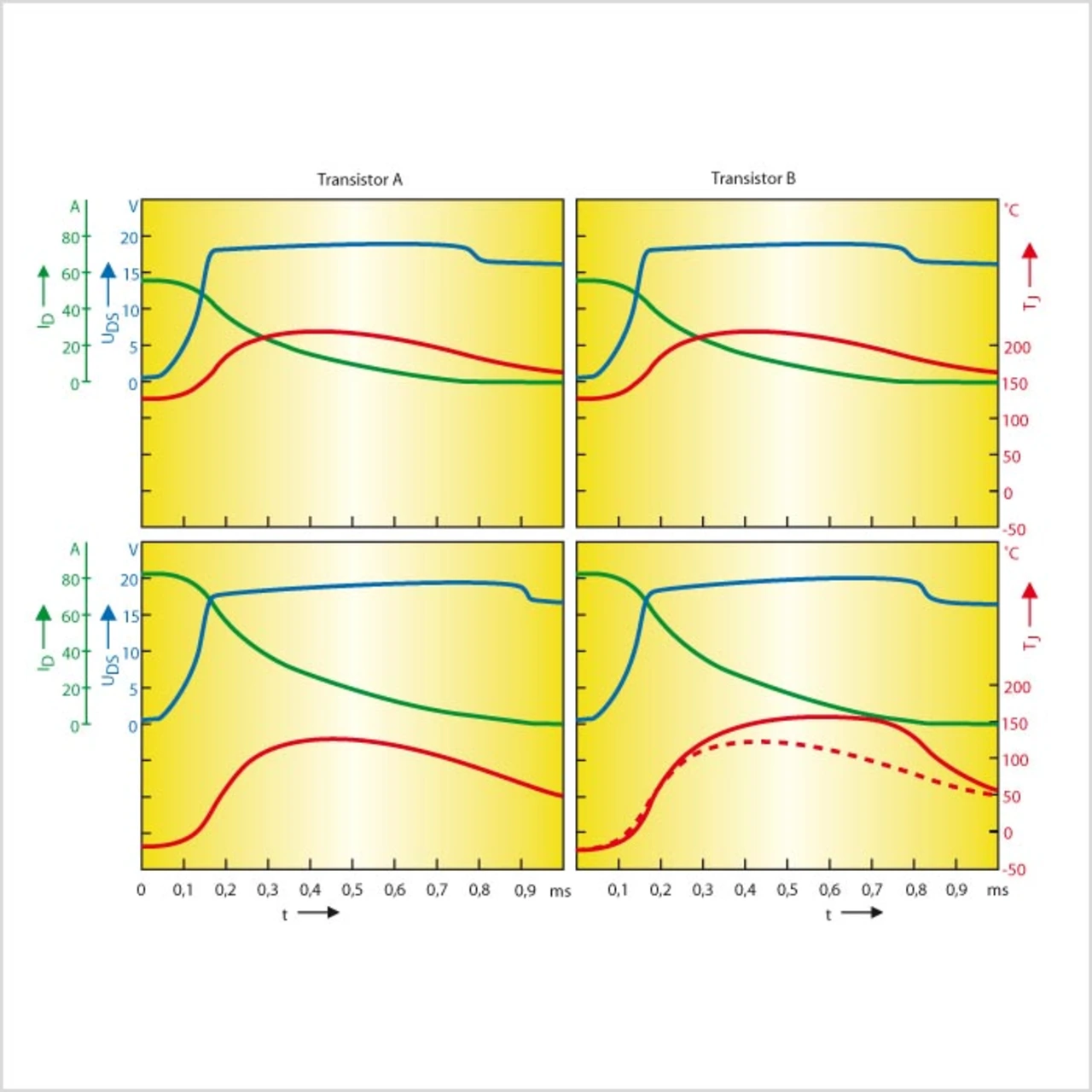

Ist der Transistor im ohmschen Bereich noch voll eingeschaltet, wird es Zellen geben, die – wenn auch geringfügig – etwas mehr Strom tragen. Ein Grund hierfür könnte sein, dass diese sich in der Nähe der Bondkontakte befinden. Sobald der Transistor beim Abschaltvorgang in den Linearbereich geht, werden diese Zellen rasch heißer, weil dann die Drain-Source-Spannung und somit die Verlustleistung ansteigt. Erhöht sich die Temperatur dieser Zellen, wird die Stromdichte in diesen aufgrund der positiven Temperaturdrift des Drainstroms nochmals zunehmen. Es ergibt sich also ein mitkoppelnder Effekt. Kann die thermische Anbindung des Siliziums nicht mehr ausreichend entgegenwirken, so kommt es zu einer inhomogenen Stromverteilung auf dem Silizium. Schlimmstenfalls kann dies zum thermischen Davonlaufen und somit zur Bauteilzerstörung führen. Bild 3 zeigt den Temperaturverlauf in der Sperrschicht während des Rückschlagpulses.

Jobangebote+ passend zum Thema

Verhalten sich beide Transistoren bei hohen Umgebungstemperaturen noch gleich, kommt es bei niedrigen Umgebungstemperaturen zu einem deutlichen Unterschied. Der höhere Strom und die längeren Verweilzeiten im Linearbereich müssen zu einer ausgeprägten Bildung von „Hot Spots“ in Transistor B (in Bild 3 rechts) geführt haben. Ein weiteres, auch nur geringfügiges Absinken der Umgebungstemperatur könnte deshalb zur Bauteilzerstörung führen.

Die gestrichelte Linie im unteren, rechten Teil von Bild 3 zeigt für Transistor B den Temperaturverlauf in der Sperrschicht, den man bei niedrigen Umgebungstemperaturen unter der Annahme erwarten würde, dass sich dieser Transistor hier genauso verhält wie bei hohen Umgebungstemperaturen. Wie zu sehen ist, gibt es einen signifikanten Unterschied zum tatsächlich gemessenen Verlauf aufgrund der ausgeprägten Bildung von „Hot Spots“. Das ist ein klares Indiz dafür, dass das Temperaturverhalten eines Transistors stark vom jeweiligen Transistorarbeitspunkt abhängt. Aus diesem Grunde kann eine Simulation zu keinem aussagekräftigen Resultat führen.

- Das Temperaturverhalten von Power-FETs bei Rückschlagpulsen

- Schlussfolgerungen

- Das Temperaturverhalten von Power-FETs bei Rückschlagpulsen

- Das Temperaturverhalten von Power-FETs bei Rückschlagpulsen