Das Temperaturverhalten von Power-FETs bei Rückschlagpulsen

Fortsetzung des Artikels von Teil 1

Schlussfolgerungen

Bis vor nicht allzu langer Zeit waren die Chipabmessungen das einzige Kriterium bei der Auswahl von Power-FETs in Applikationen, in denen energiereiche Rückschlagpulse absorbiert werden müssen. Dieser Artikel zeigt, dass inzwischen wegen der zunehmenden Zelldichte eine vorsichtigere Auswahl von Silizium- und Gehäusetechnologie notwendig geworden ist. Die ungünstigste Rahmenbedingung, auf die das Bauteil ausgelegt sein muss, ist der Rückschlagpuls bei tiefen Temperaturen nach der spezifizierten Anzahl von Temperaturzyklen.

Jobangebote+ passend zum Thema

Die Untersuchungen legen auch nahe, dass die absoluten Grenzdaten (Absolute Maximum Rating) des Datenblattes nicht missachtet werden dürfen. Denn das Überschreiten des sicheren Betriebsbereichs mag bei wenigen, fabrikneuen Bauteilen in der heißen Temperaturkammer im Labor gutgehen. Doch bei hohen Stückzahlen, nach einigen Temperaturzyklen und bei realen Umweltbedingungen riskiert man eine hohe Ausfallrate im Feld.

Abschließend ist zu erwähnen, dass Schaltbetriebs-Anwendungen das klassische Einsatzgebiet von Power-FETs sind. Arbeiten sie im ohmschen Bereich bei guter thermischer Stabilität und haben sie eine gute thermische DC-Anbindung, so sind sie doch nicht darauf ausgelegt, Rückschlagpulse zu absorbieren. Vermutlich wird man deswegen zunächst daran denken, den Rückschlagpuls zu vermeiden, indem man eine Freilaufdiode parallel zum Aktor platziert. Doch dies würde zu einer höheren EMV-Emission führen und die Verpolsicherheit der Schaltung zunichte machen.

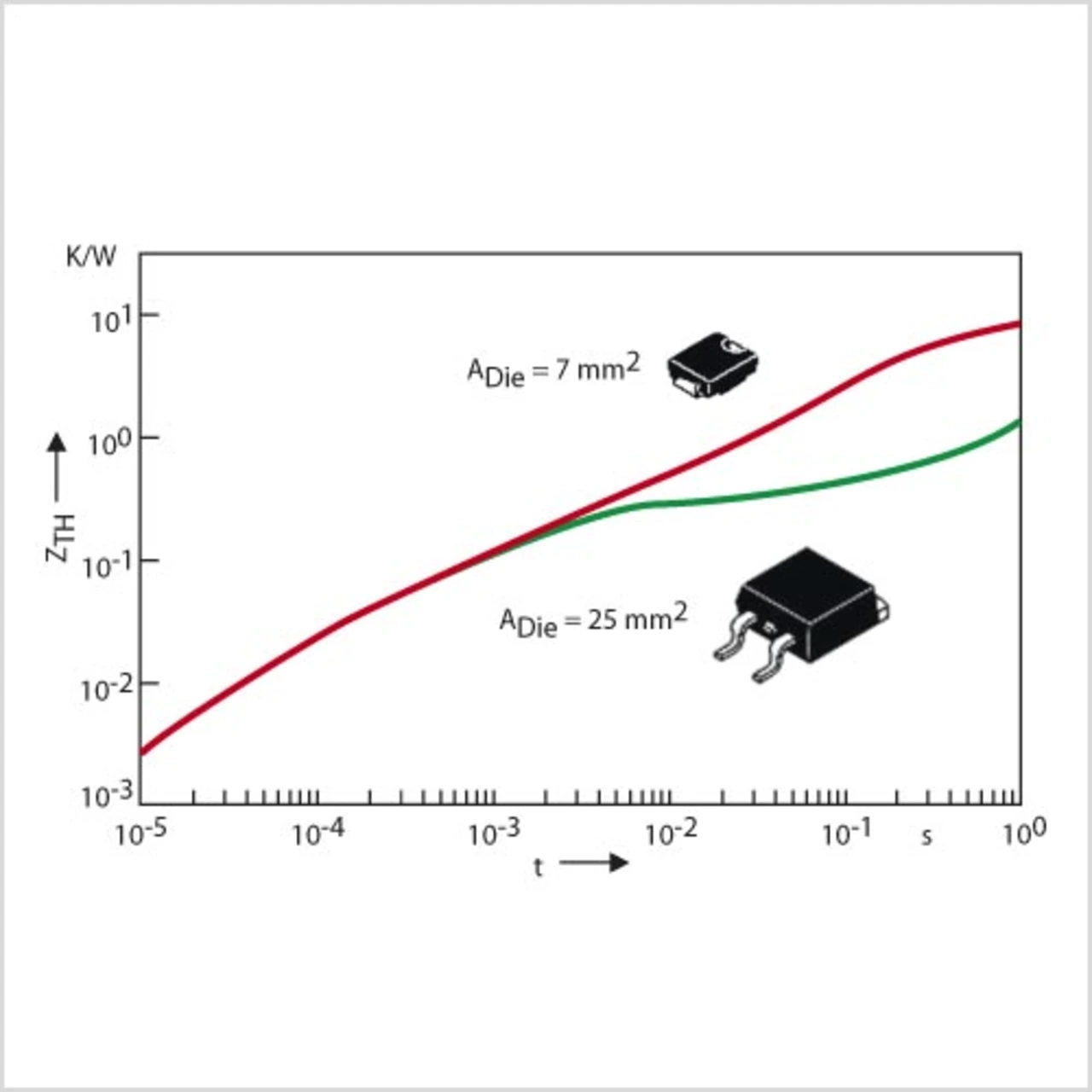

Aus Bild 5 geht hervor, dass es eine interessante Alternative gibt. Der Vergleich der transienten thermischen Widerstände zeigt, dass eine kleine SMC-Löschdiode die gleiche Pulsbelastbarkeit hat wie ein großer D2Pack-Power-FET. Eine solche Diode parallel zum Power-FET könnte energiereiche Rückschlagpulse aufnehmen: Ohne dass die Vorteile der Schaltung verlorengingen, vereinfachte sich die Transistorauswahl erheblich. Sogar die Chipgeometrien würden keine Rolle mehr spielen. Das heißt: Ohne ihre Robustheit zu beeinträchtigen, könnte der Kostenaufwand für die Schaltung reduziert werden. fr

| Dipl.-Ing. Matthias Goecke studierte Elektrotechnik in Erlangen. 2000 trat er der TEMIC Telefunken microelectronic GmbH (seit 2001 Teil des Continental Konzerns) in Ingolstadt als Hardware-Entwickler bei. Zu seinem Aufgabenbereich zählten Baugruppenqualifikationen sowie EMV- und Ausfallanalysen. Heute arbeitet er bei der Continental in Yokohama, Japan. Matthias.Goecke@jp.contiautomotive.com |

Auch das Gehäuse muss noch betrachtet werden. Durch Temperaturzyklen können das Chiplot und die Bondkontakte ermüden, was zu einer ernsthaften Beeinträchtigung der thermischen Belastbarkeit des gesamten Bauteils führen kann. Aus diesem Grunde haben viele Hersteller eine hohe Sicherheitsmarge bei der Spezifikation des thermischen Widerstandes. Momentan gibt es nur wenige Hersteller, die Leistungstransistoren in einem wirklich robusten SMD-Gehäuse anbieten können.

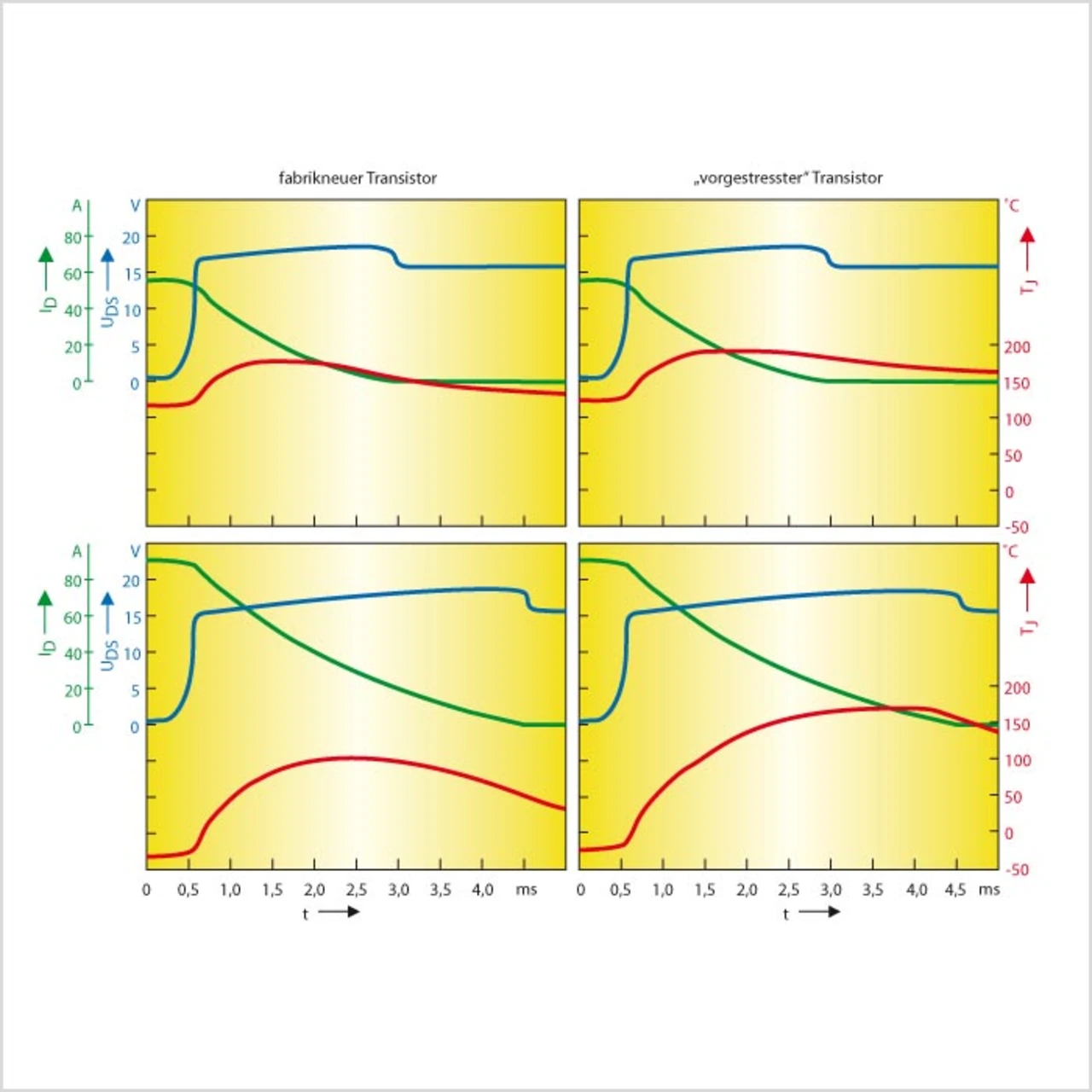

Bild 4 zeigt eine Vergleichsmessung zweier Transistoren gleichen Typs. Der eine ist fabrikneu, der nur dem Stress während des Lötprozesses ausgesetzt wurde. Der andere Transistor wurde zusätzlich noch mit 1000 Temperaturzyklen gestresst. Im Gegensatz zu Bild 3 wurde diesmal eine Last mit einem höheren Induktivitätswert verwendet. Des weiteren ist die Siliziumfläche der Transistoren größer.

- Das Temperaturverhalten von Power-FETs bei Rückschlagpulsen

- Schlussfolgerungen

- Das Temperaturverhalten von Power-FETs bei Rückschlagpulsen

- Das Temperaturverhalten von Power-FETs bei Rückschlagpulsen