Auswahl des richtigen FPGA für unterschiedliche Anwendungsfälle

Keine Angst vor parallelen Schnittstellen

Fortsetzung des Artikels von Teil 4

Realisierung von parallelen Schnittstellen

Um auf der Empfängerseite die Daten zu empfangen, stehen folgende Möglichkeiten zur Verfügung:

Verschiebung der Daten gegenüber dem Takt

Jobangebote+ passend zum Thema

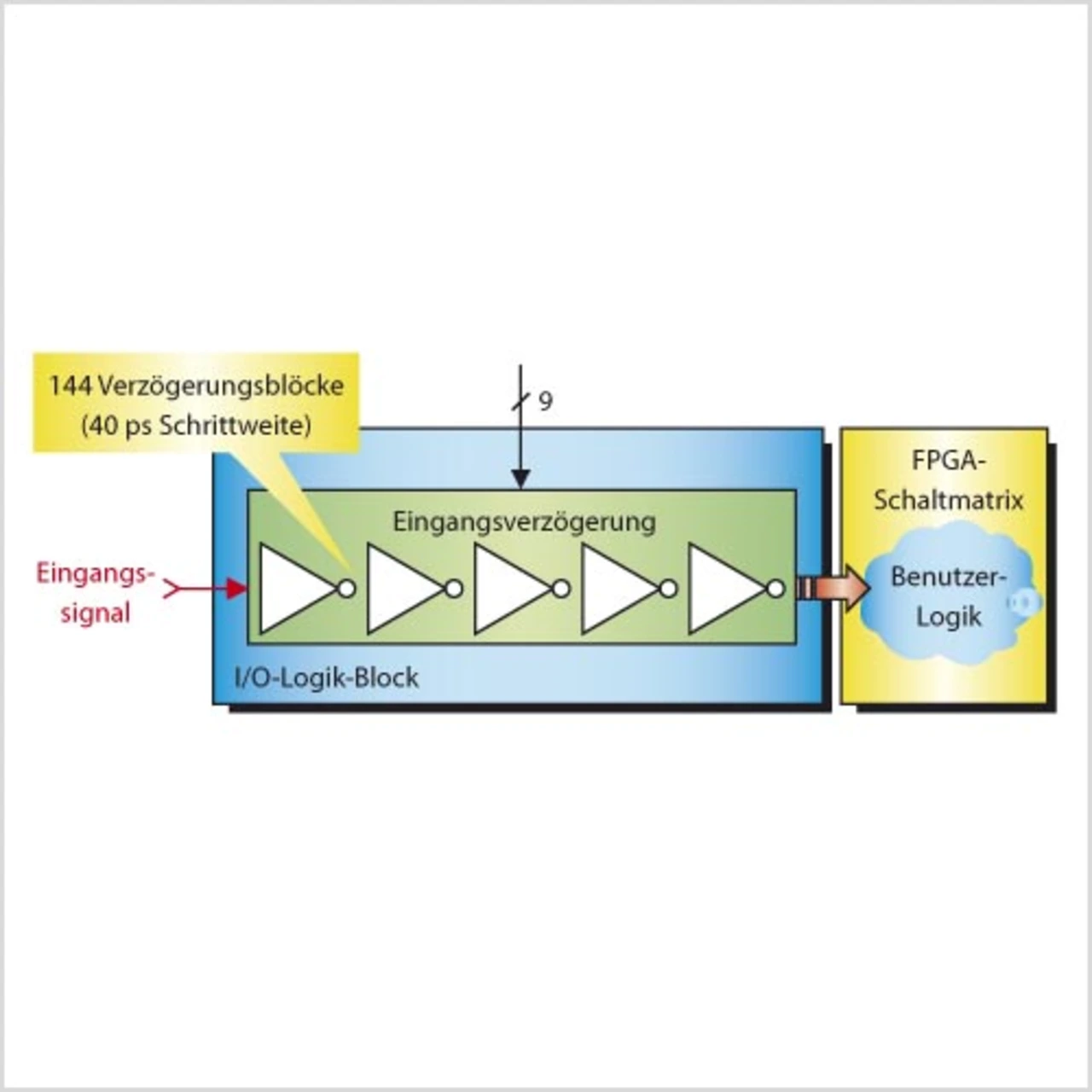

Bei der festen Verzögerung der Daten (Bild 1) können die Daten gegenüber dem Takt bei der SCM-Familie mittels 144 kleiner Blöcke in 40-ps-Schritten und bei der ECP2/M-Familie mittels 16 Blöcken verzögert werden.

Dieses Vorgehen ist bis maximal 300 Mbit/s sinnvoll. Der Vorteil liegt in der einfachen Implementierung, der Nachteil besteht darin, dass dieses System keine Rücksicht auf Temperatur- bzw. Spannungsschwankungen nimmt. Der Verzögerungswert (z.B. 2,5 ns) wird einmal vergeben und nicht mehr verändert.

Eine bessere Lösung wäre hier die Verwendung einer Schaltung mit Rückführung, um die Verzögerungselemente dynamisch je nach Anforderung nachziehen zu können. Das Ergebnis ist eine sichere Schnittstelle bezüglich Temperatur- und Spannungsschwankungen.

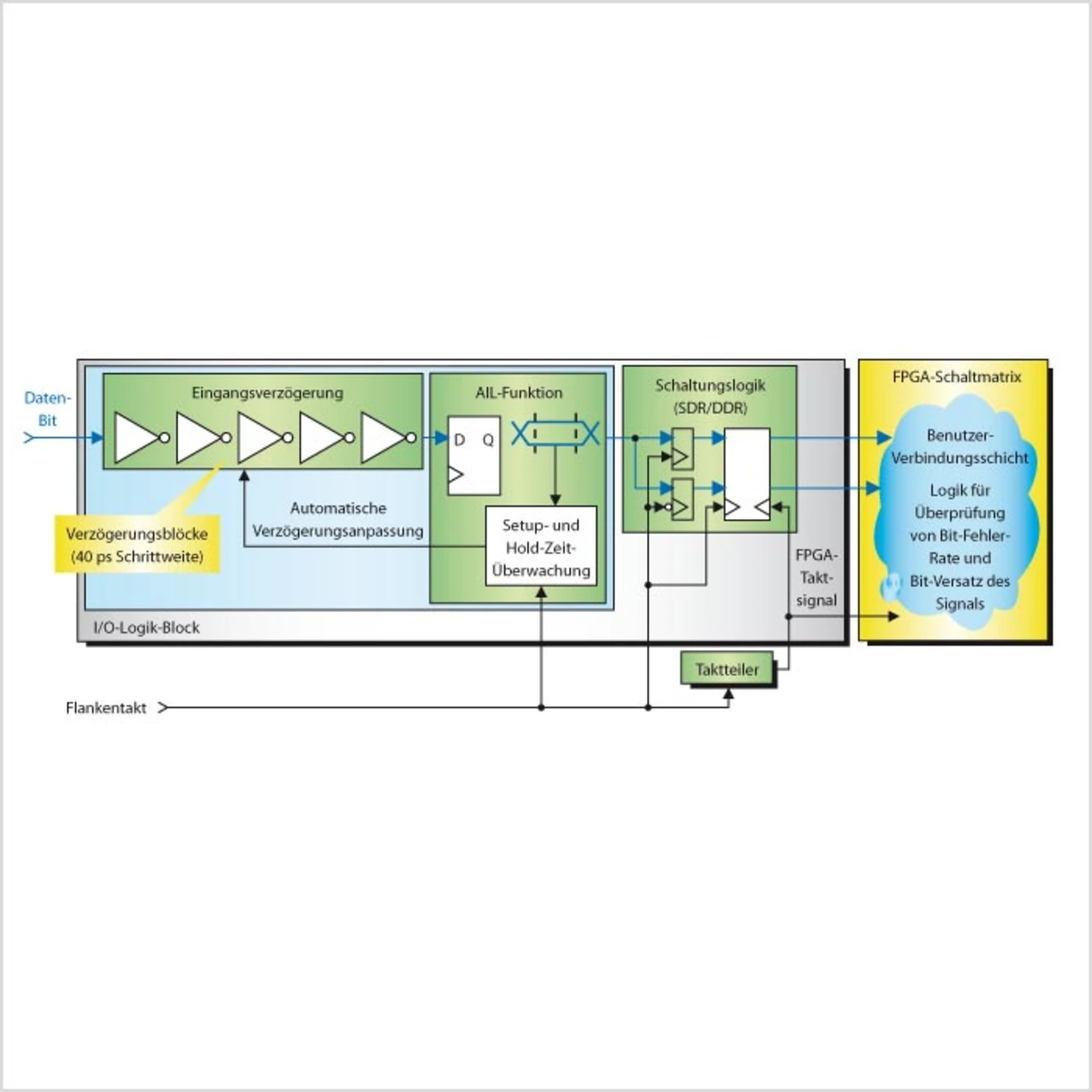

Bei der dynamischen Verzögerung der Daten (Bild 2) kann jedes Datenelement unabhängig voneinander verzögert werden, damit die Daten sicher übernommen werden können. Hierbei lassen sich auch Laufzeit-Unterschiede ausgleichen, die durch unterschiedliches Verlegen der Leitungen auf der Leiterplatte entstehen. Diese Methode kann für Datenraten bis zu 2 Gbit/s verwendet werden. Um dies zu realisieren, benötigt jeder Dateneingang die Eingangsverzögerungen sowie die so genannte AIL-Funktion (Adaptive Input Logic). Sie sorgt dafür, das bei jeder Flanke die Verzögerungselemente nachgezogen werden.

Damit dieses System stabil läuft, benötigt die AIL-Funktion 32 Übergänge, um einen stabilen Startwert zu ermitteln, danach ist keine Mindestanzahl an Signalübergängen (Wechsel von „1“ auf „0“ oder umgekehrt) mehr nötig. Da diese Funktion sehr aufwendig ist, wird sie nur in High-End-FPGAs angeboten. Die Lattice-SCM-Familie bietet die AIL-Funktion als einzige auf dem Markt mit bis zu 2 Gbit/s an. Das Einstellen der AIL erfolgt sehr einfach mit dem in der Design-Software ispLEVER implementierten IPexpress-Modul-Generator (Bild 3). Hier kann man das Fenster für die Daten spezifizieren. AIL stellt sicher, dass die Signale, die in diesem Fenster liegen, mehr oder weniger verzögert werden.

Das Hauptanwendungsgebiet dieser seriellen Datenübertragung ist meist die Verbindung über eine Busplatine (Backplane) oder ein Kabel, z.B. PCIExpress, Ethernet, XAUI (10 Gbit Attachment Unit Interface), CPRI, OPSAI, FibreChannel, Serial RapidI/O und SATA. Zur Kommunikation zwischen den Bausteinen auf der Platine sind heute immer noch parallele Bussysteme im Einsatz. Deren Vorteil liegt in der kürzeren Latenzzeit und der Tatsache, dass keine Codierung und keine Taktrückgewinnung notwendig sind.

Um hohe Datenraten über diese parallelen Systeme zu übertragen, kann entweder die Busbreite erweitert oder die Taktrate erhöht werden. Heute werden parallele Systeme bis zu Übertragungsraten von 2 Gbit/s angewendet, d.h., bei einem System, in dem beide Taktflanken benutzt werden, ist ein Takt von 1 GHz notwendig, um mit 2 Gbit/s Daten übertragen zu können. Wie bei jedem parallelen System müssen die Daten parallel sowie zusätzlich ein Takt übertragen werden. Hierbei sind meist die Daten und der Takt phasengleich, d.h., Takt und Daten wechseln zur gleichen Zeit.

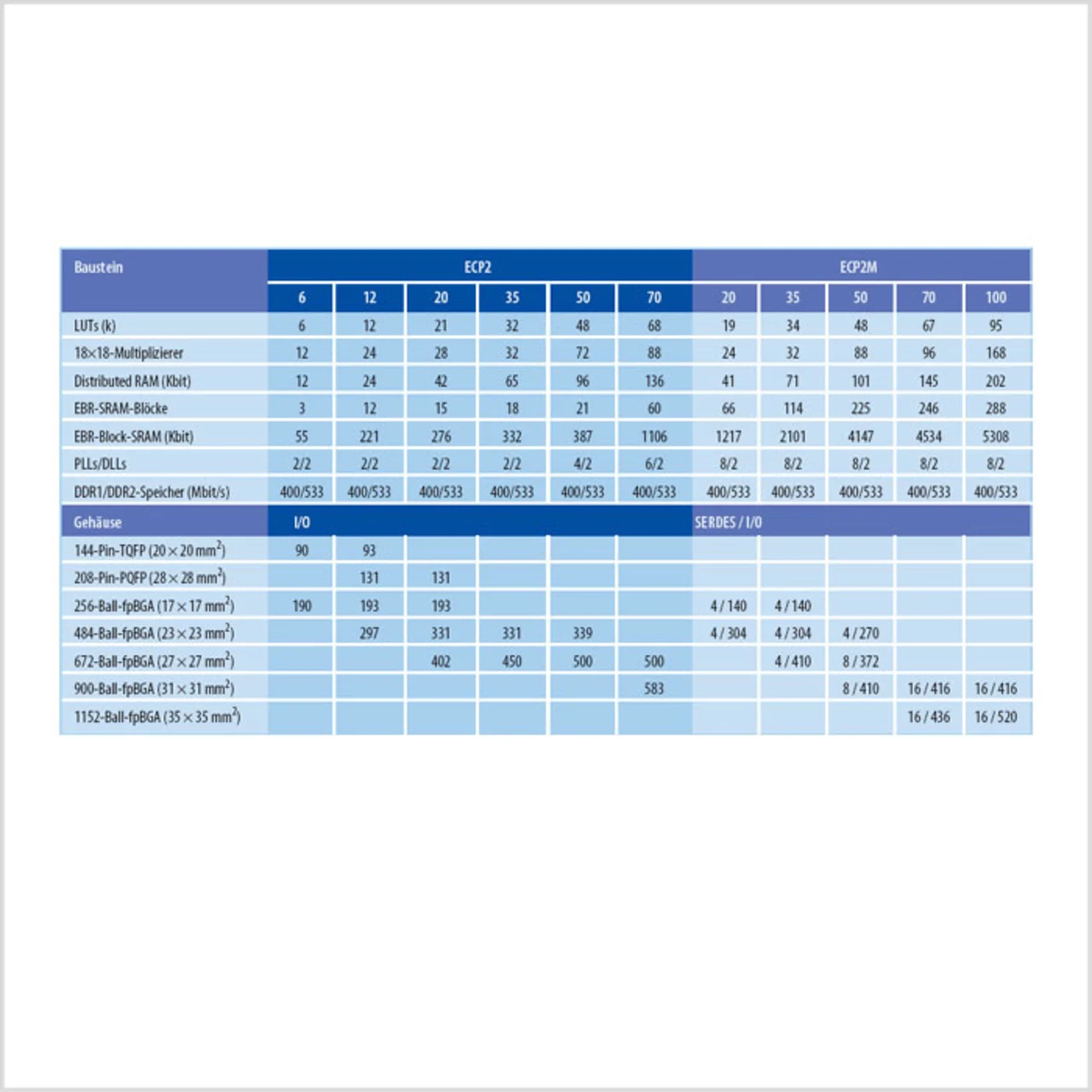

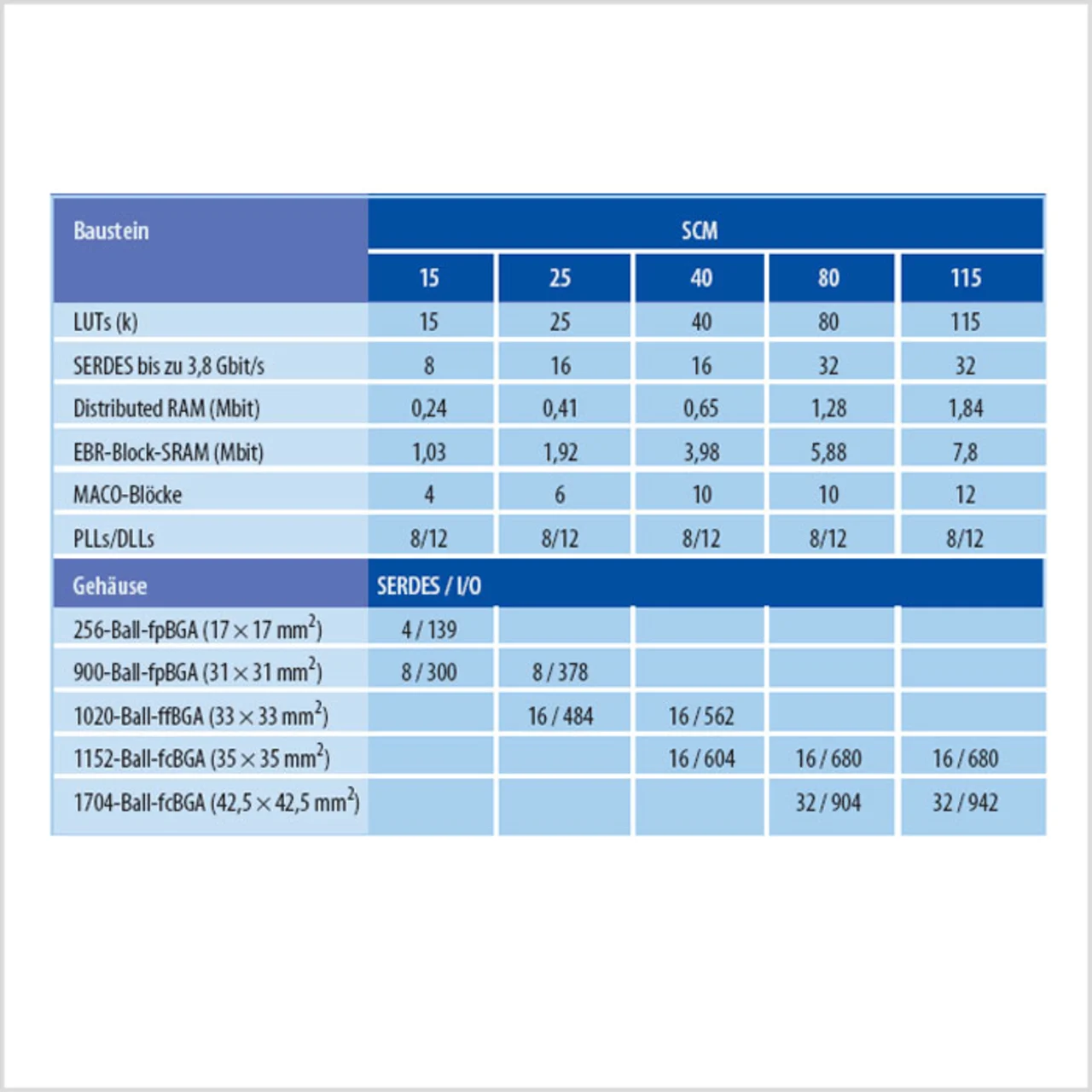

Für die Empfängerseite ist dies nicht ideal, da hierbei die Daten nicht direkt mit dem Takt übernommen werden können. Dazu muss der Takt verschoben werden, um die Setup&Hold-Zeiten zu erfüllen. Weiterhin ist bei parallelen Systemen ein gewisser Versatz (Skew) zwischen den Datenleitungen zu erwarten, der auf der Empfängerseite berücksichtigt werden muss. Dieser Datenversatz ist bedingt durch die etwas unterschiedliche Leitungsführung auf der Leiterplatte. Lattice hat zur Bedienung serieller oder paralleler Schnittstellen Low-Cost-ECP2/M-FPGAs und High-End-SCM-FPGAs im Programm. Einen kurzen Überblick über beide Familien geben Tabelle 1 und Tabelle 2.

- Keine Angst vor parallelen Schnittstellen

- Literatur

- Keine Angst vor parallelen Schnittstellen

- Keine Angst vor parallelen Schnittstellen

- Realisierung von parallelen Schnittstellen