Auswahl des richtigen FPGA für unterschiedliche Anwendungsfälle

Keine Angst vor parallelen Schnittstellen

Fortsetzung des Artikels von Teil 3

Keine Angst vor parallelen Schnittstellen

Taktverzögerung gegenüber den Daten

Jobangebote+ passend zum Thema

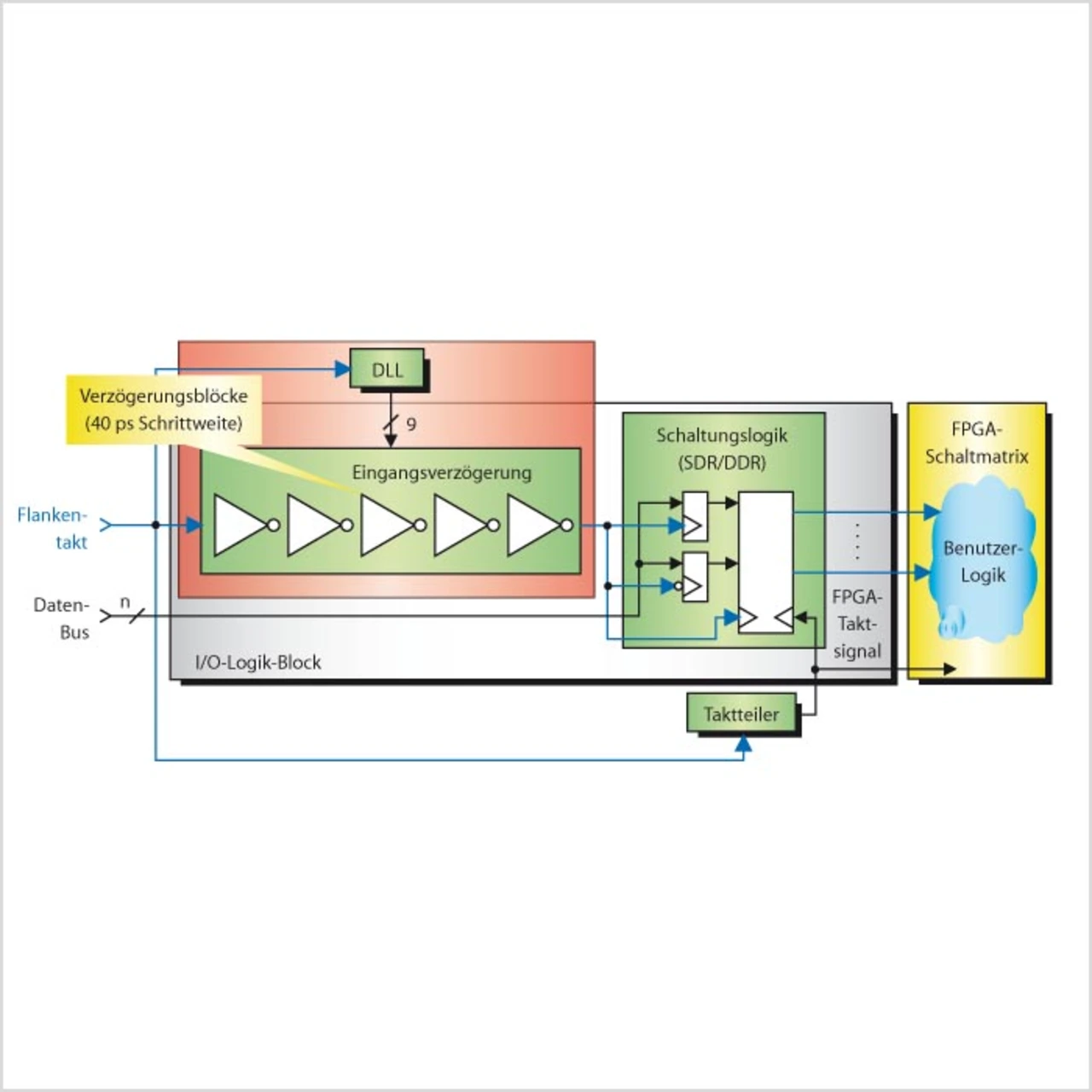

Eine einfachere Lösung, die über Temperatur und Spannung stabil läuft, ist der Ansatz, nicht die Daten, sondern den Takt zu verschieben. Dieses Vorgehen wird zum Beispiel bei den DDR1/2-Speicher-Schnittstellen benutzt. Hier werden nicht die Daten verschoben, sondern der Takt wird um 90 Grad gegenüber den Daten verzögert (Bild 4). Durch die DLL (Delay Locked Loop) ist diese Verzögerung konstant über Temperatur und Spannung. Diese Funktion wird nicht an allen Eingängen, sondern nur an den Takteingängen benötigt. Somit kann diese Methode auch in Low-Cost-FPGAs angewendet werden, da die zusätzlichen Funktionen nur wenig Silizium-Fläche benötigen.

In diesem Beispiel wird die Verzögerung über eine DLL nachgezogen. Hierbei wird auch bei einer Änderung der Randbedingungen die Verzögerung konstant gehalten. Eine sinnvolle Grenze für dieses Vorgehen liegt bei einer Datenrate von ca. 700 Mbit/s. Bei der ECP2/M-Familie können die Schnittstellen bis zu 533 Mbit/s für DDR-Speicher und bis zu 850 Mbit/s bei Standard-DDR eingesetzt werden.

Die SCM-Familie bietet den Vorteil, dass die Standard-DDR-Schnittstellen bis zu einer Datenrate von 2 Gbit/s unterstützt werden. Zusätzlich zu der elektrischen Schnittstelle sind auch schon Speicher-Controller für DDR1/2 und QDR als Hard-IP in den so genannten MACO-Blöcken (eingebettete strukturierte ASIC-Blöcke mit der Bezeichnung „Masked Array for Cost Optimization“) integriert. Dadurch fallen bei der Benutzung dieser Blöcke keine Lizenzgebühren für die IP-Cores an. Auch entstehen keine zusätzlichen Laufzeiten für die Implementierung dieser Designs.

Weitere Anwendungsgebiete für schnelle parallele Schnittstellen

Die heute häufigste Anwendung der schnellen parallelen Schnittstellen sind die Speicherschnittstellen für DDR1/2. Diese haben eine Datenrate bis zu ca. 600 Mbit/s. Der nächste Schritt wird auf dem Speicherbereich die DDR3-Speicherschnittstelle sein, die eine weitere Herausforderung für FPGAs darstellt. Hierbei werden Datenraten bis 1 Gbit/s benötigt.

- Keine Angst vor parallelen Schnittstellen

- Literatur

- Keine Angst vor parallelen Schnittstellen

- Keine Angst vor parallelen Schnittstellen

- Realisierung von parallelen Schnittstellen