Auswahl des richtigen FPGA für unterschiedliche Anwendungsfälle

Keine Angst vor parallelen Schnittstellen

Fortsetzung des Artikels von Teil 2

Keine Angst vor parallelen Schnittstellen

Eine Schnittstelle über 600 Mbit/s ist heute zum Beispiel die Hyper-Transport-Schnittstelle, die von 800 Mbit/s bis 1,6 Gbit/s betrieben wird. Diese Schnittstelle wird hauptsächlich von AMD für seine schnellen Opteron-Prozessoren benutzt, um hier eine schnelle Datenanbindung mit geringer Latenzzeit zu realisieren. Durch ihre AIL-Funktion, die mit bis zu 2 Gbit/s betrieben werden kann, bietet die SCM-Familie auch hier Vorteile. Die SPI-4.2-Schnittstelle (System Packet Interface) wird häufig für den 10 Gbit/s schnellen Datenaustausch zwischen Bausteinen in der Telekommunikations-Industrie verwendet.

Hier ist die ECP2/M-Familie in der Lage, 16 Kanäle mit bis zu 645 Mbit/s im statischen Betrieb zu betreiben. Die SCM-Familie unterstützt Datenraten über 1 Gbit/s pro Kanal im dynamischen Modus.

Jobangebote+ passend zum Thema

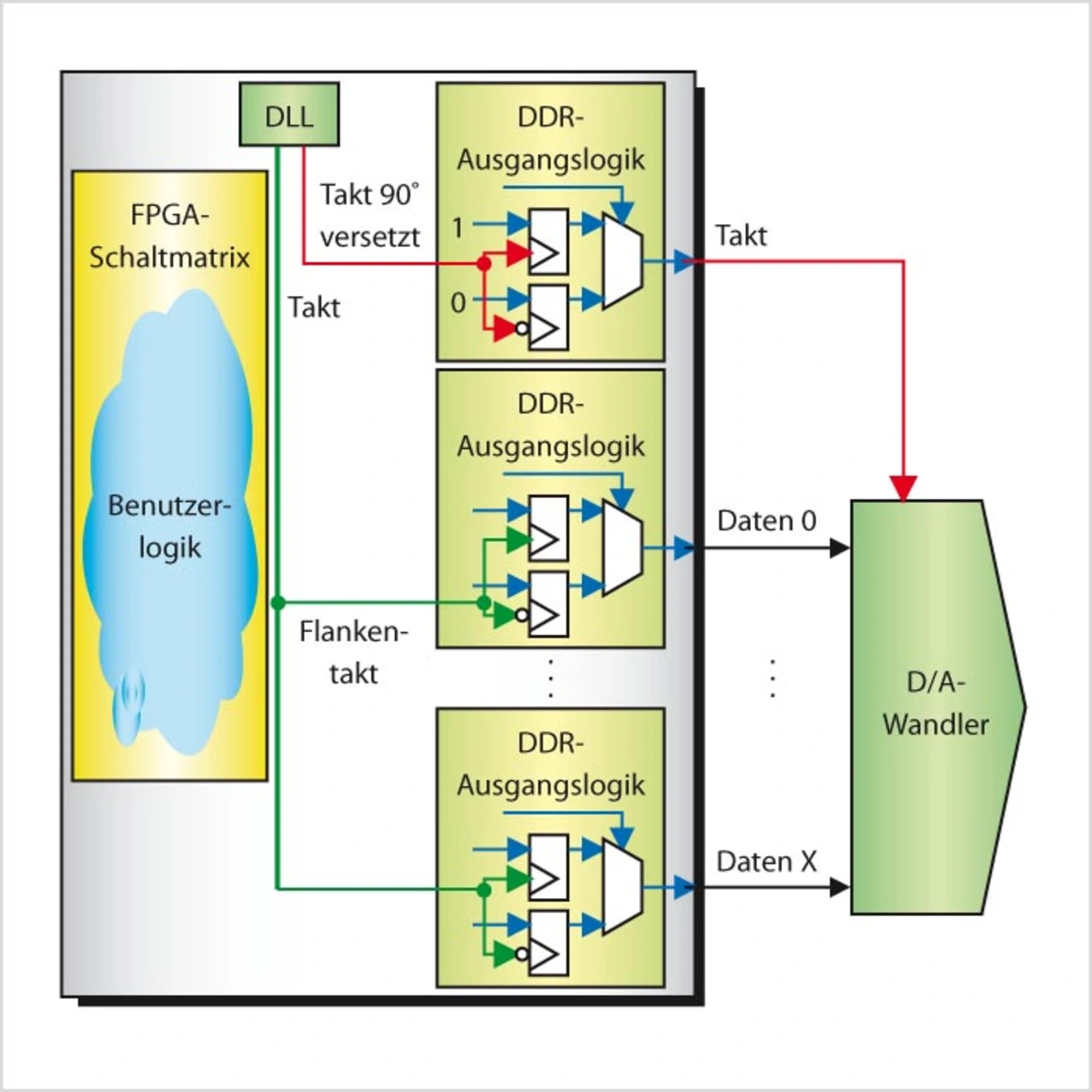

Eine weitere Anwendung für solch hohe Datenraten ist die Datenaufnahme mit schnellen A/D-Wandlern (ADC, Analog to Digital Converter). Diese haben meist eine LVPECLoder LVDS-Schnittstelle, bei der der Takt phasengleich zu den Daten geliefert wird. Hier kann man jetzt die AIL-Methode anwenden oder den Takt mit Hilfe der PLL um 90 Grad verschieben, um die Daten sicher in das FPGA zu übernehmen. Häufige Verwendung der schnellen parallelen Schnittstellen findet man auch bei der Ansteuerung von schnellen D/AWandlern (DAC, Digital to Analog Converter), wie es zum Beispiel bei schnellen Signalgeneratoren üblich ist (Bild 5). Die DACs haben eine parallele LVDS-Schnittstelle, bei der die Daten und der Takt geliefert werden müssen. Das FPGA muss in der Lage sein, einen 1-GHz-Takt und die entsprechenden Daten zu liefern. Auch dies ist mit der SCM-Familie möglich, da hier die I/Os die entsprechende Geschwindigkeit liefern, sowie Edge-Takt-Netzwerke vorhanden sind, die für einen sehr geringen Skew auf der Taktleitung sorgen, welche die Ausgangsregister taktet.

- Keine Angst vor parallelen Schnittstellen

- Literatur

- Keine Angst vor parallelen Schnittstellen

- Keine Angst vor parallelen Schnittstellen

- Realisierung von parallelen Schnittstellen