IEDM 2012

IMEC-Chef zeigt Weg zu 7-nm-Chips auf

Fortsetzung des Artikels von Teil 1

Auch FinFETs sind irgendwann am Ende

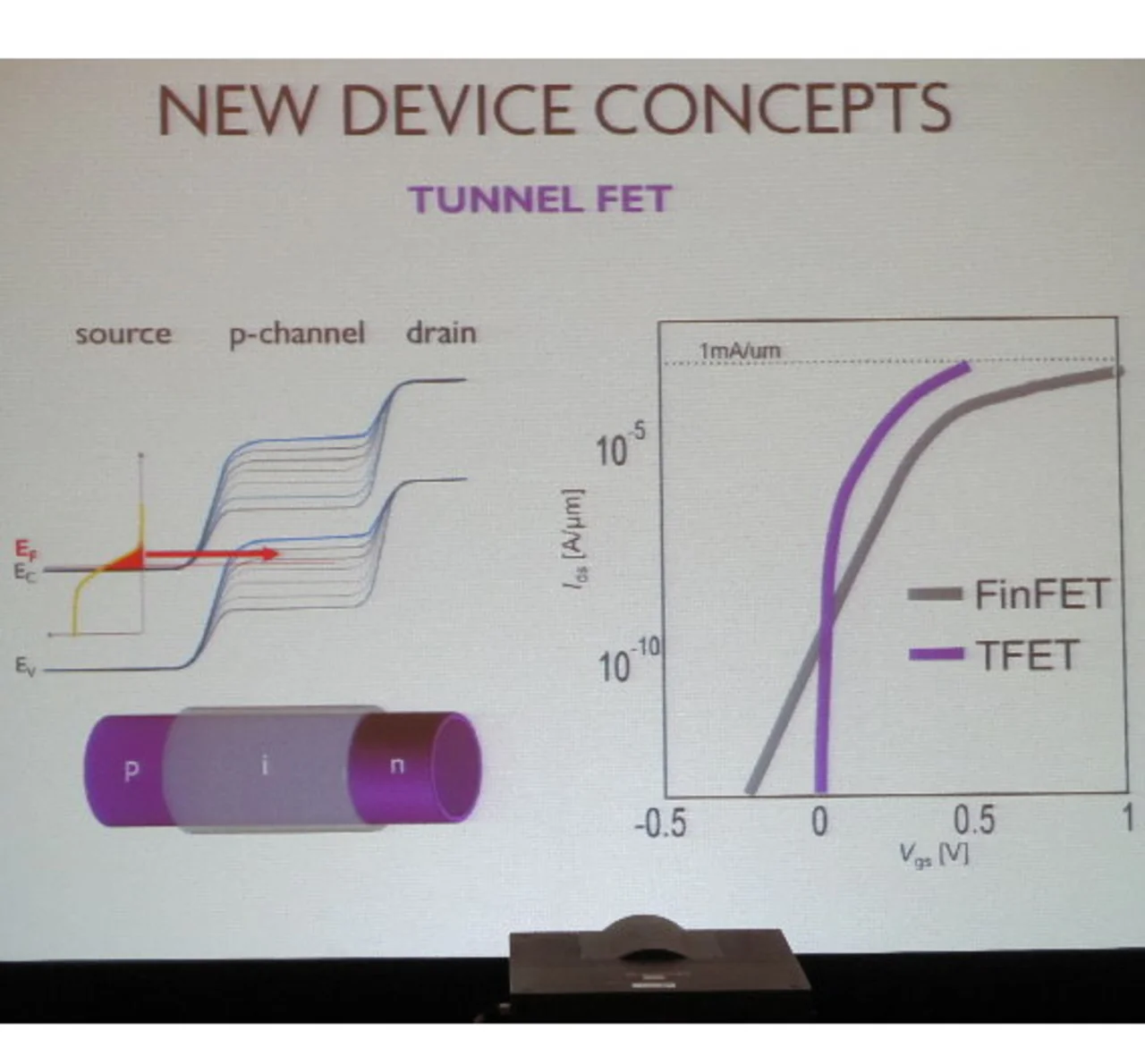

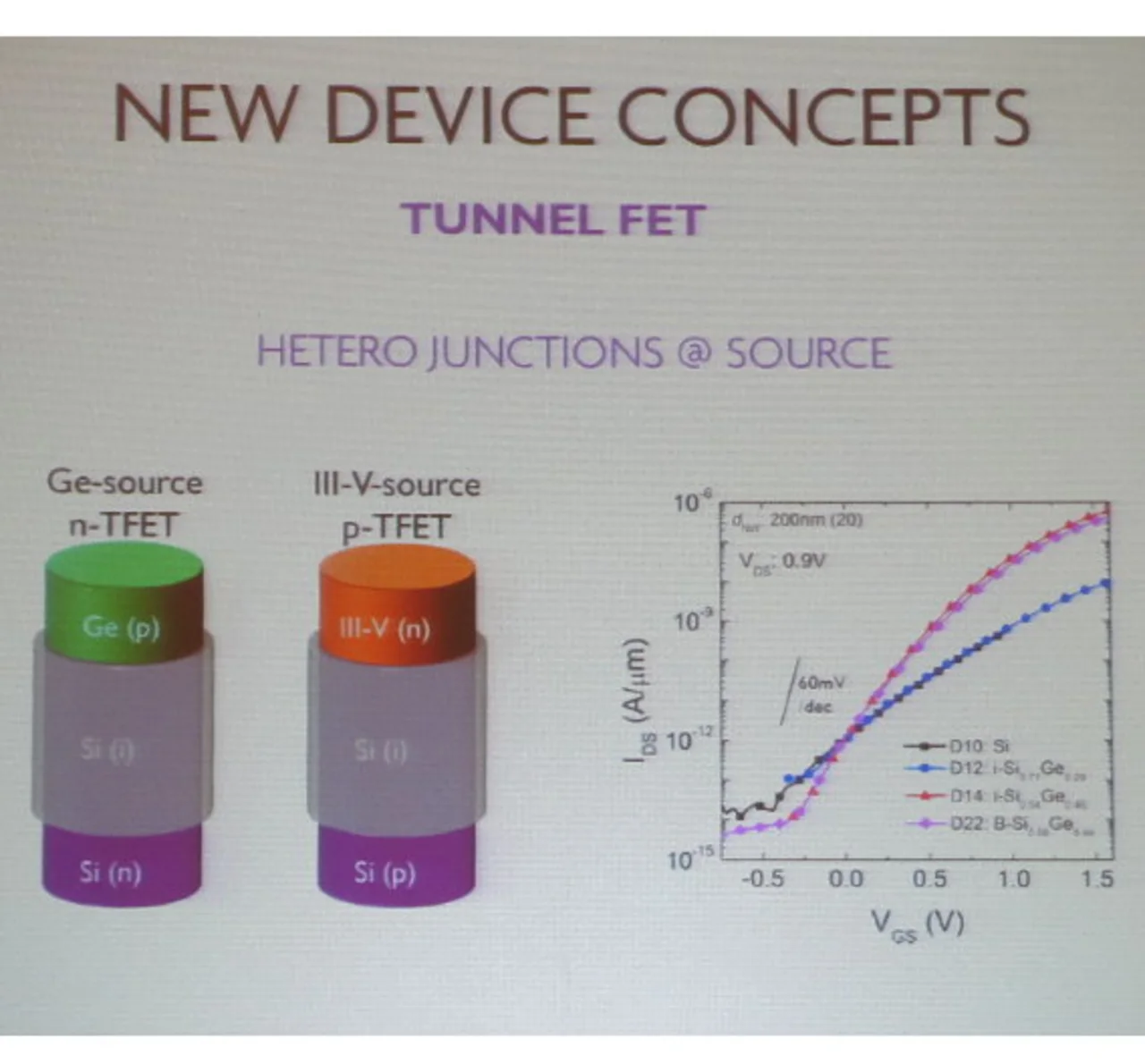

Für den 7-nm-Node sieht Van den Howe keine Möglichkeit mehr, mit den heutigen FinFET-Strukturen weiterzukommen. Seiner Ansicht nach sind sogenannte Tunnel-FETs die Transistoren der Wahl. Bisher wird für Transistoren ja die sogenannte "Feldeffekttechnologie" genutzt, wobei eine elektrische Spannung einen Elektronenfluss erzeugt, der den Transistor aktiviert. Die Tunnel-FET-Technologie (Bilder) basiert auf einem grundlegend anderen Prinzip: Der Transistor verfügt über zwei durch eine Energiebarriere getrennte "Kammern". In der ersten warten Heerscharen von Elektronen, der Transistor sei dadurch deaktiviert. Durch das Anlegen einer elektrischen Spannung erhalten sie die notwendige Energie, um die Barriere zu überwinden und in die zweite Kammer zu gelangen, wodurch der Transistor auf „ON“ schaltet.

Jobangebote+ passend zum Thema

Bisher ist der "Tunneleffekt" bei Transistoren nur als Störfaktor bekannt. Gemäss der Quantentheorie überwinden bestimmte Elektronen die Barriere selbst wenn sie scheinbar nicht genügend Energie besitzen. Reduziert man nun die Breite der Barriere, kann dieser Quanteneffekt verstärkt und genutzt werden. Damit kann die Versorgungsspannung auf bis zu 0,2 V gesenkt werden, was in der Praxis bedeutet, dass die Leistungsaufnahme bis zu 100x reduziert werden kann.

Speicher der Zukunft

Auch über die zukünftigen Speicher machte sich Hove Gedanken. NAND-Flash läuft in diverse Grenzen. Zum einen steigen mit kleineren Geometrien die Interferenzen zwischen benachbarten Bits, zudem sinkt die Anzahl der Elektronen, die in Schreib- und Lesevorgänge involviert ist, immer weiter ab – bis auf 100 im 20-nm-Prozess. Damit wird die erwünschte Datenerhaltung für 10 Jahre oder länger immer schwieriger zu erreichen. Und zu guter Letzt wird mit dem Schrumpfen auch noch die Anzahl der Schreib-/Löschzyklen einer Multi-Level-Zelle dramatisch verringert.

Mit Hilfe neuer Strukturen und Materialien wird man sich bis zum 10-nm-Node retten können, dann ist mit konventionellem NAND jedoch Schluß. Als Ersatz könnte sogenanntes RRAM (resistive RAM) herhalten, das auf HfO2 basiert und exzellente Skalierungs-Eigenschaften hat – bis zu einer Fläche von weniger als 10x10 nm2.

Bei den flüchtigen Speichern (DRAM und SRAM) wird man ebenfalls in Probleme laufen. Hier explodieren vor allen Dingen die Leckströme, was man bis 20 nm noch mit einer sogenannten MIMCAP-Struktur (Metal-insulator-metal-capacitor), die einen RuOx/TiOx/STO-Stack nutzt, in den Griff bekommen kann. Unterhalb von 20 nm setzt das IMEC auf sogenanntes STT-RAM (Spin-torque-transfer), das Daten über die Spin-Richtung der Elektronen, die durch den Tunnel eines magnetisch-resistiven-Ements fließen, speichert. Magnetische Sandwiches. Jede Speicherzelle eines STT-RAM besteht aus drei Lagen: zwei magnetische Schichten sowie dazwischen eine nichtmagnetische Schicht. Beim Lesen verursacht die unterschiedliche relative Ausrichtung der Elektronenspins in den ferromagnetischen Schichten eine unterschiedliche Leitfähigkeit des Sandwiches. Paralleler Spin bedeutet einen geringen, antiparallelen einen hohen Widerstand. Beim Schreiben lässt sich die Spinausrichtung durch einen Stromstoß dauerhaft beeinflussen. Somit lässt sich die Zelle zum Speichern von Information verwenden.

Grundlage der STT-RAMs ist übrigens der 1988 von dem Jülicher Wissenschaftler Prof. Peter Grünberg und dem Franzosen Prof. Albert Fert unabhängig voneinander entdeckte „Riesenmagnetowiderstand“, auch GMR-Effekt (giant magnetoresistance) genannt. Damit legten sie das Fundament der „Spin-Elektronik“. 2007 teilten sich beide Forscher für diese Entdeckung den Physik-Nobelpreis.

EUV-Lithografie ist ein Muß

Während man bei der 20-nm-Fertigung noch mit der 193-nm-Immersions-Lithografie und Double-Patterning hinkommt, wäre schon bei 14 nm das Triple-Patterning notwendig. Das Problem besteht laut van den Hove darin, dass die Wafer-Kosten damit explodieren würden (Bild). Gegenüber dem heutigen 28-nm-Node würden sie sich fast verdoppeln, während beim Einsatz von EUV „nur“ Mehrkosten von knapp 60 % zu Buche stehen würden, was nur wenig mehr ist als bei der 20-nm-Fertigung, die ihrerseits dank Double-Patterning ja auch schon deutlich teurer wird. Zudem ist eine 50-prozentige Flächenreduktion einer Speicherzelle ohne EUV nicht möglich.

Die heutigen Herausforderungen insbesondere hinsichtlich einer leistungsfähigen Strahlungsquelle für einen hinreichenden, d.h. wirtschaftlich vertretbaren, Wafer-Durchsatz pro Stunde sind bekannt – laut van den Hove stehen der Problemlösung jedoch keine unüberwindbaren physikalischen Grenzen entgegen.

- IMEC-Chef zeigt Weg zu 7-nm-Chips auf

- Auch FinFETs sind irgendwann am Ende