HF-Produkte für die Unterhaltungselektronik

Fortsetzung des Artikels von Teil 4

Zeigerarithmetik minimiert Anzahl der Lade/Speicher-Zyklen

Im Durchschnitt werden 30 % der Prozessortakte nicht für Verarbeitungsvorgänge, sondern für Lade-/Speicher-Anweisungen verbraucht. Der AVR32 senkt die Anzahl der benötigten La-de-/Speicher-Anweisungen durch Byte- (8 bit), Halbwort- (16 bit), Wort- (32 bit) und Doppelwort-Lade-/Speicher-Anweisungen (64 bit) in Verbindung mit unterschiedlichen Zeigerarithmetiken zum effizienten Zugriff auf Tabellen, Datenstrukturen und zufällige Daten in einer möglichsten geringen Anzahl von Takten. Beispielsweise bei Blockverschlüsselungsalgorithmen, wie sie in der Kryptographie verwendet werden, ist ein spezieller Array-Adressierungsvorgang mit einer langen Folge von Anweisungen erforderlich. Bei diesem Vorgang dominieren vier Speicherzugriffe, bei denen jeweils eines von vier Bytes in einem 32-bit-Wort extrahiert, dieses mit Null erweitert und zu einem Basiszeiger addiert wird. Als Ergebnis dieses Vorgangs erhält man die Speicheradresse, auf die zugegriffen werden soll. Die Ausführung dieses Vorgangs auf einem konventionellen Prozessor kann 14 Taktzyklen in Anspruch nehmen (Listing).

Jobangebote+ passend zum Thema

|

Der AVR32 verfügt über eine neuartige Anweisung zum Laden mit extrahiertem Index „Load with extracted index, ld.w“. Damit wird dieser Vorgang auf nur sieben Taktzyklen reduziert, wobei alle vier Speicherzugriffe in vier Zyklen durchgeführt und alle vier Offsets in einem Register gespeichert werden.

Ein weiteres Beispiel für eine effektive Lade-/Speicher-Anweisung ist die Anweisung zum Laden mehrerer Register (Load Multiple Register, ldm). Die Anweisung kann in Zusammenhang mit der Anweisung „Store Multiple“ (stm) eingesetzt werden, um zwei Mal zwei Register aus dem Datencache zu holen. Die Anweisung kann eingesetzt werden, um eine Rückgabe einer Subroutine zu veranlassen, da das letzte zu schreibende Register der Programmzähler sein kann. Die Ausführung einer speziellen Rückgabe-Anweisung am Ende einer Subroutine ist dann nicht mehr erforderlich.

Durch Senkung der Anzahl der durchzuführenden Lade-/Speicher-Anweisungen steigert der AVR32-Kern den Durchsatz pro Taktzyklus. Insgesamt hat der AVR32-Kern 28 Anweisungen, mit denen die Effizienz der Lade-/Speicher-Anweisungen verbessert wird.

„Out-of-Order“-Ausführung dank mehrerer Pipelines

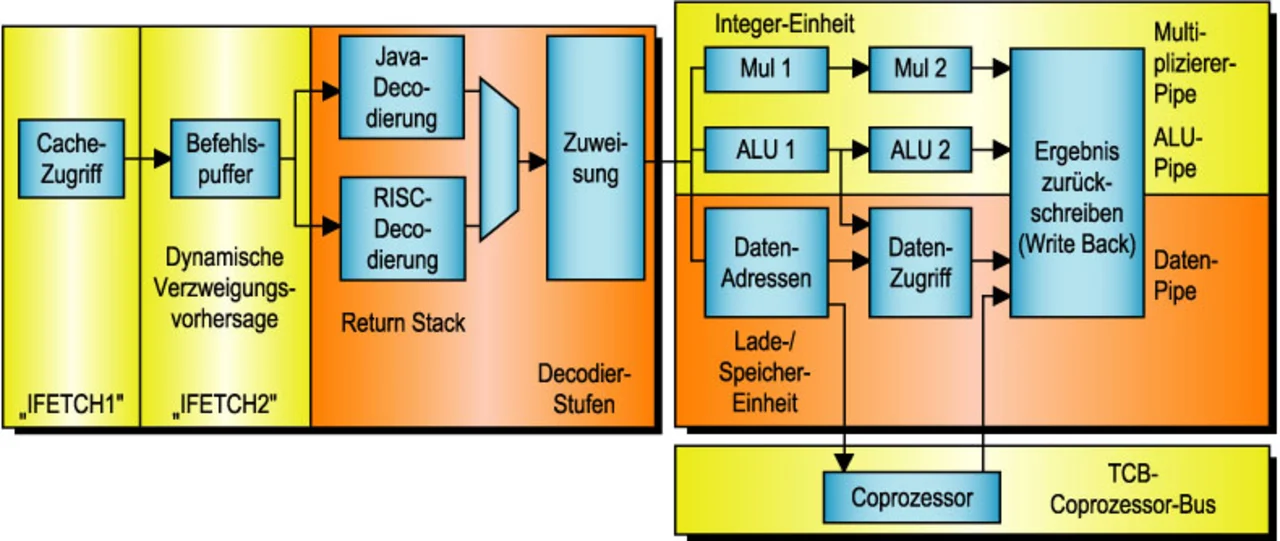

Die AVR32-CPU hat eine 7-stufige Pipeline mit drei Sub-Pipelines (Multiplikation/MAC, Laden/Speichern und ALU), mit deren Hilfe Rechenvorgänge an nicht abhängigen Daten außerhalb der vorgegebenen Reihenfolge und parallel durchgeführt werden können (Bild 2). Eine konventionelle Architektur hat nur eine einzige Pipeline, in der der Code angehalten wird, bis jede einzelne Anweisung abgearbeitet wurde. Dies kann bei Anweisungen, die mehrere Taktzyklen benötigen, wertvolle Rechenressourcen verschwenden. Die Logik in der AVR32-Pipeline ermöglicht die gleichzeitige Ausführung von nicht abhängigen Anweisungen unter Ausnutzung der verfügbaren Pipeline-Ressourcen. Durch die Ausführung außerhalb der vorgegebenen Reihenfolge kann der Durchsatz pro Taktzyklus erhöht werden. Eine Gefahrenerkennungslogik (Hazard Detection Logic) erkennt abhängige Anweisungen und hält diese am Eingang der Pipeline zurück, bis die Anweisung, von der diese Anweisungen abhängig sind, ausgeführt ist.

Pfiffige Architekturdetails sparen Taktzyklen

Arbeit, die nicht verrichtet werden muss, spart Energie. So trägt eine Reihe von kleinen aber effizienten Architekturmerkmalen zur Genügsamkeit des AVR32-Kerns bei, angefangen beim Akkumulator-Cache über „Data Forwarding“ und SIMD-Befehle bis hin zur Verzweigungsvorhersage.

Akkumulator-Cache in der Multiplikatorarchitektur

DSP-Algorithmen bestehen zu einem großen Teil aus Multiplikations-/Akkumulationsvorgängen (MAC), bei denen zwei Werte miteinander multipliziert und wiederholt zu einem dritten Wert addiert werden. Normale Prozessorarchitekturen handhaben diese MAC-Operationen so, dass sie zunächst die Multiplikation durchführen und dann das Ergebnis zu einem Wert addieren, der in einem Register gespeichert ist. Die Anzahl der für diese MAC-Operation erforderlichen Taktzyklen ist oft von der Anzahl der Lese-/Schreib-Ports in der Registerdatei abhängig. Lese- und Schreib-Ports verlangen ihren Tribut – nicht nur, was die Siliziumfläche betrifft, sondern auch hinsichtlich der Leistungsaufnahme, da bei jedem Zugriff auf eine Registerdatei zahlreiche Leitungen innerhalb des Registerdatei-RAMs umgeschaltet werden, was die Leistungsaufnahme ansteigen lässt. Wenn der Multiplikator zwei Lese- und Schreib-Ports hat, dann dauert dieser Vorgang zwei Taktzyklen, einen zur Durchführung der Multiplikation und einen zweiten zur Durchführung der Addition. Werden ein weiterer Lese- und ein weiterer Schreibport hinzugefügt, kann eine MAC-Operation in einem einzigen Takt erfolgen. Andererseits führen die Lese- und Schreibports zu höheren Kosten und höherer Leistungsaufnahme der CPU. Deshalb müssen die Chipentwickler die höheren Silizium-Kosten und die höhere Leistungsaufnahme mit der Steigerung der Rechenleistung abwägen.

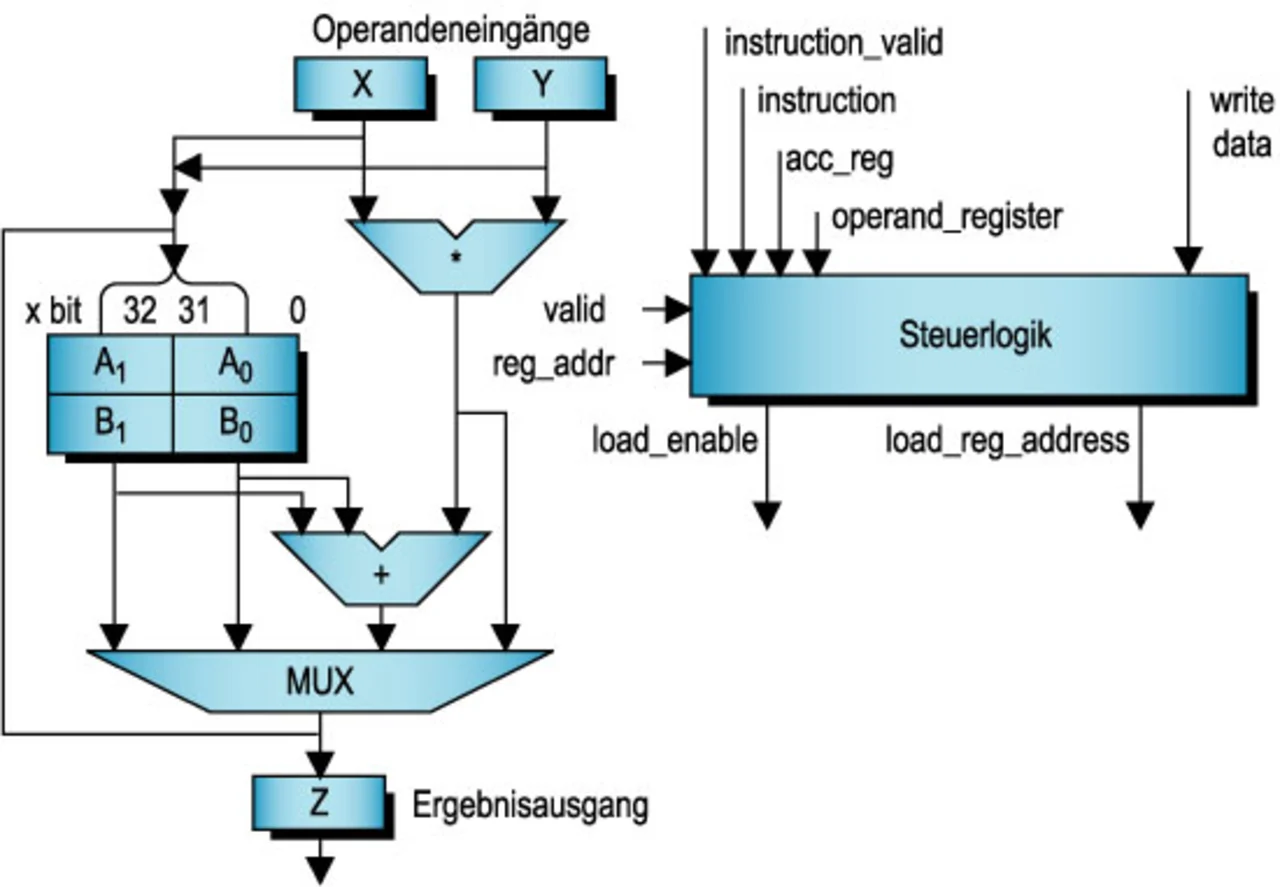

Die AVR32-Entwickler bei Atmel haben eine patentierte, neuartige Methode entwickelt, mit der MAC-Operationen (Multiply/Accumulate) in einem Takt ausgeführt werden können, ohne dass zusätzliche Ports für den Multiplizierer erforderlich wären: den „Akkumulator-Cache“ innerhalb des Multiplizierers (Bild 3). Der Akkumulator-Cache wird verwendet, um den Wert zu speichern, zu dem addiert werden soll. Da bei MAC-Einheiten das Produkt der Multiplikation immer zum letzten Wert addiert werden muss, sind keine externen Register erforderlich. Somit wird das Ergebnis der Multiplikation zum Wert im Cache addiert, und das nächste Ergebnis wird zu diesem Wert addiert und so weiter. Dadurch kann der MAC-Vorgang in einem einzigen Takt ausgeführt werden, und zwar mit einem Minimum an Lese- und Schreibports und ohne externe Register.

- HF-Produkte für die Unterhaltungselektronik

- Zeigerarithmetik minimiert Anzahl der Lade/Speicher-Zyklen