HF-Produkte für die Unterhaltungselektronik

RF Magic und Compotron haben ein Abkommen unterzeichnet, das den Distributor zum Vertrieb der HF-Halbleiterprodukte von RF Magic in Deutschland, Österreich und der Schweiz sowie in Polen berechtigt

Atmels 8-bit-AVR-Controller wurde als proprietäre Architektur so erfolgreich vom Markt aufgenommen, dass man sich entschloss, nun eine 32-bit-Variante nachzuschieben. Der AVR32 zielt auf portable Anwendungen wie beispielsweise tragbare Video-Player, MP3-Player und Mobiltelefone.

Jobangebote+ passend zum Thema

Zu den Produkten zählen Silizium-Tuner für satellitengestützte (DVB-S) TV-Anwendungen und für digitale TV-Systeme mit terrestrischem Empfang (DVB-T). Angeboten werden außerdem Channel Stacking Switches (CSS) und Multi-Band-Transceiver-Chipsätze für den WiMAX-Standard.

In dem Maße jedoch, in dem sich in Video-„iPods“ und PDAs eine VGA-ähnliche Auflösung mit 30 Bildern pro Sekunde durchsetzt, steigen auch die Anforderungen an die Rechenleistung exponentiell. Üblicherweise wird dieses Problem dadurch gelöst, dass der Prozessortakt erhöht wird. Dadurch erhöht sich aber auch die Leistungsaufnahme – oftmals so sehr, dass diese für batteriebetriebene kompakte Geräte nicht mehr tragbar ist. Zum Beispiel benötigt man für eine MPEG4-Decodierung mit Quarter-VGA (QVGA) bei 30 Bildern pro Sekunde auf einem ARM9-Kern (Freescale i.MX21) eine Taktfrequenz von 266 MHz mit ei-ner Leistungsaufnahme von mehr als 320 mW [1]. Um dieses Problem zu lösen, hat die AVR-Produktgruppe bei Atmel eine neue MCU/DSP-Architektur entwickelt, die in der Lage ist, mehrere DSP-Berechnungen in einem Taktzyklus auszuführen, und damit bei niedriger Taktfrequenz und Leistungsaufnahme einen hohen Datendurchsatz erzielt.

Bei den meisten RISC-Architekturen wird eine große Anzahl von Prozessortaktzyklen für nicht produktive Vorgänge verschwendet, die aber eine hohe Leistungsaufnahme nach sich ziehen, wie z.B. das Laden, Speichern und Verschieben von Daten, für Verzweigungen, für den Versuch, Daten zu laden, die im Cache nicht vorhanden sind (Cache-Misses), oder für blockierte Instruktionen, die darauf warten, dass Vorgänge, die mehrere Taktzyklen in Anspruch nehmen, in der Pipeline ausgeführt werden. Keiner dieser Vorgänge leistet einen Beitrag zur Ausführung der Anwendung. Im Gegenteil: Sie verringern sogar den Datendurchsatz pro Taktzyklus. Der AVR32-Kern erreicht einen höheren Durchsatz, indem er nicht produktive Prozessortakte möglichst vermeidet, und zwar auf folgende Weise:

- Reduzierung der Anzahl von Lade/Speicher-Zyklen,

- maximale Ausnutzung der Rechenressourcen,

- Durchführung von Verzweigungen ohne Verzögerungen (zero Penalty Branches) und

- Senkung der Anzahl der Fälle; in denen Daten im Cache nicht gefunden werden.

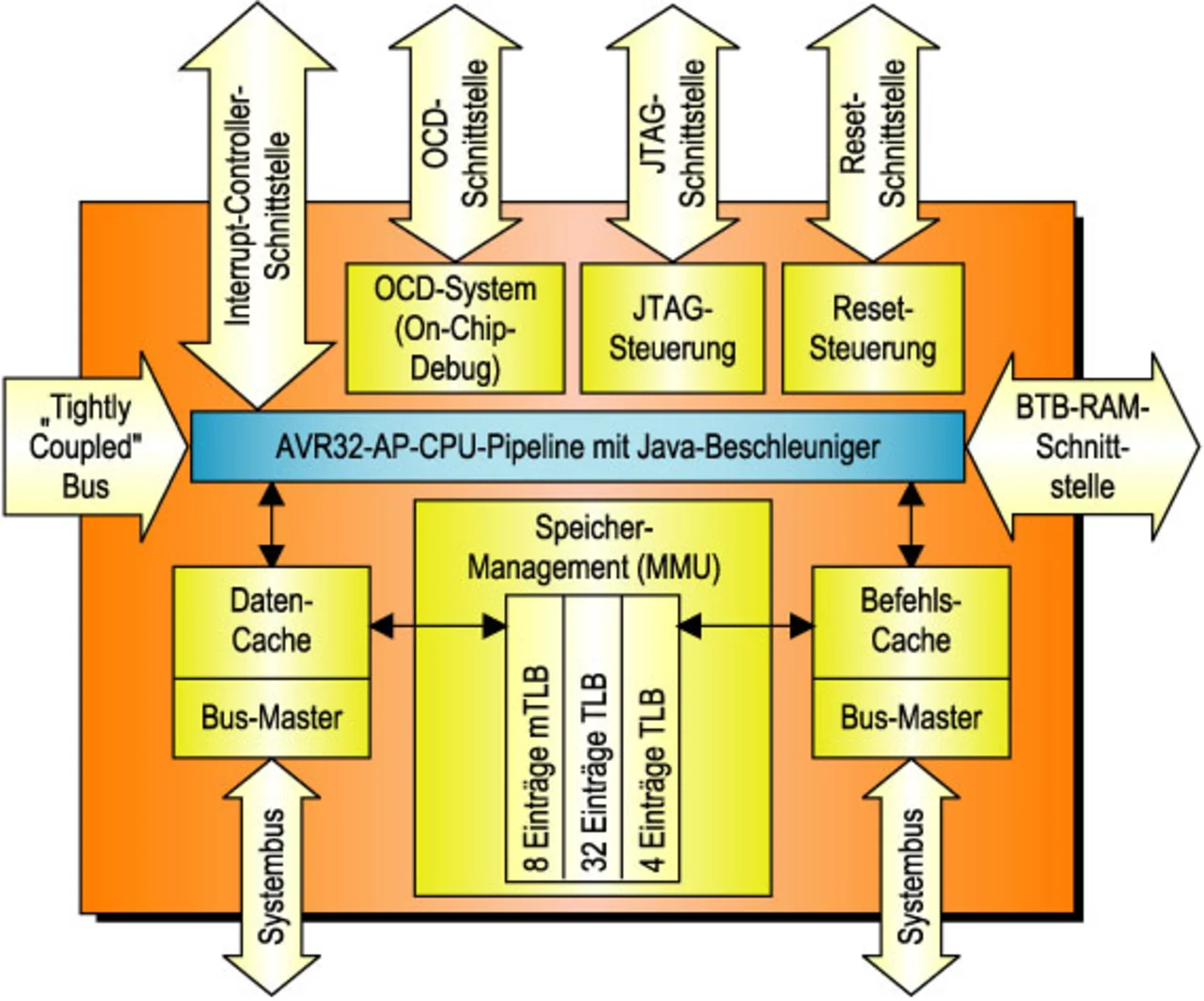

Außerdem ist die Architektur des AVR32-Kerns (Bild 1) auf eine minimale Leistungsaufnahme im aktiven Betrieb und minimale Leckströme getrimmt.

- HF-Produkte für die Unterhaltungselektronik

- Zeigerarithmetik minimiert Anzahl der Lade/Speicher-Zyklen