HF-Produkte für die Unterhaltungselektronik

Fortsetzung des Artikels von Teil 2

Vektormultiplikations-Coprozessor

Bei Multimedia-Anwendungen müssen üblicherweise arithmetische Operationen an 3?8-bit-Matrizen durchgeführt werden, z.B. zur Bildfilterung (FIR-Filterung), Farbraumumsetzung (RGB – YUV), Bildskalierung und Viertel-Pixel-Bewegungsabschätzung bei MPEG4/H.264. Damit der CPU-Durchsatz so hoch wie möglich bleibt, ist beim AP7000 die Vektormultiplikationseinheit (VMU) über die AVR32-AP-Coprozessor-Schnittstelle angekoppelt. Sie arbeitet damit parallel zur CPU und führt verschiedene Vektormultiplikationen ohne Beteiligung der CPU aus.

MPEG4-Videodaten werden typischerweise in YUV komprimiert, während für die meisten Video-DACs und LCD-Controller RGB benötigt wird. Der Vektormultiplikations-Coprozessor führt diese Umwandlung doppelt so schnell durch wie die AVR32-CPU. Bei Bildskalierungsanwendungen steigert der Vektormultiplikations-Coprozessor des AP7000 die Leistungsfähigkeit bei der MPEG-Decodierung um ca. 50 %.

Direkter Speicherzugriff per DMA-Controller

Multimedia-Anwendungen sind datenintensiv. Große Datenströme fließen zwischen den Peripheriegeräten und den Speichern. Die Verarbeitung dieser Datentransfers kann die CPU erheblich belasten. Ohne DMA-Controller würden die beiden 100-Mbit/s-Ethernet-MACs und der 480-Mbit/s-USB-Slave-Controller die CPU vollständig auslasten. Der AP7000 bietet verschiedene Mechanismen für den „Direct Memory Access“ (DMA), die die Belastung der CPU durch Datentransfer zwischen den Peripheriegeräten und dem Speicher bzw. zwischen zwei Speicherorten auf dem Chip verringern. Es können gleichzeitig zwei Speicher-zu-Speicher-Transfers zwischen On-Chip-RAM oder an die externe Busschnittstelle (EBI) angeschlossenen Off- Chip-Speichern durchgeführt werden, da diese alle durch den DMA-Controller adressierbar sind.

Ein 18-kanaliger „Peripheral DMA-Controller“ (PDC) sorgt für eine enge Kopplung der Peripheriemodule und der Speicher. Der PDC richtet virtuelle Kanäle zwischen Datenregistern im Peripheriemodul und den On-Chip- oder Off-Chip-Speichern ein, wodurch die CPU vollständig von diesen Aufgaben entlastet wird.

Jobangebote+ passend zum Thema

Vier unabhängige Taktdomains sparen Strom

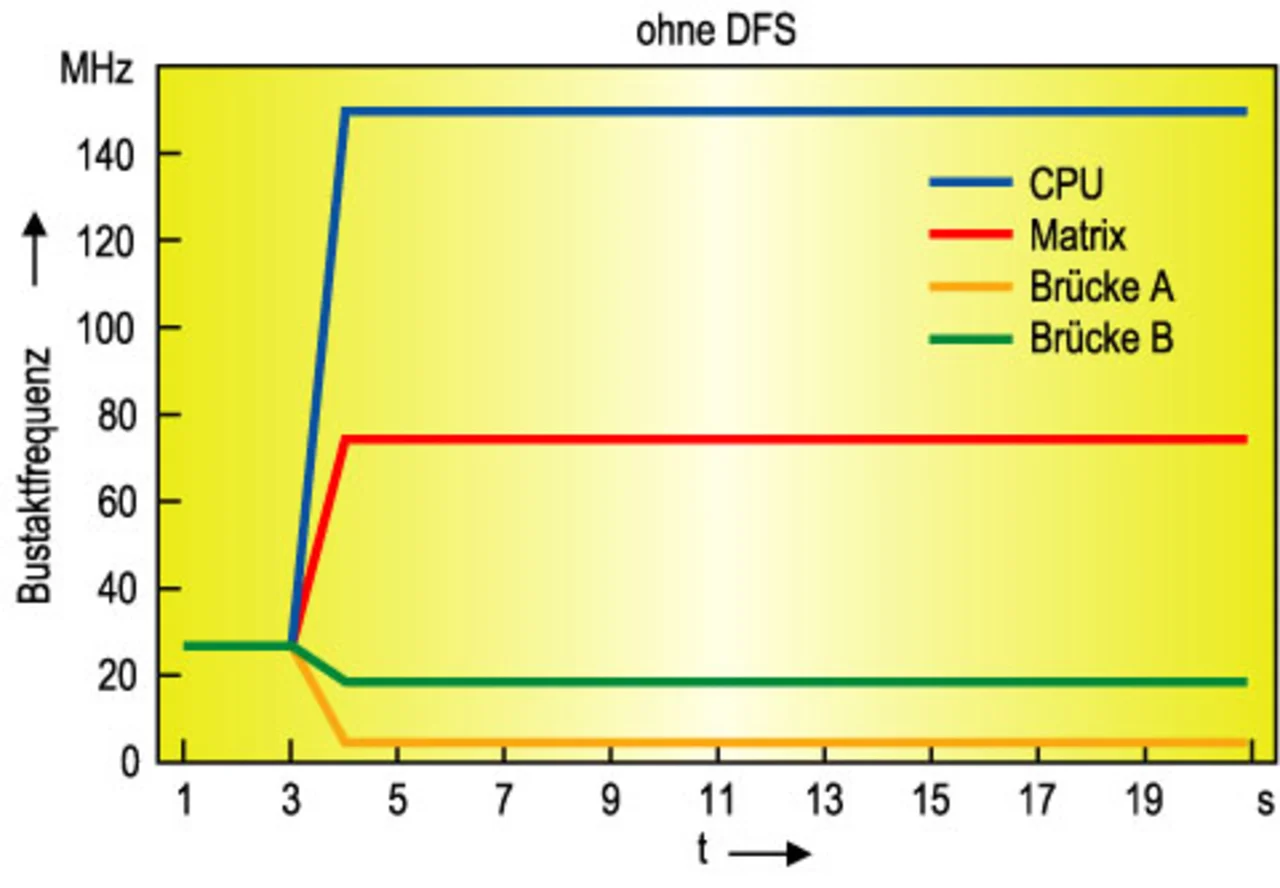

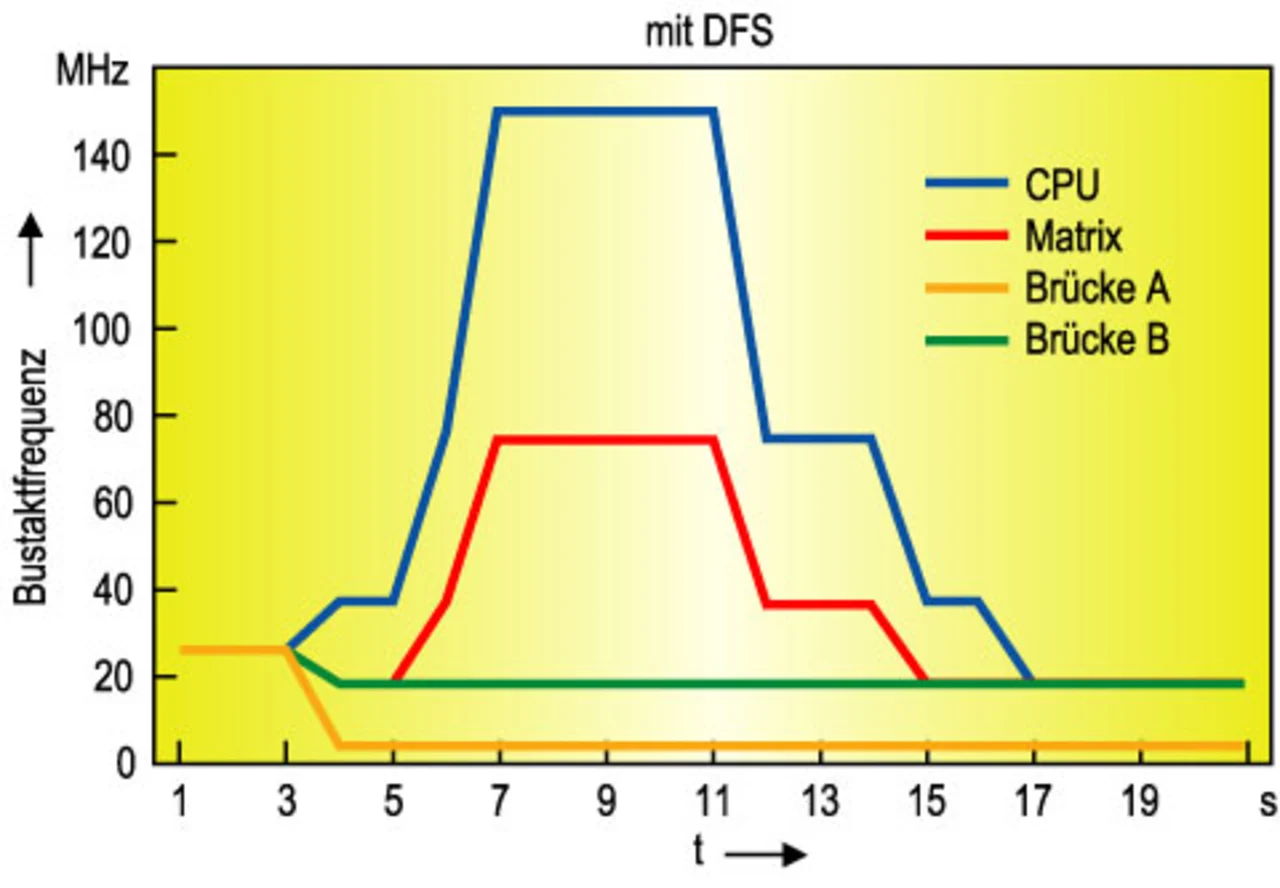

Wie die meisten hochentwickelten 32-bit-Controller verfügt der AP7000 über einen Multi-Layer-Hochgeschwin-digkeitsbus, der den Datendurchsatz dadurch verbessert, dass mehrere Operationen gleichzeitig durchgeführt werden können. Unterschiedliche Peripheriemodule benötigen unterschiedliche Busfrequenzen. Beispielsweise darf bei TWI, SPI und UART der Bus wesentlich langsamer sein als bei einem 10/100-Ethernet-MAC oder bei einem High-Speed-USB 2.0 (480 Mbit/s). In einer konventionellen Busstruktur diktiert das schnellste Peripheriegerät die Taktfrequenz für den gesamten Bus und treibt damit den Leistungsverbrauch nach oben (Bild 5). Beim AP7000 wird dieses Problem dadurch gelöst, dass zwei Peripherie-Busbrücken vorgesehen sind; langsamere Peripheriemodule werden über die Brücke A angeschlossen, Hochgeschwindigkeitsperipheriemodule über die Brücke B. Mit Hilfe von dynamischen Frequenzskalierungsalgorithmen kann der AP7000 die individuelle Taktfrequenz dieser beiden Brücken sowie die Frequenz der internen Uhr der CPU und die Frequenz der Busmatrix dynamisch konfigurieren und auf den niedrigsten möglichen Wert anpassen.

Die Taktgeber der vier Domains (Brücke A und B, CPU und Busmatrix) können gleichzeitig mit unterschiedlichen Frequenzen laufen. Damit kann jede Taktdomain zur Minimierung der Leistungsaufnahme auf den Bussystemen auf die niedrigstmögliche Frequenz eingestellt werden. Wenn z.B. die Hauptapplikation während eines Datentransfers über IrDA oder Bluetooth inaktiv ist, können die Taktfrequenzen der CPU, der Hochgeschwindigkeitsbrücke und der Busmatrix verringert werden, während die Brücke für die niedrige Geschwindigkeit mit einer (niedrigen) konstanten Taktfrequenz den Datentransfer abwickelt.

Jede einzelne oder alle Taktdomains können in einem einzigen Taktzyklus zurückgesetzt werden, indem ein 32-bit-Wert in ein Konfigurationsregister geschrieben wird. Die Änderung erfolgt unverzüglich in allen Taktdomains (Bild 6). Die internen stromsparenden Oszillatoren und PLLs laufen weiter und erfordern daher bei den Frequenzumschaltungen keinerlei Zeit für eine Kalibrierung. Der Prozessor berechnet automatisch die niedrigste Taktfrequenz für jede Domain, die die benötigte Funktion noch unterstützt.

- HF-Produkte für die Unterhaltungselektronik

- Zeigerarithmetik minimiert Anzahl der Lade/Speicher-Zyklen