HF-Produkte für die Unterhaltungselektronik

Fortsetzung des Artikels von Teil 3

„Data Forwarding“

Der AVR32 senkt die Anzahl der Takte, die für das Schreiben in und Lesen von Registerdateien benötigt werden, indem er Daten zwischen den einzelnen Pipelinestufen weiterreicht. Wenn die Ausführung von Anweisungen bereits vor der Write-back-Stufe abgeschlossen ist, werden diese direkt an den Beginn der Pipelines weitergereicht, damit sie unmittelbar von anderen darauf wartenden Anweisungen verwendet werden können. Dies senkt sowohl die Anzahl der benötigten Taktzyklen als auch die Leistungsaufnahme durch Reduzierung der Anzahl der Registerdateizugriffe. Alle Ergebnisse des AVR32 werden weitergereicht, sobald der entsprechende Vorgang abgeschlossen ist.

„SIMD“-Befehle

Durch SIMD-Anweisungen (Single Instruction/Multiple Data) in der Architektur des AVR32 kann der Durchsatz bei bestimmten DSP-Algorithmen, bei denen sich ständig wiederholende Operationen an einem Datenstrom durchgeführt werden müssen (z.B. bei der Bewegungsabschätzung zur Decodierung von MPEG-Daten), vervierfacht werden. Die Berechnung einer 8-bit-Summe absoluter Differenzen (SAD) erfolgt z.B. durch Laden von vier 8-bit-Pixeln aus dem Speicher in einem einzigen Ladevorgang, Ausführen einer gepackten Subtraktion vorzeichenloser Bytes mit Sättigung, Addition des höchsten und niedrigsten Paars gepackter Bytes und Entpacken der Bytes in gepackte Halbwörter. Diese werden dann addiert und ergeben den SAD-Wert.

Verzweigungsvorhersage

Durch die Vorhersage von Verzweigungen und Faltung kann der Schleifen-Overhead auf Null Taktzyklen reduziert werden. Tiefe Pipelines ermöglichen zwar höhere Taktfrequenzen, benötigen aber andererseits zusätzliche Taktzyklen, wenn Sprünge im Programmfluss vorkommen. Besonders schwer fallen diese bei Verzweigungen im Zusammenhang mit kleinen inneren Schleifen ins Gewicht. Um dieses Problem zu lösen, umfasst die Pipeline beim AVR32 eine Logik zur Vorhersage von Verzweigungen, die in der Lage ist, alle Anweisungen zu erkennen, bei denen sich der Verarbeitungsfluss ändert. Außerdem werden die Verzweigungen mit der Zielanweisung „gefaltet“, wodurch die Belastung durch Verzweigungen auf Null Takte reduziert wird.

Jobangebote+ passend zum Thema

Benchmarking bescheinigt hohe Codedichte und hohe Rechenleistung pro MHz

Beim Benchmarking durch EEMBC [2] zeigte die AVR32-Architektur eine hohe Codedichte und eine überdurchschnittliche Rechenleistung.

Außergewöhnliche Codedichte

Der Befehlssatz des AVR32 wurde durch umfangreiches Benchmarking und eine Optimierung in Zusammenarbeit mit dem Hersteller des Compilers (IAR) entwickelt. Dadurch hat AVR32 eine Codedichte, die 10 bis 50 % über der von ARM9- oder ARM11-Prozessorkernen liegt (festgestellt über EEMBC Benchmark-Suite). Aufgrund dieser höheren Codedichte wird weniger Platz im Cache benötigt, und es kann eine größere Anzahl von Anweisungen im Prozessor-Cache gespeichert werden. Dadurch reduziert sich die Anzahl der Fälle, in denen benötigte Daten im Cache nicht vorhanden sind, und der Prozessordurchsatz pro Taktzyklus wird höher.

Hohe taktfrequenzbezogene Rechenleistung

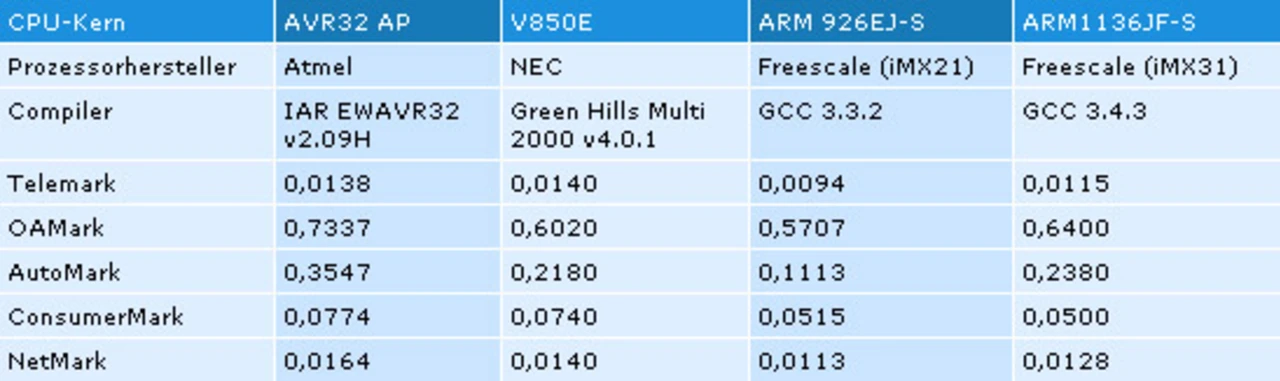

Der AVR32 erzielt eine höhere Rechenleistung pro MHz als viele andere auf dem Markt erhältliche 32-bit-CPUs aufgrund der erwähnten Besonderheiten seiner Architektur. Das Embedded Microprocessor Benchmark Consortium (EEMBC) führt Benchmark-Tests an Prozessoren mit einer Vielzahl von Algorithmen unter Verwendung eines nicht optimierten, compilierten Codes durch. Als Maß für den Durchsatz wird angegeben, wie oft pro Sekunde jeder Algorithmus bei einer bestimmten Taktfrequenz durchgeführt werden kann. Die Ergebnisse schwanken, nicht nur abhängig von der Effizienz des Prozessors, sondern auch in Abhängigkeit von den zu verarbeitenden Daten und der Effizienz des Compilers. Außerdem fasst EEMBC häufig verwendete Algorithmen in bestimmten Anwendungsklassen zusammen (z.B. Vernetzung, Konsumelektronik etc.) und berechnet den geometrischen Mittelwert der entsprechenden Benchmark-Werte. Damit kommt man zu einem Benchmark-Wert für die jeweilige Anwendungsklasse (Tabelle 1).

Höherer Durchsatz bei niedrigeren Taktfrequenzen und geringerer Leistungs-aufnahme

Bei der Architektur des AVR32 geht es darum, eine ausreichende Verarbeitungsleistung bei minimaler Leistungsaufnahme für batteriebetriebene tragbare Consumerprodukte, wie z.B. tragbare Video-Player, mobile Kassensysteme oder tragbare medizinische Geräte bereitzustellen. Der außergewöhnlich hohe Durchsatz des AVR32-Kerns ermöglicht eine geringere Taktfrequenz, was zu einer linearen Senkung der Leistungsaufnahme führt. Unabhängig davon ermöglicht der AVR32 eine Minimierung der aktiven Leistungsaufnahme bei allen Taktfrequenzen, indem er Daten in der Nähe der CPU hält und einen unnötigen Transfer von Daten auf Bussystemen vermeidet.

Ältere MCU-Architekturen z.B. kopieren die Rückgabeadresse eines Subroutinenaufrufs in einen Speicher-Stack, was unnötig Leistung verbraucht. Dies wird beim AVR32 mit Hilfe eines in die Registerdatei integrierten Link-Registers vermieden. Durch Techniken wie Data Forwarding und die Verwendung des Akkumulator-Cache werden Daten innerhalb der Pipeline gehalten, was die Gesamtleistungsaufnahme senkt. Eine weitere stromsparende Funktion besteht darin, das Statusregister und die Rückgabeadresse für Interrupts und Ausnahmen in Systemregistern abzulegen, statt Daten zu und von einem Stack zu verschieben. Auch die hohe Codedichte des AVR32 trägt zu einer Senkung der Leistungsaufnahme bei, indem sie die Anzahl der Taktzyklen senkt und die Anzahl der externen Speicherzugriffe reduziert, wenn benötigte Daten im Cache nicht gefunden werden.

- HF-Produkte für die Unterhaltungselektronik

- Zeigerarithmetik minimiert Anzahl der Lade/Speicher-Zyklen