Flash-Mikrocontroller für komplexe Steueraufgaben

Fortsetzung des Artikels von Teil 1

Flash-Mikrocontroller für komplexe Steueraufgaben

Viele Anwender, die Probleme mit der Rechenleistung ihrer bestehenden 8- und 16-bit-Lösungen haben, sind auf die UC3-Mikrocontroller umgestiegen. Die hohe DSP-Leistung des UC3 hat sogar eine ganze Reihe neuer Anwendungsmöglichkeiten erschlossen, die bisher eine Domäne von Multi-Chip-Lösungen auf Basis von ARM9- und x86-CPUs waren.

Jobangebote+ passend zum Thema

Schneller-Flash-Zugriff

In einem Mikrocontroller fungiert der integrierte Flash-Speicher als Haupt-Programmspeicher. Da jedoch die Lesezugriffszeiten des Flash-Speichers so lang sind, dass nicht in jedem Taktzyklus ein Befehl ausgelesen werden kann, müssen alle 32-bit-Flash-Mikrocontroller so genannte Wait-States einfügen, wenn sie auf ihren Flash-Speicher zugreifen. Dies bedeutet nichts anderes, als dass die CPU die Wartezeit, bis ein neuer Befehl zur Verfügung steht, mit Warten vergeudet. Die meisten 32-bit-Mikrocontroller sind deshalb mit „Fetch-Puffern“ ausgestattet, die die Wartezeiten bei sequenziellen Flash-Zugriffen vermeiden helfen. Oberhalb einer gewissen Taktfrequenz führt allerdings jede Abweichung von der Befehlsabfolge (beispielsweise durch If-then-else-oder Case-Anweisungen höherer Programmiersprachen) zu Wait-States.

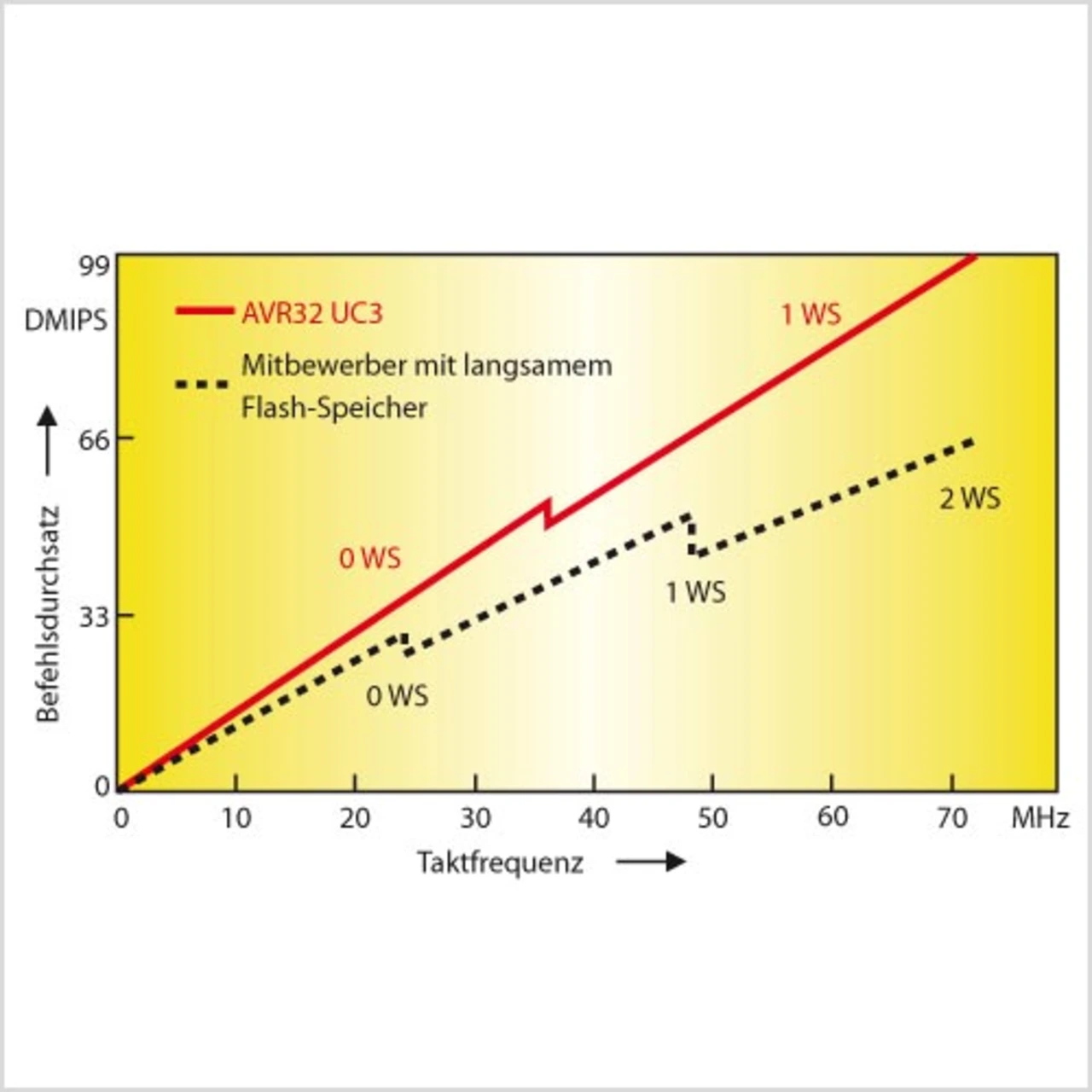

Der AVR32 UC3 hat einen äußerst schnellen Flash-Speicher, der bei der maximalen Taktfrequenz von 66 MHz mit einem einzigen Wait-State auskommt, während bei den meisten konkurrierenden Lösungen zwei Wait-States nötig sind. Welche Bedeutung diese Verbesserung hat, macht Bild 1 deutlich. Wann immer ein Anheben der Taktfrequenz das Einfügen eines zusätzlichen Wait-States notwendig macht, bedeutet das einen Leistungsverlust für das gesamte System. Die maximale Taktfrequenz eines Mikrocontrollers ist somit von untergeordneter Bedeutung, solange der Flash-Speicher langsam ist. Der schnelle Flash-Speicher des AVR32 UC3 aber lässt die Rechenleistung des Mikrocontrollers signifikant ansteigen.

Von Beginn an hatte das AVR32-UC3-Design-Team hohen Wert auf die Optimierung der DSP-Leistung gelegt. Durch das Hinzufügen von speziellen Befehlen für Single-Cycle-Multiply-Accumulate-Operationen für verschiedene Zahlenformate sowie für Sättigung und Rundung kommt der AVR32 UC3, verglichen mit bisherigen Architekturen, auf eine außerordentlich hohe DSP-Leistung.

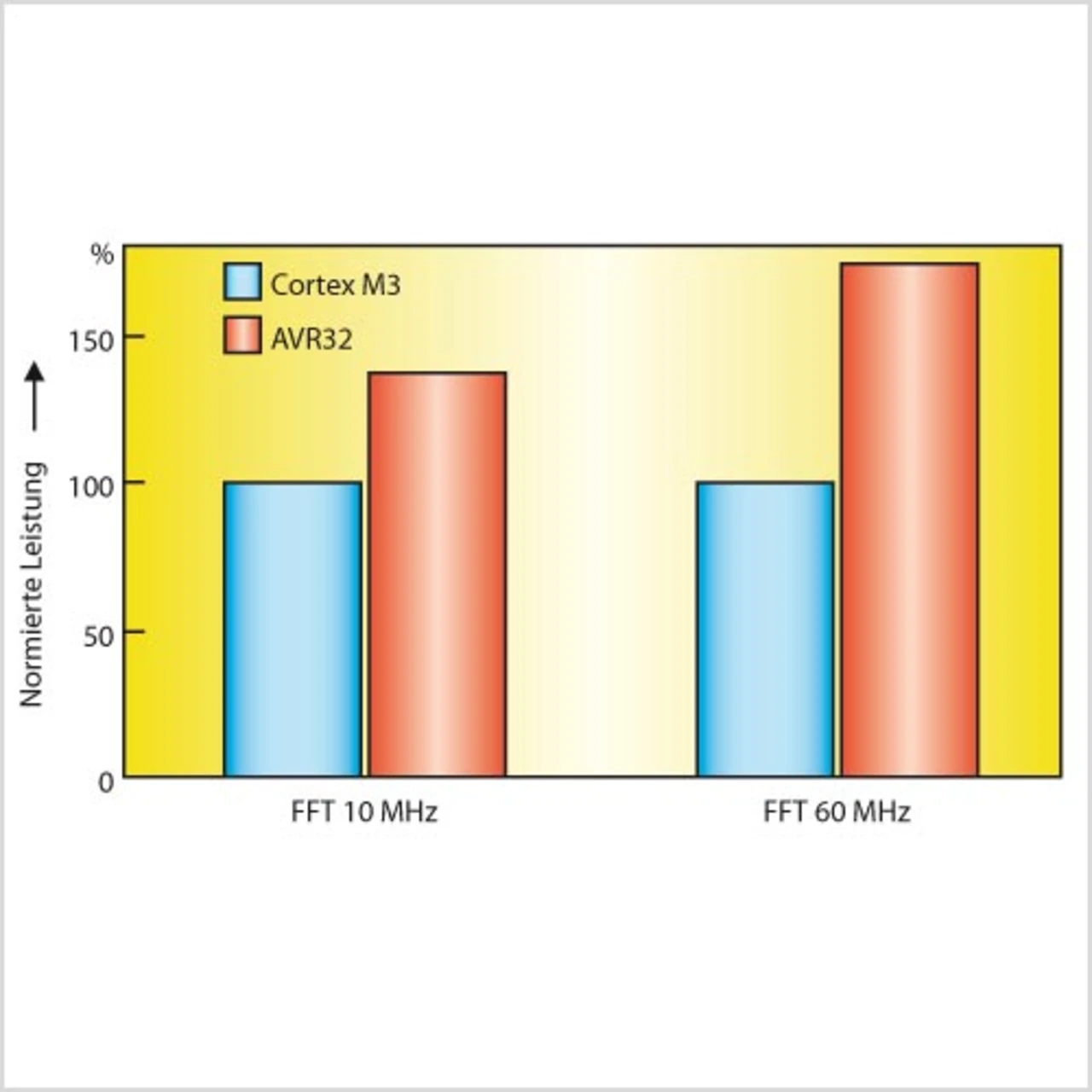

Bild 2 zeigt eine einfache Leistungs-Gegenüberstellung zwischen einem AVR32 UC3A und einem vergleichbaren Cortex-M3-basierten Controller eines Mitbewerbers. Bei der Ausführung einer FFT-Routine bei 10 MHz bzw. 60 MHz zeigen sich nicht nur die klaren Vorteile des DSP-Befehlssatzes, sondern auch die Auswirkungen der schnellen Flash-Architektur.

Bei 10 MHz können beide Bausteine noch ohne Wait-States auf den Flash-Speicher zugreifen. Der DSP-Befehlssatz führt hier nur zu einem 40-prozentigen Leistungsgewinn gegenüber der Cortex-M3-Architektur, bei der diese Instruktionen fehlen. Hebt man allerdings die Taktfrequenz auf 60 MHz an, ist der AVR32 UC3A auf einmal 75 % schneller als sein Konkurrent.

40 % gehen nach wie vor auf das Konto des DSP-Befehlssatzes, doch die übrigen 35 % sind auf die Tatsache zurückzuführen, dass der AVR32 seine Flash-Zugriffe bei 60 MHz mit nur einem Wait-State ausführen kann, während der Konkurrenzbaustein zwei benötigt.

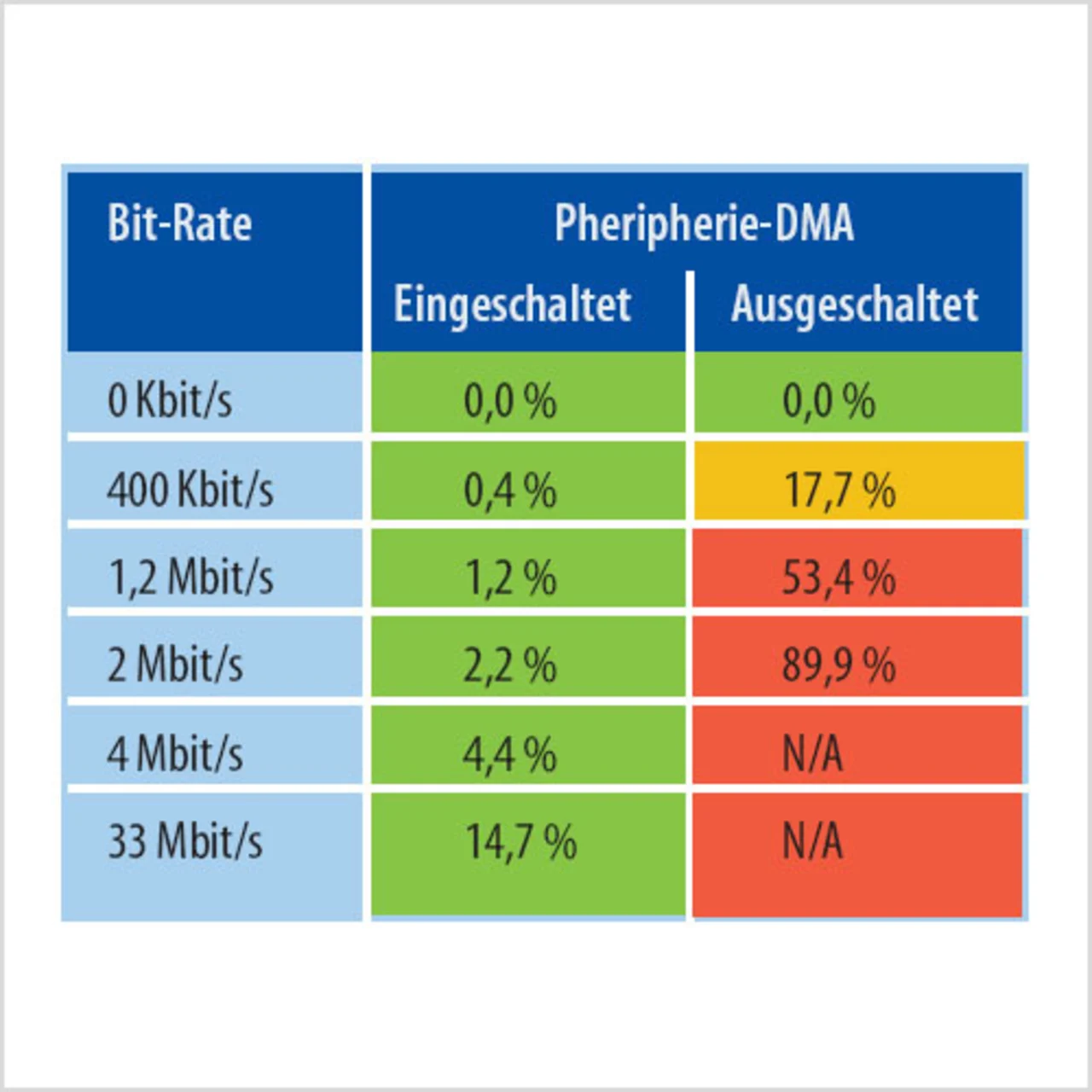

Vor einigen Jahren wurde der Peripherie-DMA-Controller erstmals in der SAM7-Architektur vorgestellt. Sein Nutzen wird in der Tabelle deutlich. Solange der Peripherie-DMA-Controller inaktiv ist, beträgt der maximale Datendurchsatz des SPI-Moduls ca. 1 Mbit/s, hierbei ist die CPU über die Hälfte der Zeit allein mit dem Transfer von zu sendenden oder empfangenen Daten beschäftigt. Der Peripherie-DMA-Controller erzielt auf dem SPI-Bus einen Datendurchsatz von 33 Mbit/s, wobei die CPU nur zu 15 % belastet wird.

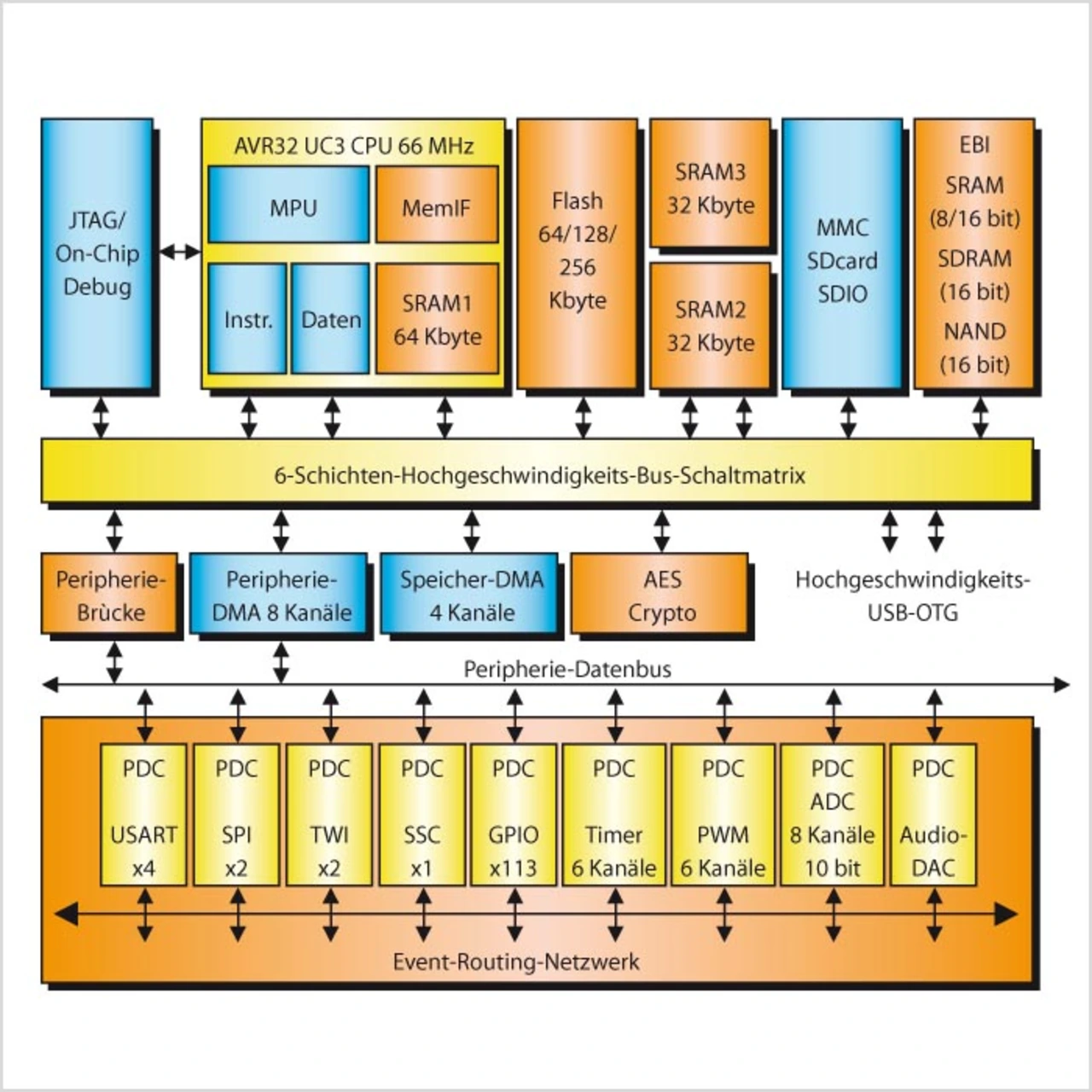

Die Einführung neuer hochleistungsfähiger Peripheriemodule setzt einen echten Speicher-zu-Speicher-DMA-Controller voraus. Bei den AVR32-UC3-Bausteinen mit Hochgeschwindigkeits-USB-Peripherie-Option ist das USB-Modul mit AES-Kryptographie und einem großen internen SRAM-Speicher kombiniert. Dabei ist der SRAM-Speicher so aufgeteilt, dass sich ein Speicherblock innerhalb der CPU befindet, um während der Programmausführung Single-Cycle-Zugriffe zu ermöglichen.

Zur Maximierung der Bandbreite sind außerdem zwei weitere SRAM-Blöcke auf zwei verschiedenen Bussen der Busmatrix angeordnet, um als Datenpuffer für das Hochgeschwindigkeits-USB-Modul (Bild 3) zu fungieren. Diese Blöcke sind so an den Speicherzu-Speicher-DMA-Controller angebunden, dass die Daten ohne Belastung der CPU übertragen werden können.

Das neue Event-Steuerungs-System bedeutet einen Paradigmenwechsel, denn der interruptgesteuerte Datentransfer wird hier durch eine asynchrone, ereignisgesteuerte Datenübertragung abgelöst. Dies ist eine Erfindung, die die CPU in typischen Mikrocontroller-Applikationen erheblich entlastet. Traditionell verwendet ein Mikrocontroller Interrupts, um Ereignisse im System anzustoßen. Dies lässt sich am besten an einem Beispiel erklären. Ein Timer-Überlauf-Interrupt soll einen A/D-Wandler veranlassen, einen Signalwert zu nehmen. Beim Einsatz von Interrupts muss die CPU dazu aus einem etwaigen Sleep-Modus aufgeweckt werden und Taktzyklen für Routineaufgaben investieren. Anders ist es mit dem Event-Controller: Hier triggert der Timer den A/D-Wandler direkt, ohne die CPU aufzuwecken. Die Leistungsaufnahme sinkt dadurch, und die CPU kann sich wichtigeren Aufgaben widmen.

- Flash-Mikrocontroller für komplexe Steueraufgaben

- Flash-Mikrocontroller für komplexe Steueraufgaben

- Programmentwicklung mit AVR32-Mikrocontrollern

- Flash-Mikrocontroller für komplexe Steueraufgaben