Effiziente Abbildung von Audio-Algorithmen in Programmierbarer Logik und ASICs

Rock ’n’ Roll im FPGA

Fortsetzung des Artikels von Teil 1

Steckbrief“ des Programmwerkzeugs

Synplify DSP setzt auf dem Industriestandard Matlab/Simulink der Firma The Mathworks auf. In einem Blockset wird eine Bibliothek von Standardkomponenten zur Verfügung gestellt, mit deren Hilfe sich komplexe Algorithmen implementieren lassen. Neben Basiskomponenten wie „Add“, „Gain“ und „Delay“ beinhaltet die Bibliothek auch viele komplexe Funktionen wie FIR- oder IIR-Filter und Cordic-Algorithmen. Alle Funktionen, auch die hochkomplexe FFT oder der Viterbi-Decoder, lasssen sich beliebig parametrisieren. Es ist ebenfalls möglich, anwenderdefinierte Bibliotheken zu erstellen und bestehenden VHDL- oder Verilog-Code in ein Simulink-Modell zu integrieren. Synplicity stellt auch eine Vielfalt an Referenzschaltungen aus den Bereichen Bildverarbeitung, Software Defined Radio und Audio gratis zur Verfügung – so auch die beschriebene Applikation, der Sample-Rate-Konverter für beliebige Audiofrequenzen, als Referenzdesign.

Das Werkzeug ermöglicht die Implementierung von Single- und Multi-Rate-Systemen. Der Code kann mit den Optimierungsmöglichkeiten „Folding“, „Multichannelization“ und „Retiming“ entweder flächenoptimiert oder geschwindigkeitsorientiert implementiert werden. Erzeugt wird immer ein generischer, nicht verschlüsselter RTL-Code, der mit allen gängigen Werkzeugen synthetisierbar ist. Synplicity empfiehlt allerdings für FPGAs die Nutzung des eigenen Syntheseprodukts – Synplify Pro – da mit diesem Werkzeug die besten Ergebnisse erzielt werden. Unterstützt werden die FPGAs aller gängigen Hersteller: Actel, Altera, Lattice, Quicklogic und Xilinx. Seit neuestem steht auch eine „ASIC-Variante“ der Entwicklungsumgebung zur Verfügung.

Jobangebote+ passend zum Thema

Literatur:

[1] Fliege, N.J.: Multirate Digital Signal Processing. John Wiley & Sons, New York.

[2] Marven, C.; Ewers, G.: A simple Approach to Digital Signal Processing. Wiley-Interscience, 2001.

[3] www.synplicity.com/literature/

verwandte Artikel:

FPGA-Systeme architekturneutral entwerfen

| Philipp Jacobsohn ist seit Oktober 2000 bei der Synplicity Deutschland GmbH als Field Applications Engineer tätig. Er ist verantwortlich für die technische Unterstützung aller Produkte aus den Bereichen RTL-Synthese, Signalverarbeitung, ASIC Prototyping und Debugging. 1993 schloss er sein Studium der Elektrotechnik im Fachbereich Informationsverarbeitung an der FH Bielefeld ab. philipp@synplicity.com |

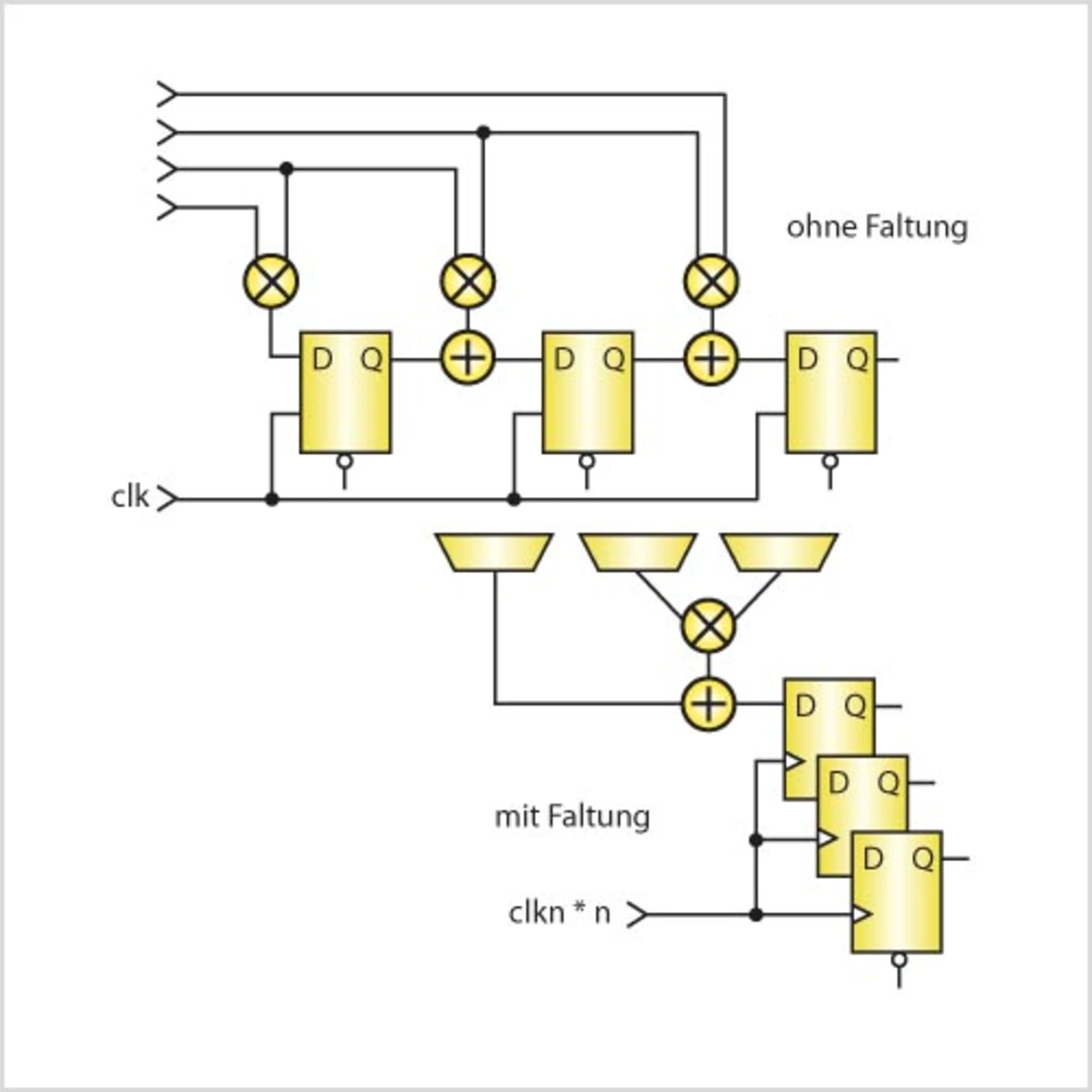

Synplify DSP stellt mit der Option „Folding“ die Möglichkeit zur Verfügung, die Anzahl der genutzten Multiplizierer praktisch beliebig zu minimieren (Bild 4). Speziell solche Schaltungen, die mit niedrigen Sample-Frequenzen betrieben werden, können von dieser Optimierung profitieren. Die Idee ist einfach: Im Normalfall wird für jede Multiplikation ein Hardware-Multiplizierer genutzt, auch wenn die Abtastfrequenz im Kilohertzbereich liegt. Das FPGA kann jedoch mit Taktraten in mindestens zweistelligem, üblicherweise sogar dreistelligem Megahertzbereich betrieben werden. Wird nun der Hardware-Multiplizierer mit der FPGA-Systemfequenz betrieben, kann in einem Zeitmultiplex-Verfahren eine serielle Abarbeitung der Multiplikationen erfolgen.

Ein praktisches Beispiel: Liegt die Sample-Frequenz der Schaltung bei 3 MHz und das FPGA kann mit maximal 120 MHz betrieben werden, so kann jeder einzelne Hardware-Multiplizierer im gleichen Zeitraum 40 Rechenoperationen durchführen, wenn die Systemfrequenz zur Multiplikation genutzt wird. Die notwendige Hardware wird also um den Faktor 40 reduziert. Die Verarbeitung von Audiosignalen erfolgt jedoch nicht mit Sample-Frequenzen im Megahertz Bereich. Die üblichen Abtastraten betragen – wie schon erwähnt – 44,1, 48, 96 oder 192 kHz. Daraus resultiert, dass ein Sample-Rate-Konverter (oder eine beliebige andere Schaltung, die mit geringen Abtastfrequenzen arbeitet) soweit „zusammengefaltet“ werden kann, dass nur noch sehr wenige Hardware- Multiplizierer benötigt werden. Eine Implementierung ist also auch in den kleinsten verfügbaren „Low-cost“-FPGAs möglich. Solche Bauteile werden von allen FPGA-Herstellern zu günstigen Preisen angeboten und stellen durchaus eine Alternative zu Digitalen Signalprozessoren dar. Es besteht natürlich auch die Möglichkeit, besonders rechenintensive Algorithmen aus einem DSP heraus in ein FPGA zu verlagern und so den Prozessor zu entlasten.

Da das Folding-Feature in Synplify DSP auch Multi-Rate-Systeme unterstützt, kann die Anzahl der benötigten Multiplizierer sogar noch weiter reduziert werden als in einem System mit einer einzigen Sample-Frequenz. Das Oversampling lässt sich mit Hilfe von zwei FIR-Filtern realisieren, und diese beiden Filter werden mit unterschiedlichen Sample-Frequenzen betrieben. Das Filter, das für die höhere Abtastfrequenz zum Einsatz kommt, wird mit dem vom Anwender spezifizierten Folding-Faktor gefaltet. Das Filter mit der geringeren Sample-Frequenz wird mit einem entsprechend höheren Faktor gefaltet – letzterer errechnet sich aus der Differenz der Sample-Frequenzen beider Filter, multipliziert mit dem vom Anwender definierten Folding- Faktor. Ist zum Beispiel die Abtastfrequenz des einen Filters achtmal so hoch wie die Sample-Frequenz des anderen Filters, dann wird der „schnellere“ Filter um den Faktor 8, der „langsamere“ um den Faktor 64 gefaltet. Hierdurch können auch solche Schaltungen platzoptimiert werden, die mit sehr hohen Abtastraten arbeiten und normalerweise eine Faltung nicht erlauben. Wird beispielsweise ein System mit einer Sample-Frequenz von 200 MHz betrieben und es wird ein Faltfaktor von 2 eingeführt, so steigt die Systemfrequenz auf 400 MHz. Eine solche Taktrate ist auch mit den durchsatzstärksten FPGAs nur schwerlich zu erreichen. Die Alternative: Es wird ein Folding-Faktor von 1 definiert. Die Schaltungsteile, die mit der höchsten Abtastrate betrieben werden, sind vom Falten ausgenommen. Alle Schaltungsteile eines Multi-Rate-Systems, die mit geringeren Sample-Frequenzen betrieben werden, profitieren aber von der Faltung und damit von der platzoptimierten Abbildung. Der Anwender muss den Faktor der Faltung nur für das Gesamtsystem vorgeben. Das Propagieren des Foldings über alle Abtastfrequenzen hinweg funktioniert dann automatisch.

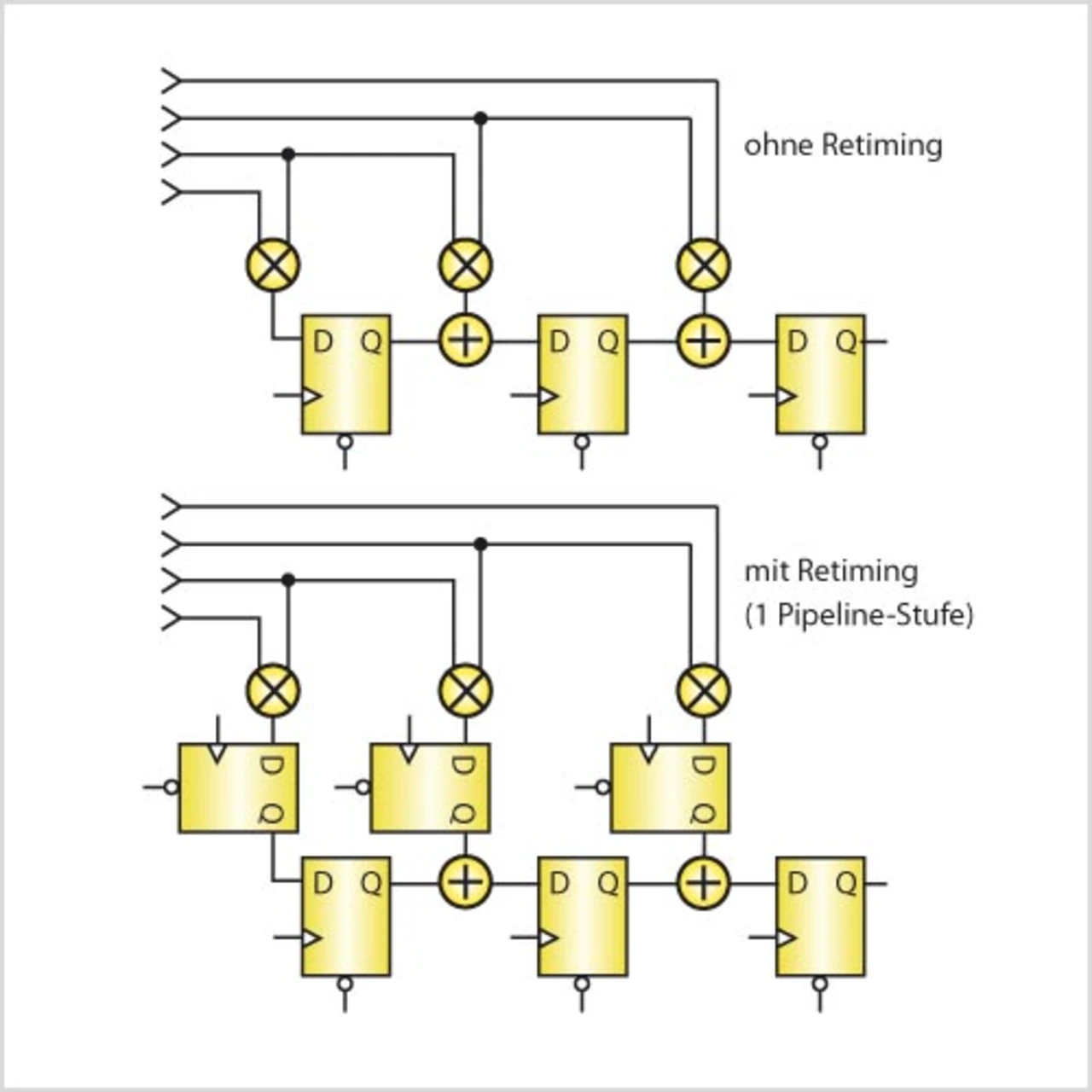

Das Folding-Feature ist mit einer weiteren Optimierungsmöglichkeit kombinierbar, dem „Retiming“ (Bild 5). Genügt ein Gesamtsystem nicht den Anforderungen an die Zielfrequenz, können so viele Pipeline-Stufen eingefügt werden, bis die gewünschte Taktrate erreicht wird. Das ist besonders in solchen Schaltungen wichtig, die einen erheblichen Folding-Faktor aufweisen und dementsprechend mit einer hohen Systemfrequenz betrieben werden müssen. Natürlich lässt sich das Retiming auch für solche Schaltungen nutzen, die wenig oder gar nicht gefaltet werden, sich aber an der Leistungsgrenze des FPGAs befinden. Das Einfügen von Pipeline-Stufen ermöglicht es, die Anzahl an kombinatorischen Gattern zwischen zwei Registern (Logic Levels) so weit zu reduzieren, bis die kombinatorischen Gatterverzögerungen die Taktfrequenz nicht mehr „ausbremsen“. Synplify DSP führt bei der Generierung des RTL-Codes eine Timing- Analyse durch, die sowohl die gewünschte Sample-Frequenz als auch den Faltfaktor und die Zielarchitektur des FPGAs berücksichtigt.

So wird eine Schaltung, die auf ein „schnelles“ FPGA abgebildet wird (z.B. Xilinx Virtex-5 oder Altera Stratix-3), mit weniger Pipeline-Stufen optimiert als eine identische Schaltung, die in einem „langsamen“ Low-cost-FPGA (z.B. Lattice ECP-2 oder Xilinx Spartan-3) implementiert wird. In FPGAs stehen große Mengen an Registern zur Verfügung, die für diese Optimierung genutzt werden können. Anders als die Anzahl der Multiplizierer oder LUTs (Look-up Tables), die schnell knapp werden können, sind Register in mehr als ausreichender Menge vorhanden und müssen im Normalfall nicht mit Bedacht genutzt werden. So lässt sich mit geringem Aufwand eine erhebliche Steigerung der Systemfrequenz erzielen. Selbstverständlich resultiert aus dem Einfügen von Pipeline-Stufen eine erhöhte Latenz des Systems. Wird ein Retiming-Faktor von z.B. 8 eingeführt, so erscheint das Ergebnis der Berechnung acht Taktzyklen (der Systemfrequenz, nicht der Sample-Frequenz) später am Ausgang des FPGA. Das muss beim Einbetten einer Schaltung in ein Gesamtsystem berücksichtigt werden.

Besonders wichtig ist, dass die zuvor beschriebenen Optimierungen das (in Matlab/Simulink beschriebene) Modell nicht beeinflussen. Der Algorithmus wird in Simulink implementiert und verifiziert. Die Verifikation erlaubt es, die Funktion des Algorithmus zu validieren und den Einfluss von Quantisierungseffekten darzustellen. Das Blockset der Synplify-DSPSoftware erlaubt es, die Floating-nach Fixed-Point-Konvertierung sowohl mittels Truncation (Eliminieren irrelevanter Bitstellen) als auch Rounding (bei Underflow) oder Saturation (bei Overflow) durchzuführen. Sobald die Simulation zeigt, dass der Algorithmus wie gewünscht funktioniert, kann der RTL-Code generiert werden. Das Optimieren des VHDL- oder Verilog-Codes verändert unter Umständen die Latenz, nicht aber die Funktion der Schaltung.

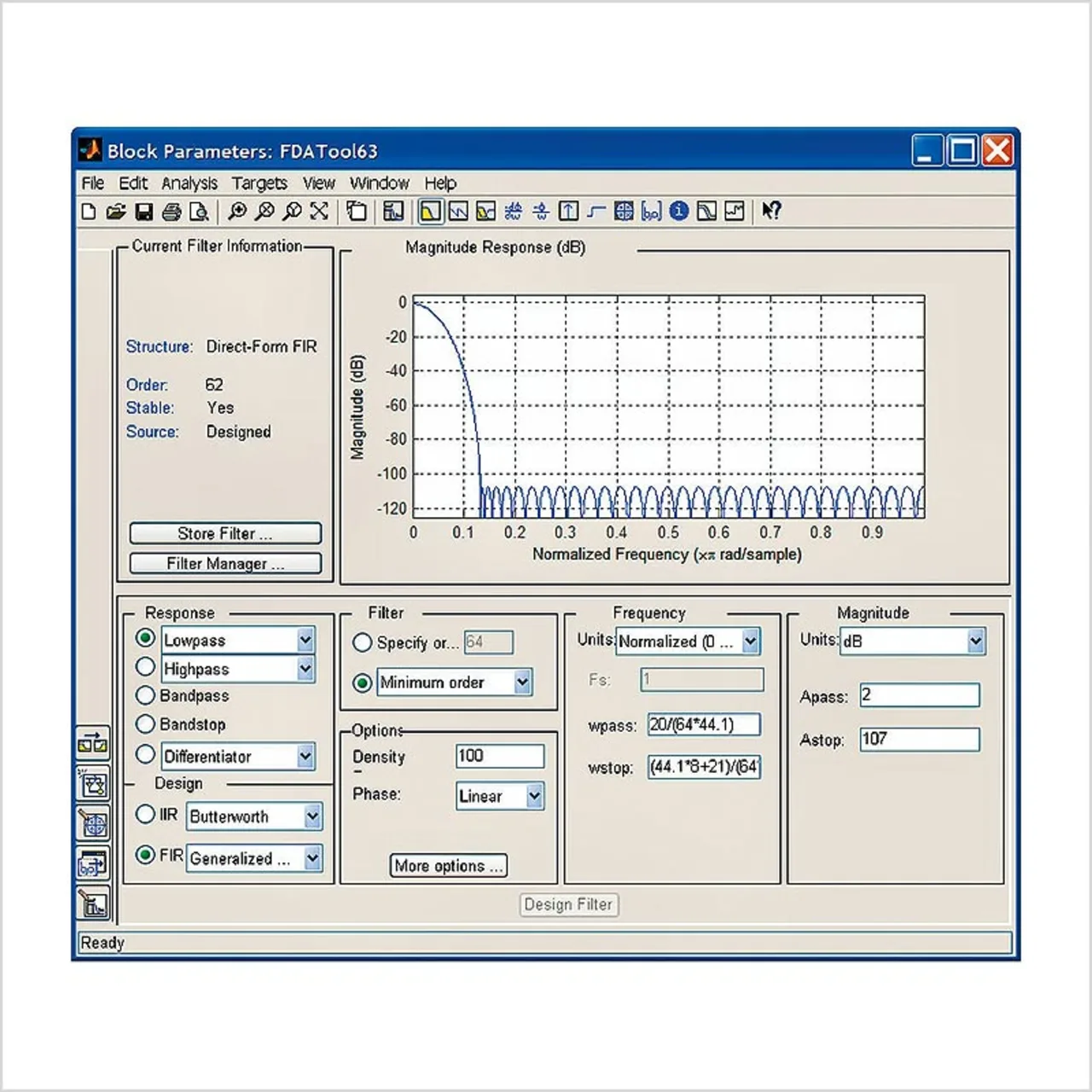

Die Schaltung wird in Simulink unter Nutzung des Synplify DSP Blocksets und des Simulink-“Filter Design and Analysis“-Tools (FDA) implementiert (Bild 3). Das FDA-Tool erlaubt die Generierung und Verifikation von beliebigen FIR- und IIR-Filtern. Es ist Bestandteil der Simulink „Signal Processing Toolbox“, auf die Synplify DSP für die Implementierung von Filterstrukturen zurückgreift. Alle Schaltungsbestandteile, die zwischen einer PortIN- und einer PortOUT-Beschreibung definiert sind und aus dem Synplify DSP Blockset oder dem FDATool stammen, generieren VHDLoder Verilog-Code.

Zur Spektralanalyse und Verifikation des Zeitverhaltens dienen FFTund SCOPE-Elemente aus Simulink Blocksets. Diese Blöcke dienen ausschließlich der funktionalen Verifikation inklusive Floating-nach-Fixed-Point-Konvertierungseffekten (Quantisierung) und werden nicht in Hardware abgebildet.

Der erste Teil der Algorithmen-Implementierung besteht aus zwei FIRFiltern: das erste Filter hat 512 Taps, das zweite 64. Der aus dem Oversampling resultierende RTL-Code beinhaltet dementsprechend 576 Multiplikationen, was eine Abbildung im FPGA aus kommerziellen Gründen nicht interessant erscheinen lässt. Ein hochkomplexes FPGA schlägt auf der Kostenseite mit mehreren tausend Euro zu Buche. Nur die komplexesten programmierbaren Logikbausteine verfügen über ausreichende Multiplikations-Ressourcen, um die Schaltung implementieren zu können (Altera Stratix-3 EP3SE110: 896 18×18-Multiplizierer, Xilinx Virtex-5 XC5VSX95TXC: 640 25×18-Multiplizierer). Alle Multiplikationen, die nicht in dedizierten Hardware-Strukturen (DSP-Blöcke) abgebildet werden, müssen aus Logikressourcen (LUT, Register) aufgebaut werden. Daraus resultiert eine hohe Auslastung der Bauteile bei gleichzeitig geringer maximaler Taktrate.

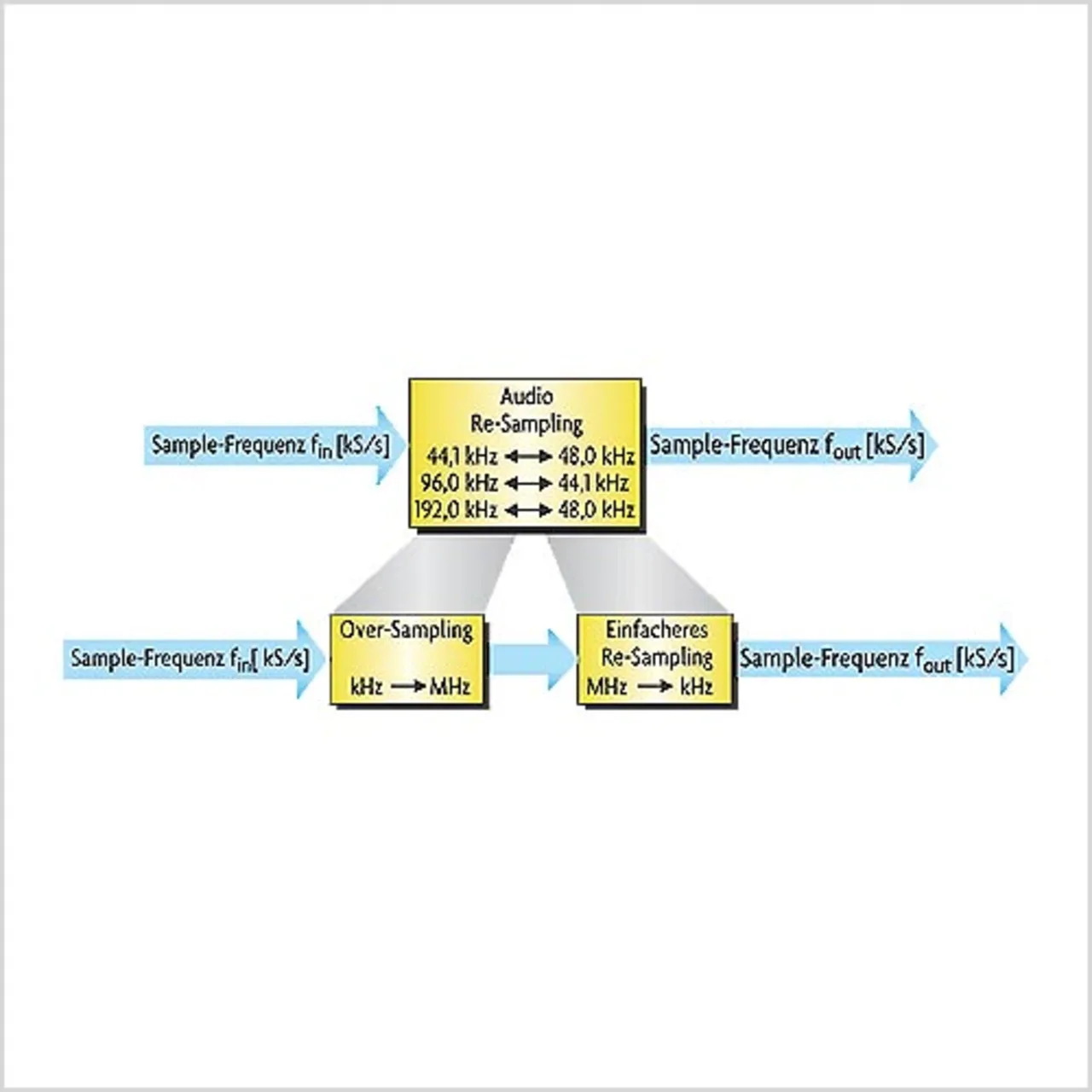

Um Signale mit unterschiedlichen Sample-Rates verarbeiten zu können, muss eine Konvertierung vorgenommen werden. An dieser Stelle sei nochmals daran erinnert, dass Audiosignale üblicherweise Sample-Rates von 44,1 kHz (CD Sample Rate) oder 48 kHz (DAT) aufweisen. Zur Konvertierung der Frequenzen (Asynchrones Re-Sampling) wird mit einer Polyphase-FIR-Filter-Struktur gearbeitet. Der Algorithmus beinhaltet zwei Schritte (Bild 2). Im ersten Schritt erfolgt das Oversampling der Frequenzen. Der zweite Schritt – lineare Interpolation – ist notwendig, um aus einer beliebigen Frequenz eine beliebige andere Frequenz zu generieren. Die beiden Frequenzen sind zueinander asynchron. Das Re-Sampling des Signals in einem einzigen Schritt würde erheblich mehr Ressourcen benötigen, da ein solches Filter entsprechend komplex ausfällt. Aus einer solchen Implementierung können mehrere Millionen Multiplikationen resultieren. Eine derartige Beschreibung ist nicht effizient und muss vermieden werden. Wird für den zweiten Schritt eine lineare Interpolation implementiert, resultieren daraus wesentlich einfachere Strukturen.

Der erste Schritt, das Oversampling, muss ebenfalls in einer möglichst effizienten Art und Weise beschrieben werden. Nur so kann man eine ressourcenschonende Abbildung im FPGA ermöglichen. Die Anzahl der insgesamt benötigten Rechenoperationen kann weiter drastisch reduziert werden, wenn dieser Schaltungsteil in mehreren, kaskadierten Stufen anstatt einer einzigen Berechnung durchgeführt wird. Bei der Implementierung des Algorithmus ist bereits darauf zu achten, welche Zielarchitektur (DSP, FPGA) die Berechnung durchführen wird. FPGAs sind – anders als Digitale Signalprozessoren – bei der Implementierung vieler Einzelmultiplikationen durch ihre Ressourcen limitiert. Mit der Ordnung des Filters steigt linear auch die Anzahl der benötigten Multiplizierer. Aus jedem „Tap“ des Filters resultiert die Nutzung eines DSPBlocks oder 18×18-Multiplizierers. Bei einer Kaskadierung der Re-Sampling-Stufen muss jedes einzelne Filter sehr viel weniger komplexe Funktionen erfüllen.

In der Theorie resultiert dementsprechend eine optimale Implementierung des Filters aus so vielen einzelnen Stufen wie möglich. Die mathematische Herleitung der Reduzierung von Rechenoperationen ist in der entsprechenden Fachliteratur ausführlich dargestellt und soll nicht Inhalt dieses Artikels sein. In der Praxis zeigt sich jedoch, dass die Kaskadierung der Re-Sampling Stufen durchaus notwendig ist, aber die Anzahl der Kaskaden begrenzt werden muss. Werden zu viele kaskadierte Stufen eingeführt, steigt die Zahl der benötigten Ressourcen wieder an, da bei der Implementierung zusätzliche Logik eingeführt wird. Wird als Zielarchitektur ein FPGA genutzt, hat sich die Zahl „2“ für die Einzelschritte des Oversampling als optimal erwiesen. Die gesamte Schaltung besteht dementsprechend aus zwei relativ einfachen Filtern für das Oversampling und einer einfachen linearen Interpolation. Diese Struktur lässt sich effizient auf ein FPGA abbilden.

- Rock ’n’ Roll im FPGA

- Steckbrief“ des Programmwerkzeugs

- Applikationsbeispiel: Sample-Rate-Konvertierung