Chip-Design-Produktivität mit Hilfe von Design Metrics optimieren

Flaschenhälse beim Chip-Design finden

Fortsetzung des Artikels von Teil 2

Transparente Arbeitsabläufe schaffen Klarheit

|

|

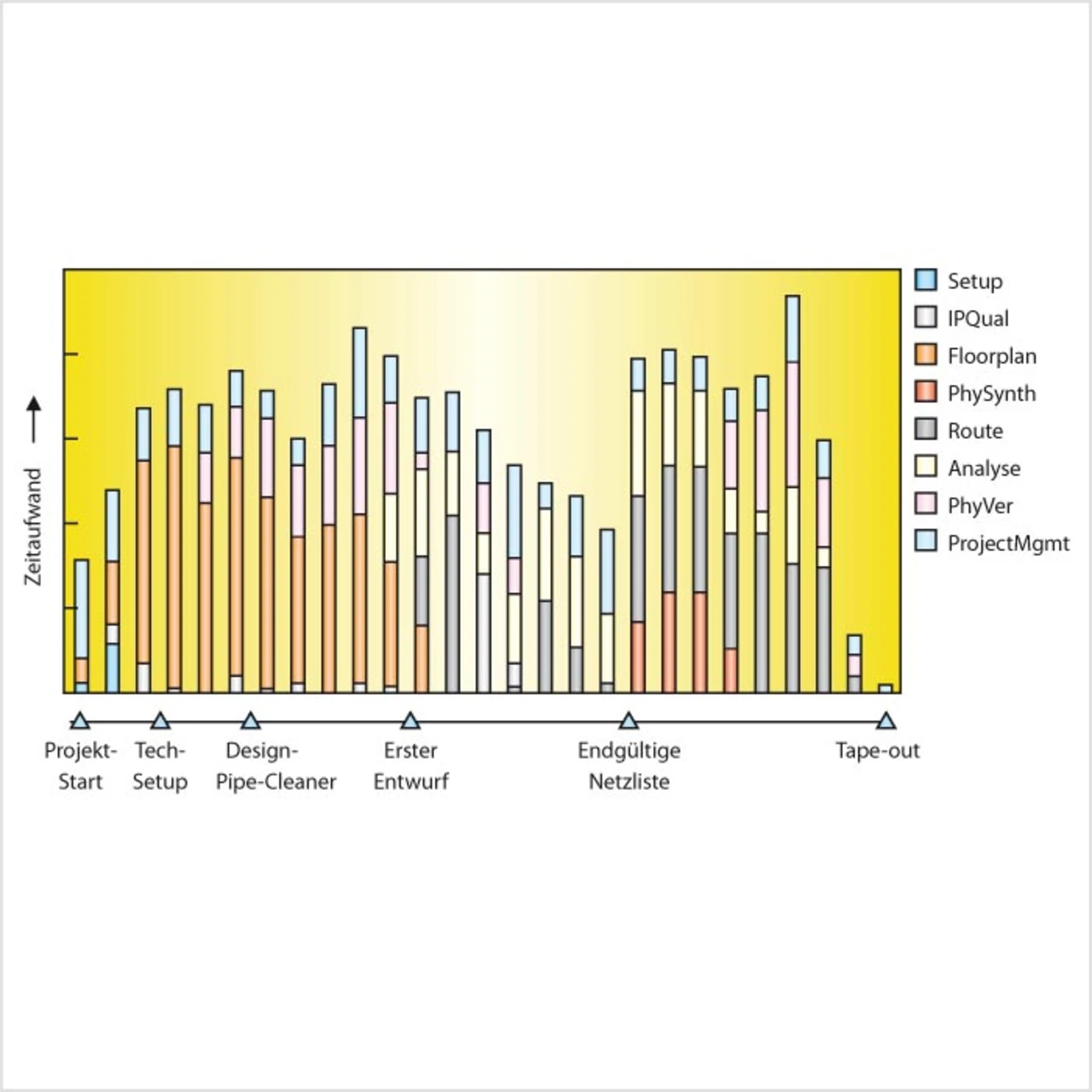

Wichtig ist, dass diese Daten sofort, also während des Projektes, eingegeben werden, denn nachträglich lassen sie sich in der Regel nicht mehr rekonstruieren. Diese Vorgehensweise erscheint dem Entwickler auf den ersten Blick als zusätzlicher administrativer Aufwand, sie ist aber im Rahmen der Durchführung eines Chip-Designs – speziell, wenn es sich um ein bezahltes Dienstleistungsprojekt handelt – ohnehin erforderlich. Zusammen mit diesen und den automatisch erfassten Daten, lassen sich Auswertungen, wie in Bild 3 und 4 dargestellt, generieren. Ferner kann man damit noch weitere Auswertungen erstellen. Bild 6 zeigt eine Auswertung, aus der sich Informationen ableiten lassen, wie viel Zeit unter anderem für „Setup des Chip-Design-Projektes“, „Synthese“, „Floorplan“, „Placement & Routing“, „Projektmanagement“, „IP-Qualifikation und Analyse“ benötigt wurde.

Darüber hinaus lassen sich noch Rückschlüsse ziehen, wie viel Zeit man denn einplanen muss, wenn ein Schritt wiederholt werden soll bzw. muss. Sehr oft kommt es vor, dass nach einer Änderung des RTL-Codes (ECO) eine neue Netzliste generiert und dann mit der geänderten Netzliste die physikalische Implementierung bis hin zu GDSII neu gemacht werden muss. Aufgrund dieser Daten lässt sich nun sehr genau vorhersagen, wie viel Zeit für eine Änderung einzuplanen ist.

Jobangebote+ passend zum Thema

Ein weiterer interessanter Aspekt ergibt sich, wenn in einem Chip-Design-Projekt der Aufwand für eine bestimmte Aufgabe (z.B. Synthese, Placement & Routing oder Setup) signifikant von anderen Projekten abweicht. So etwas würde sofort auffallen. Als Folge davon kann dann eine entsprechende Analyse eingeleitet werden, die Ursachen für diese Entwicklung und auch mögliche Abhilfemaßnahmen aufdeckt.

- Flaschenhälse beim Chip-Design finden

- Flaschenhälse beim Chip-Design finden

- Transparente Arbeitsabläufe schaffen Klarheit

- Unterschiedliche Chip-Designs anhand objektiver Kennzahlen miteinander vergleichbar

- Flaschenhälse beim Chip-Design finden