40-nm-FPGAs mit Embedded-Transceivern

Datenraten bis zu 8,5 Gbit/s

Fortsetzung des Artikels von Teil 3

Datenraten bis zu 8,5 Gbit/s

Für die schnelle Datenübertragung im Bereich von mehreren Gbit/s wurde die Common-Clock-Architektur Datenraten bis zu 8,5 Gbit/s 40-nm-FPGAs mit Embedded-Transceivern Transceiver für schnelle Datenübertragung sehen sich Forderungen nach höherer Bandbreite und reduzierter Leistungsaufnahme ausgesetzt sowie harten Vorgaben bezüglich Jitter, Rauschen, BER und Stabilität. Denn I/O-Standards mit Datenraten bis zu einigen Gbit/s kennen kein Pardon. Um alle Anforderungen zu erfüllen, werden die neuen Transceiver-FPGAs vom Typ Stratix IV-GX mit einem 40-nm-Prozess gefertigt. Daraus resultieren Vorteile für die Architektur, Taktrückgewinnung, End-to-End-Equalization und das Jitter/Rausch-Verhalten. Von Dr. Mike Peng Li (CCA) als Alternative zur konventionellen CDR-Architektur entwickelt. CCA ist eine digitale Architektur. Sie lässt preisgünstige Referenztaktgeneratoren zu und bietet eine kürzere Lock-Zeit. Dem stehen eine komplexere Architektur mit Takt- und Daten-Eingängen für die CRC gegenüber, zusätzliche Tests und eine geringere Jitter-Toleranz für die Empfänger-CRC. Außerdem ist die CCA auf kurze Entfernungen limitiert.

Jobangebote+ passend zum Thema

Hybride Architektur

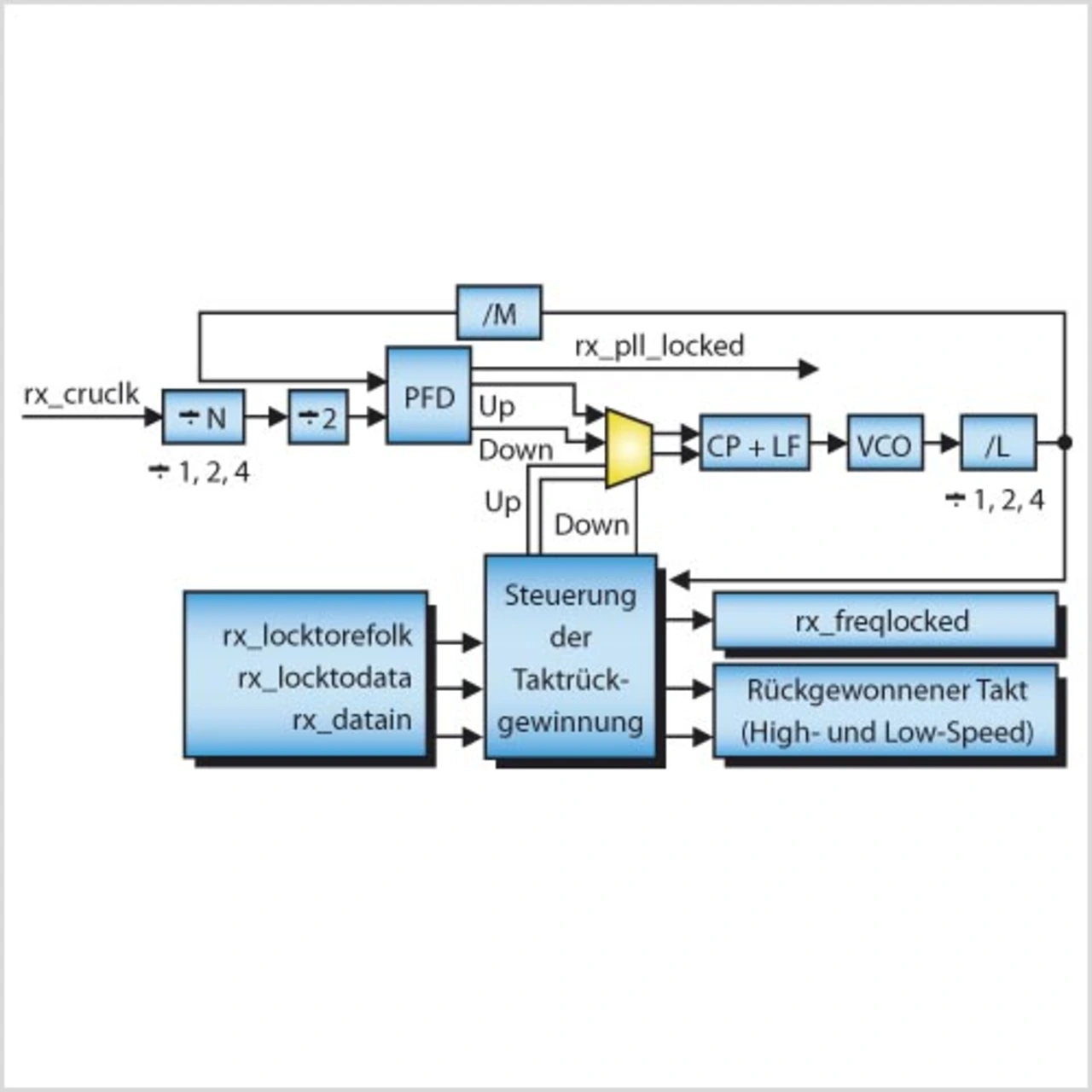

Die neuen FPGAs erweitern die konventionelle datengetriebene Architektur um zwei zusätzliche Betriebsarten sowie um die digitale Steuerung der CRC-Schaltung. Die zwei Betriebsarten sind „Lock-to-Data“ und Lock-to-Clock“, die beide automatisch oder manuell gesetzt werden können. Letztendlich wird sowohl der frequenz- als auch der phasen-zugeordnete Bit-Takt wieder hergestellt. Während diese Technik die meisten Eigenschaften der datengetriebenen Architektur beibehält, bietet der hybride Ansatz eine bessere Lock-Zeit, eine geringere Leistungsaufnahme, höhere Jitter-Toleranz und eine größere Übertragungsdichte.

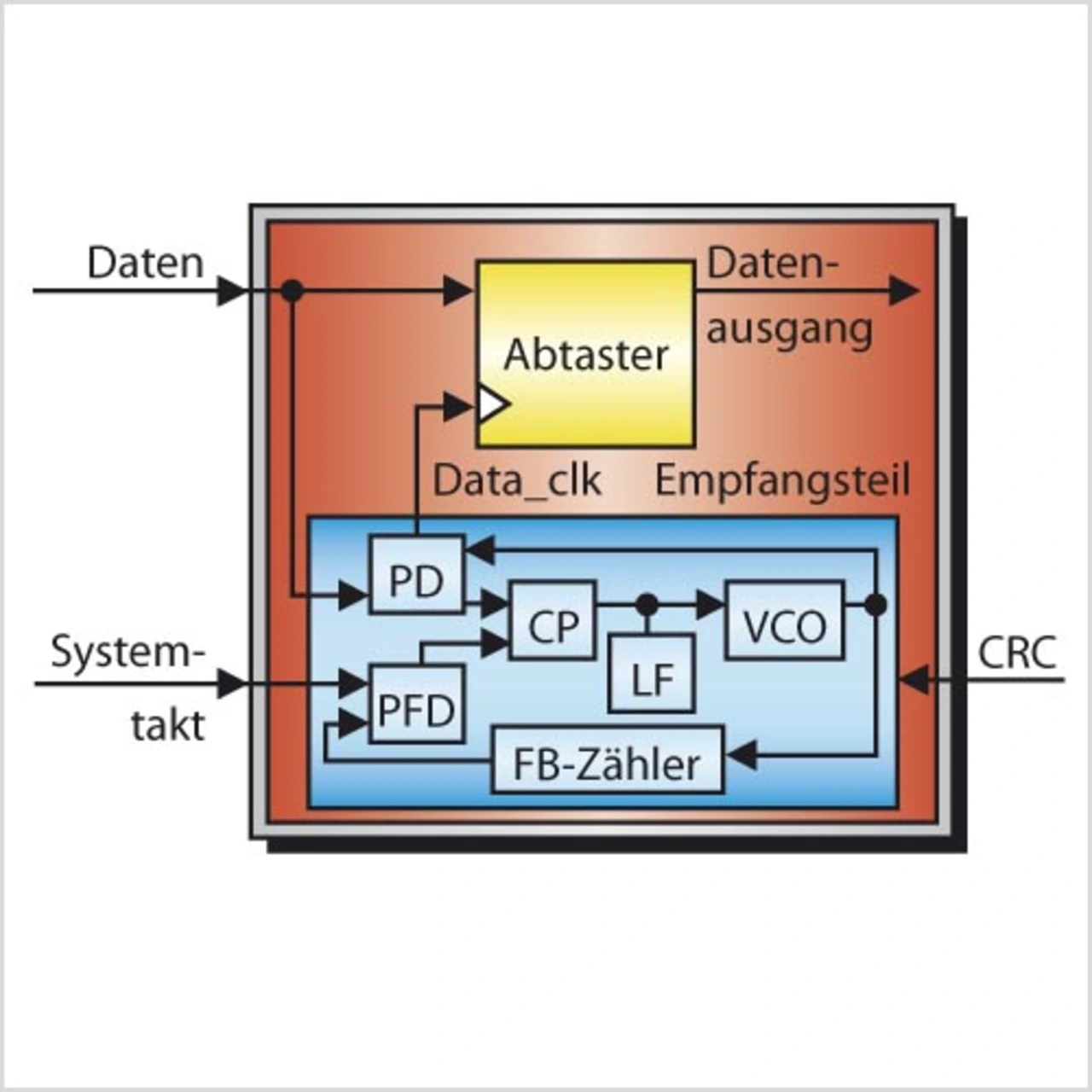

Die hybride Architektur der Takt-Wiedergewinnung ist eine Mischung aus einer analogen PLL-basierten CRC und einer phasen-interpolierten CRC (Bild 2). Dabei begnügt sich die CRCSchaltung der Stratix-IV-GX-FPGAs mit einer geringen Leistungsaufnahme. Die CRC benutzt dazu ein Half-Rate-Design, bei dem die VCO-Frequenz nur die Hälfte der Datentransferrate beträgt.

Im Vergleich zu anderen Link-Architekturen bietet die hybride Architektur eine bessere Filterung und Jitter-Reduzierung des Sendesignals oder des Referenztaktes. Dies kommt der BER des gesamten Verbindungssystems zugute. Bei der hybriden Architektur wird der Referenztakt nur während der anfänglichen Trainingsphase für die CRC genutzt und nicht während der tatsächlichen Daten-Rückgewinnung (Bild 3). Daher trägt der Jitter des Referenztaktes nicht zur System-BER bei. Im Gegensatz dazu wird bei der Common-Clock-Architektur der Referenztakt direkt für die Takt- und Daten-Rückgewinnung genutzt. So trägt hier der Referenz-Jitter zur System-BER bei und verringert das Jitter-Budget des Systems. Andererseits ist die hybride Architektur weitgehend immun gegenüber derartigen Jitter-Problemen, da der frequenzzugeordnete Bit-Takt bereits wieder generiert ist, bevor die Datenrückgewinnung beginnt.

System-Design und Systementwicklung

Die Tx/Rx-Treiber unterstützen die Auto-Kalibrierung der Abschlusswiderstände, denn unkalibrierte Terminierungen können, bedingt durch Prozess-, Spannungs- oder Temperatur-Schwankungen (PVT), Abweichungen von mehr als 30 Prozent aufweisen. Präzise Abschlusswiderstände reduzieren Reflexionen, was die System-Integrität verbessert. Ein weiteres Funktionsmerkmal auf der Senderseite ist die programmierbare Flankensteilheit (Slew-Rate): Indem der hochfrequente Anteil der Signalflanken reduziert wird, verbessert sich das Nebensprechen und die EMV.

- Datenraten bis zu 8,5 Gbit/s

- Datenraten bis zu 8,5 Gbit/s

- Datenraten bis zu 8,5 Gbit/s

- Datenraten bis zu 8,5 Gbit/s