40-nm-FPGAs mit Embedded-Transceivern

Datenraten bis zu 8,5 Gbit/s

Fortsetzung des Artikels von Teil 2

Datenraten bis zu 8,5 Gbit/s

Die saubere Takt- und Timing-Gewinnung sind wichtige Kriterien für schnelle Transceiver, denn alle Schaltungsteile produzieren ein gewisses Maß an Jitter. Der Taktgenerator basiert normalerweise auf PLL-Schaltungen, mit einem spannungsgesteuerten Oszillator (VCO) als Schlüsselkomponente. Dabei zeigen L/C-Oszillatoren ein besseres Jitter-Verhalten im Vergleich zu gängigen Ring-Oszillatoren. Für die Stratix-IV-GX-Familie hat Altera deshalb einen L/C-basierten Oszillator entwickelt, der in Bezug auf Rauschen und Jitter besonders gute Werte hat.

Während der Systementwicklung muss der Designer die Verbindung optimieren und dazu aus einer Vielzahl von Möglichkeiten die besten Einstellungen wählen (Preemphasis/ Vorverzerrung und Equalization/Entzerrung). Für diese Aufgabe bietet Altera „Pele“ an (Preemphasis Equalization Link Estimator), ein Tool, das die Preemphasisund Equalization-Einstellungen für ein gegebenes Board-Layout anhand der S-Parameter schnell optimiert.

Jobangebote+ passend zum Thema

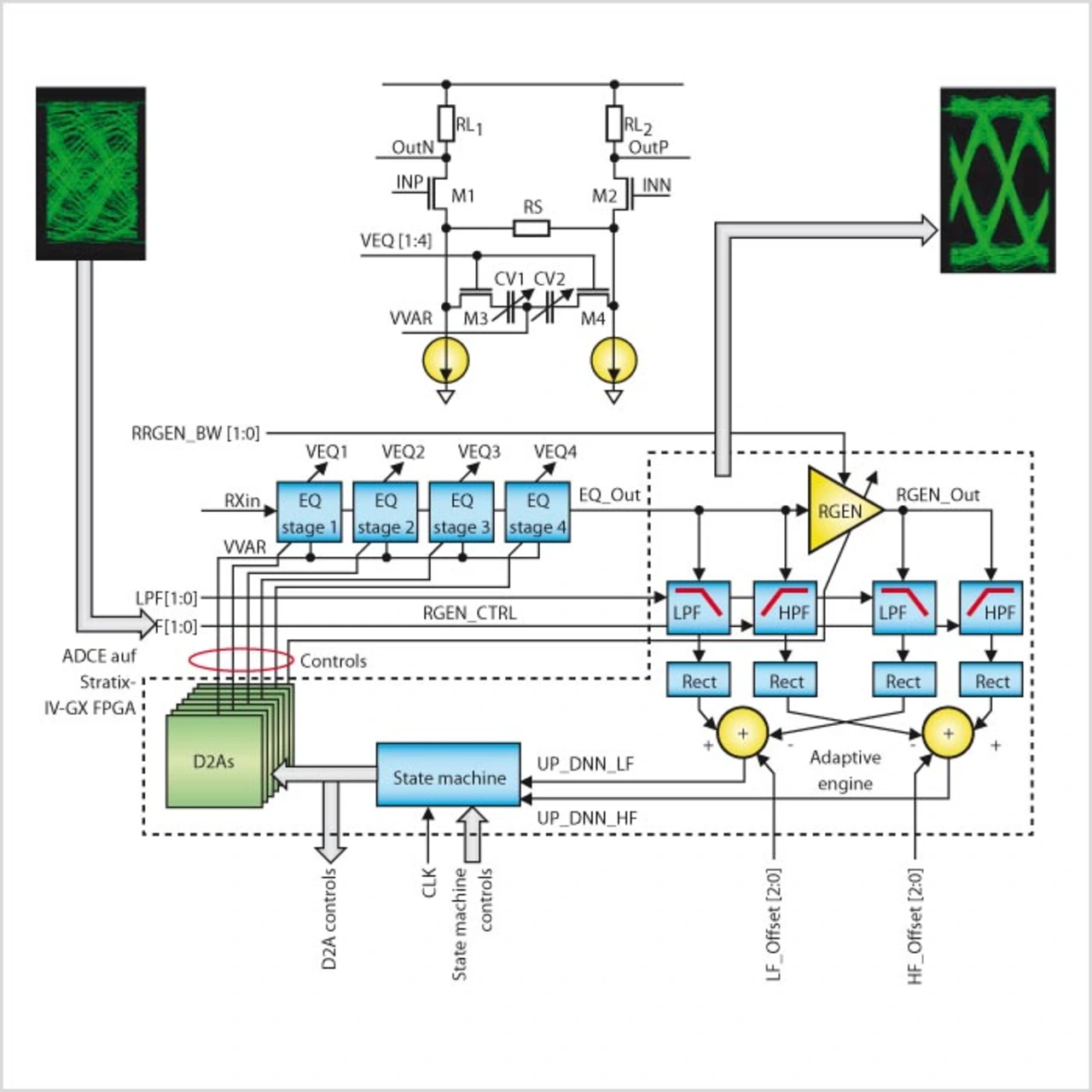

Ist die Verbindungs-Implementierung unbekannt oder kann sie nicht per Simulation adressiert werden, ist eine spezielle Hardware erforderlich, um den Prozess zu automatisieren. Dafür hat Altera die „Adaptive Dispersion Compensation Engine“ (ADCE) entwickelt. Diese Hardware-Funktion passt jeden „Link“ an das jeweilige Kundendesign an. Unabhängig von den Preemphasis-Einstellungen am Sender wählt die ADCE am Empfänger eine der verfügbaren CTLE-Einstellungen aus (Continuous Time Linear Equalizer). Die ADCE lässt sowohl eine einmalige starre Auswahl zu als auch die kontinuierliche Adaptierung. Die einmalige Adaptierung ist für zusätzliche Reduzierung der Leistungsaufnahme ausgelegt und wird während des anfänglichen Link-Trainings aktiviert. Oft ist jedoch eine periodische Anpassung in vorgegebenen Zeitintervallen oder bei einer Verschlechterung der System-BER gewünscht. Auch dann benötigt die Stufe nur während der Adaptierung Strom, da nach der Adaptierung die jeweilige CTLE-Einstellung „eingefroren“ wird. Bei der kontinuierlichen Adaptierung wird der Datenverkehr auf der Verbindung ständig überwacht, jedoch ohne ihn zu stören. Die Equalization-Einstellungen werden abhängig von Alterungsprozessen, Temperatur- und Spannungsschwankungen auf beiden Seiten der Verbindung verändert.

Die erforderliche Equalization hängt von vielen Parametern ab wie Backplane-Länge und -Material, Datenrate, Daten-Muster, Alterung, Prozess, Spannung und Temperatur. Die ADCE überwacht dazu die Ausgänge der Equalizer-Stufen und gleicht die Einstellung für mehr oder weniger Entzerrung ab (Bild 4).

Analog und digital strikt getrennt

Um die hohen Anforderungen an den Analog-Jitter zu erfüllen, muss dafür gesorgt werden, dass digitale und analoge Schaltungsteile sorgfältig voneinander getrennt sind. Bei den Stratix-IV-GX-Transceivern betrifft dies die schnellen analogen Bereiche der Sende- und Empfangspfade. Damit ermöglichen die Transceiver eine völlig unabhängige Frequenzwahl auf der Empfänger- und Senderseite. Die saubere Trennung verhindert das Entstehen unkorrelierten Rauschens.

Ein Onchip-Spannungsregler übernimmt die Aufgabe, die empfindlichen Schaltungen für jede Sende- und Empfangs-PLL (VCO, Ladungspumpe oder Schleifenfilter) zu versorgen. Die Transceiver setzen sowohl auf Entkopplung auf dem Chip als auch im Gehäuse, um von externen Stromversorgungen verursachtes Rauschen besser filtern zu können.

- Datenraten bis zu 8,5 Gbit/s

- Datenraten bis zu 8,5 Gbit/s

- Datenraten bis zu 8,5 Gbit/s

- Datenraten bis zu 8,5 Gbit/s