Aufbau einer FPGA-basierten Co-Prozessorkarte

Fortsetzung des Artikels von Teil 3

Der seriell ausgerichtete Systementwurf

Jobangebote+ passend zum Thema

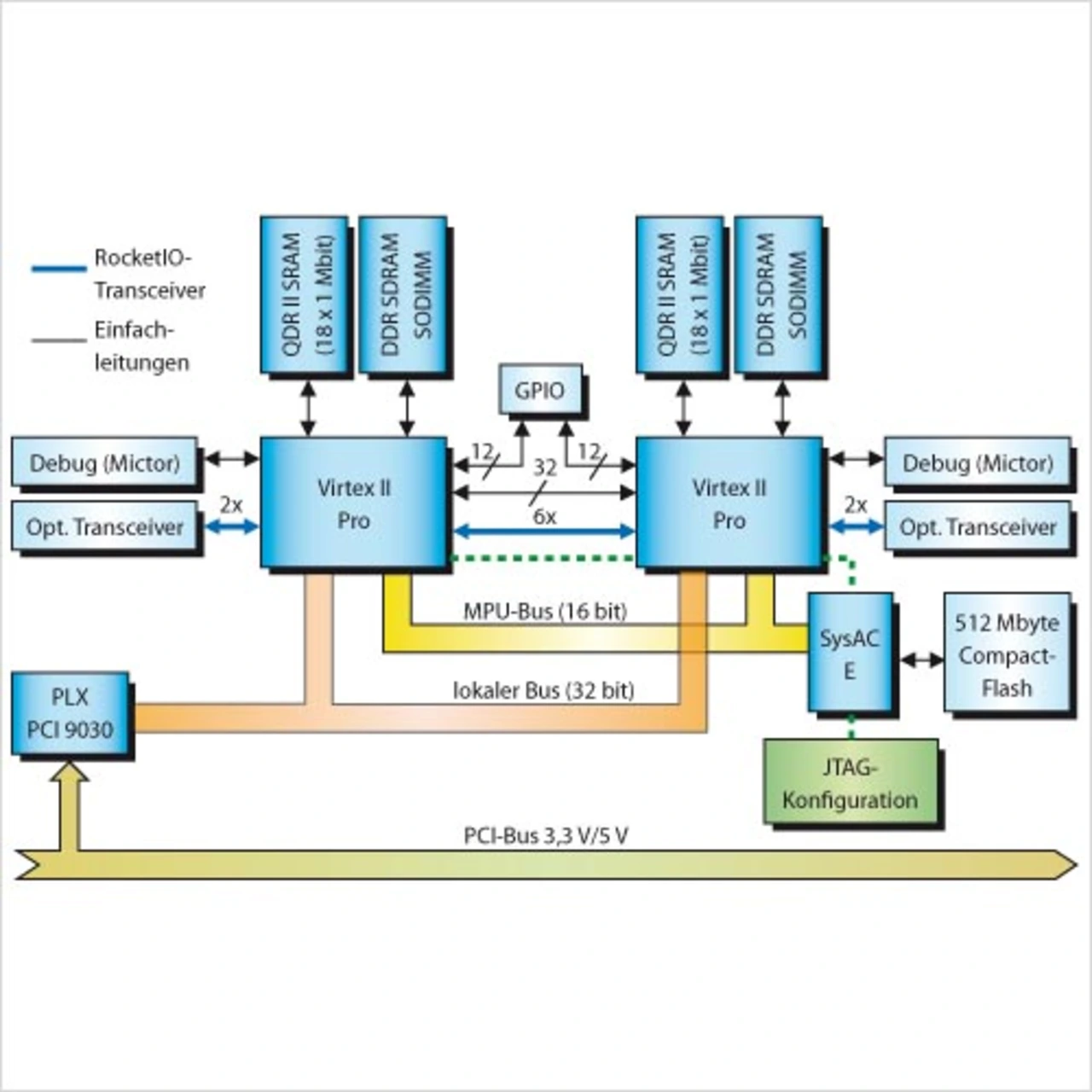

Ziel dieser Hardware-Entwicklung war der Entwurf einer FPGA-Plattform, welche durch schnelle, serielle Vernetzung zu Netzwerken beliebiger Größe skaliert werden kann (Bild 1). Den Kern bilden zwei FPGAs der Xilinx-Virtex-II-Pro-Familie (XC2VP30), welche auf einem 32-bit-PCI-Trägerboard [2] platziert sind. Der PCI-Bus dient einerseits zur Energieversorgung und andererseits zur Anbindung der Karte an einen PC-Host. Der Brückenbaustein PCI9030 von PLX Technology [3] setzt die PCI-Signale auf eine einfache lokale Busschnittstelle um, so dass im Vergleich mit einer direkten FPGA-Ankopplung an den PCIBus weniger Logikzellen benötigt werden.

Die beiden FPGAs bilden miteinander jeweils über sechs RocketIOTransceiver [4] ein lokales Netzwerk; mehrere PCI-Karten können zu globalen Netzwerken beliebiger Topologien ergänzt werden. Dafür stehen vier störungsresistente optische Transceiver zur Verfügung, die ebenfalls über RocketIO-Transceiver an die FPGAs angekoppelt sind. Die RocketIO-Transceiver sind für Datenraten zwischen 600 Mbit/s und 3125 Mbit/s ausgelegt und können über einen einstellbaren Frequenzgenerator variiert werden. Mehrere Kanäle lassen sich zwecks Steigerung der Bandbreite bündeln.

Da die RocketIO-Transceiver jeweils einen Referenz-Takt höchster Güte erfordern, werden spezielle Taktgeneratoren mit differenziellem LVPECL-Ausgang und geringem Jitter verwendet. Ebenso müssen die RX- und TX-Referenzspannungen separat mit Linearreglern erzeugt werden, um bestmögliche Stabilität und minimales Störrauschen zu gewährleisten. Das lokale FPGA-Netzwerk wird letztendlich durch weitere 32 Einfachleitungen vervollständigt.

Der SysACE-Controller von Xilinx hat die Aufgabe, ein nichtflüchtiges Speichermedium bereitzustellen (Compact-Flash-Karte) und die Konfiguration der beiden FPGAs vorzunehmen. Dies kann entweder über die externe JTAG-Schnittstelle oder acht verschiedene auf der Compact-Flash-Karte gespeicherte Konfigurationen geschehen, die über einen externen DIP-Schalter selektiert und beim Starten des Systems automatisch gelesen werden.

Schnelle Entwicklung komplexer Embedded-Systeme

Auf Basis der beiden PowerPC-Kerne und mit Hilfe der Xilinx-Entwicklungs-Software Embedded Development Kit (EDK) und Integrated Software Environment (ISE) sowie den teilweise kostenlos zur Verfügung gestellten IP-Cores lassen sich schnell und einfach komplexe, mikroprozessorbasierte Embedded-Systeme erstellen. Das Xilinx-EDK verwendet hierfür die CoreConnect-Bussysteme „On Chip Peripheral Bus“ (OPB) [5] und „Processor Local Bus“ (PLB) [6]. Eigene Komponenten lassen sich unkompliziert um die entsprechenden CoreConnect-Schnittstellen ergänzen und somit in das Design integrieren.

Neben den innerhalb der FPGAs integrierten Block-RAM-Speichern stehen jedem FPGA jeweils ein DDRSODIMM-Steckplatz – derzeitig mit jeweils 256 Mbyte belegt – sowie ein 18×1 Mbit schneller „Quad Data Rate II (QDR II) SRAM“-Speicherchip (mit 2-Word-Burst) zur Verfügung, so dass auch komplexe und speicherintensive Programme wie Betriebssysteme auf den PowerPC-Kernen ausgeführt werden können.

Im Gegensatz zu herkömmlichen SRAM-Speichern mit im Multiplex betriebenen Lese- und Schreibzyklen enthält der QDR-Speicher jeweils einen eigenen Bus für beide Operationen. Dadurch werden Verzögerungen durch Umschalten der Datenrichtungen (Bus-Turnarounds) vermieden. Jeder Datenbus wird im DDR-Modus (Double Data Rate) betrieben, womit eine theoretische Bandbreitenvergrößerung um den Faktor 4 erzielt werden kann. Im Gegensatz zum echten Dual-Port-Speicher hat der QDR-Speicher allerdings nur einen gemeinsamen Adressbus für Schreib- und Lese-Operationen. Dieser wird abwechselnd von den Read- und Write-Ports angesteuert, wodurch deutlich wird, dass der Speicher nur im Burst-Modus seine gute Leistung durch parallele Schreib- und Lesezugriffe voll ausspielen kann.

- Aufbau einer FPGA-basierten Co-Prozessorkarte

- Literatur

- In-Circuit-Debugging – schnell und einfach

- Der seriell ausgerichtete Systementwurf