Aufbau einer FPGA-basierten Co-Prozessorkarte

Fortsetzung des Artikels von Teil 2

In-Circuit-Debugging – schnell und einfach

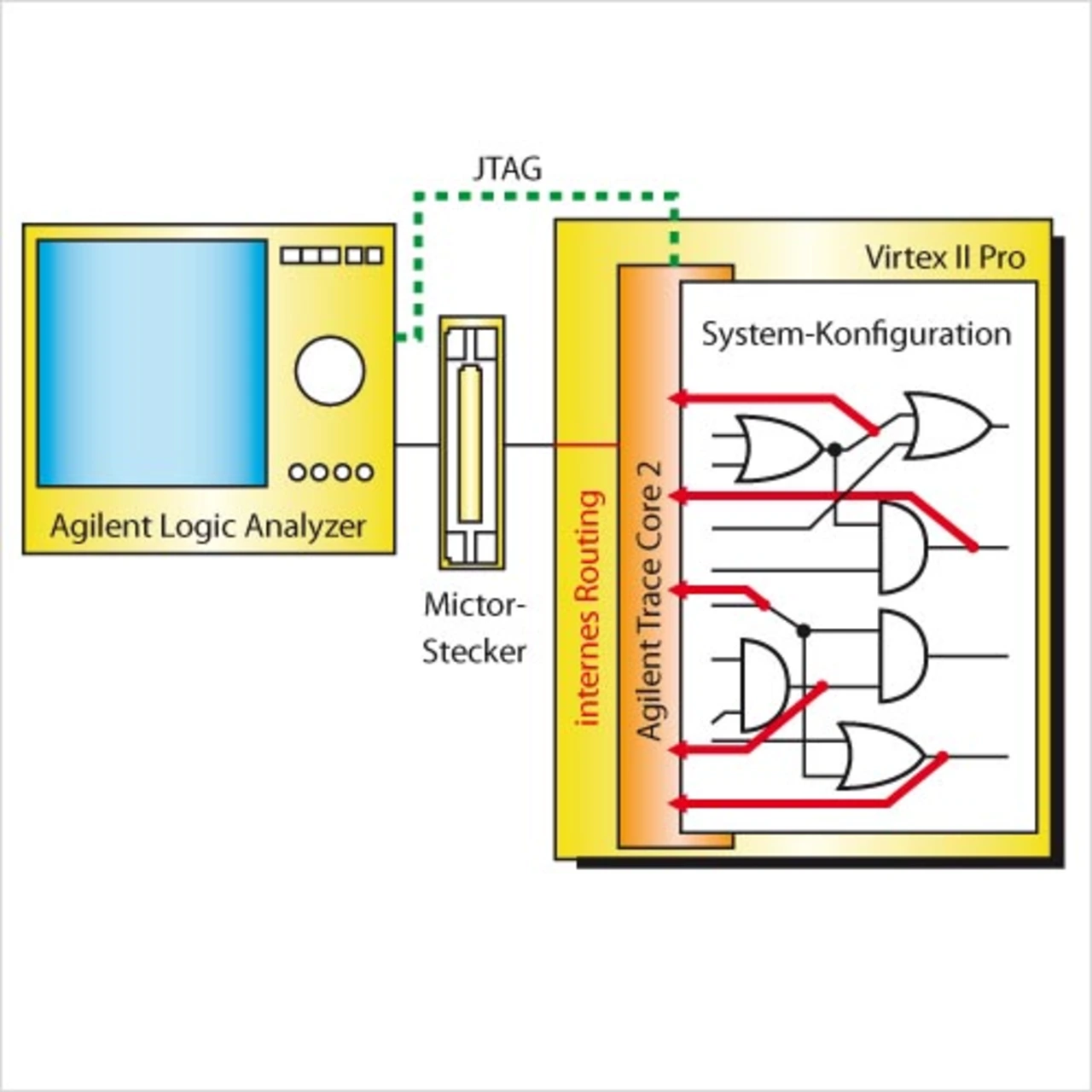

Als zusätzliche Hilfsmittel wird dem HDL-Systementwickler pro FPGA jeweils ein Mictor-Stecker (Matched Impedance Connector) zur Verfügung gestellt. Mit den entsprechenden Messund Analysegeräten lassen sich somit zur Laufzeit und in Echtzeit interne Signale der FPGAs nach außen führen, grafisch darstellen und analysieren. Die Werkzeuge von Xilinx und Agilent [7] unterstützen diesen Vorgang nahtlos; z.B. wird über Xilinx Chip-Scope Pro zunächst ein JTAG-gesteuerter Agilent Trace Core 2 (ATC2 ) in das System integriert. Die zu untersuchenden Signale werden grafisch ausgewählt, über den Mictor-Stecker wird das ATC2 mit einem Agilent-Logic-Analyzer oder Oszilloskop verbunden (Bild 2), womit zeitaufwendige eigene Debugging-Lösungen entfallen.

Jobangebote+ passend zum Thema

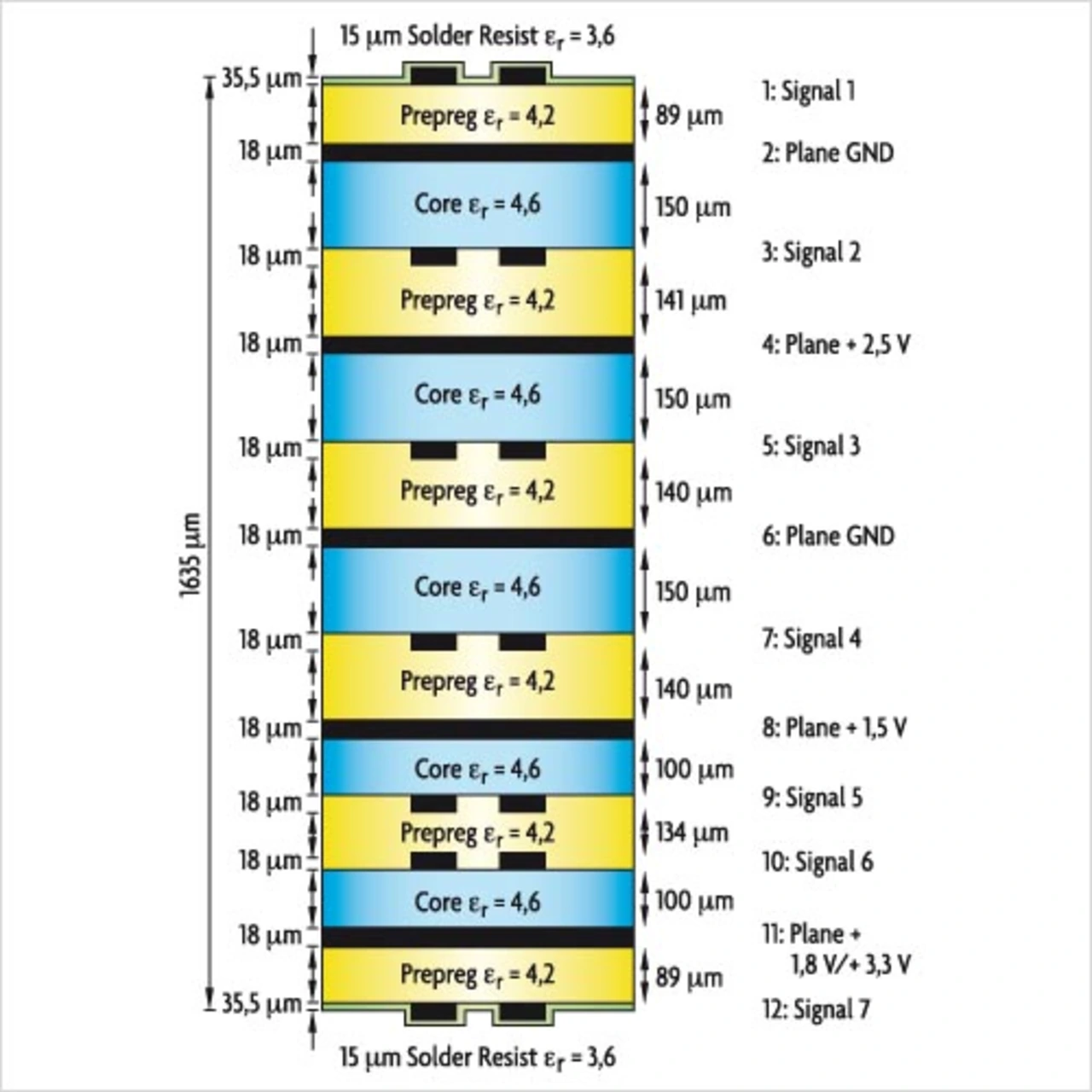

Der Platinenentwurf wurde mit dem Software-Paket Mentor Graphics SSD 2005 [8] realisiert, das Schaltbild mit Design View und das Leiterplatten-Layout mit Expedition PCB erstellt. Die Trägerplatine besteht aus zwölf Lagen (sieben Signallagen und fünf Spannungslagen), die zum bestmöglichen Schutz der Signale vor Interferenzen jeweils im Wechsel angeordnet sind. Die Kupferverteilung entlang des Leiterplattenquerschnitts muss dabei symmetrisch angeordnet werden, damit sich die Platine bei der Bestückung nicht verziehen kann und somit kalte Lötstellen vermieden werden. Der Querschnitt (Bild 3) erscheint zunächst unsymmetrisch, doch wenn man beachtet, dass die Referenzlagen den Hauptteil des Kupfers führen und diese jeweils in Abständen von ca. 300 μm angeordnet sind, kann diese Symmetrie als ausreichend betrachtet werden.

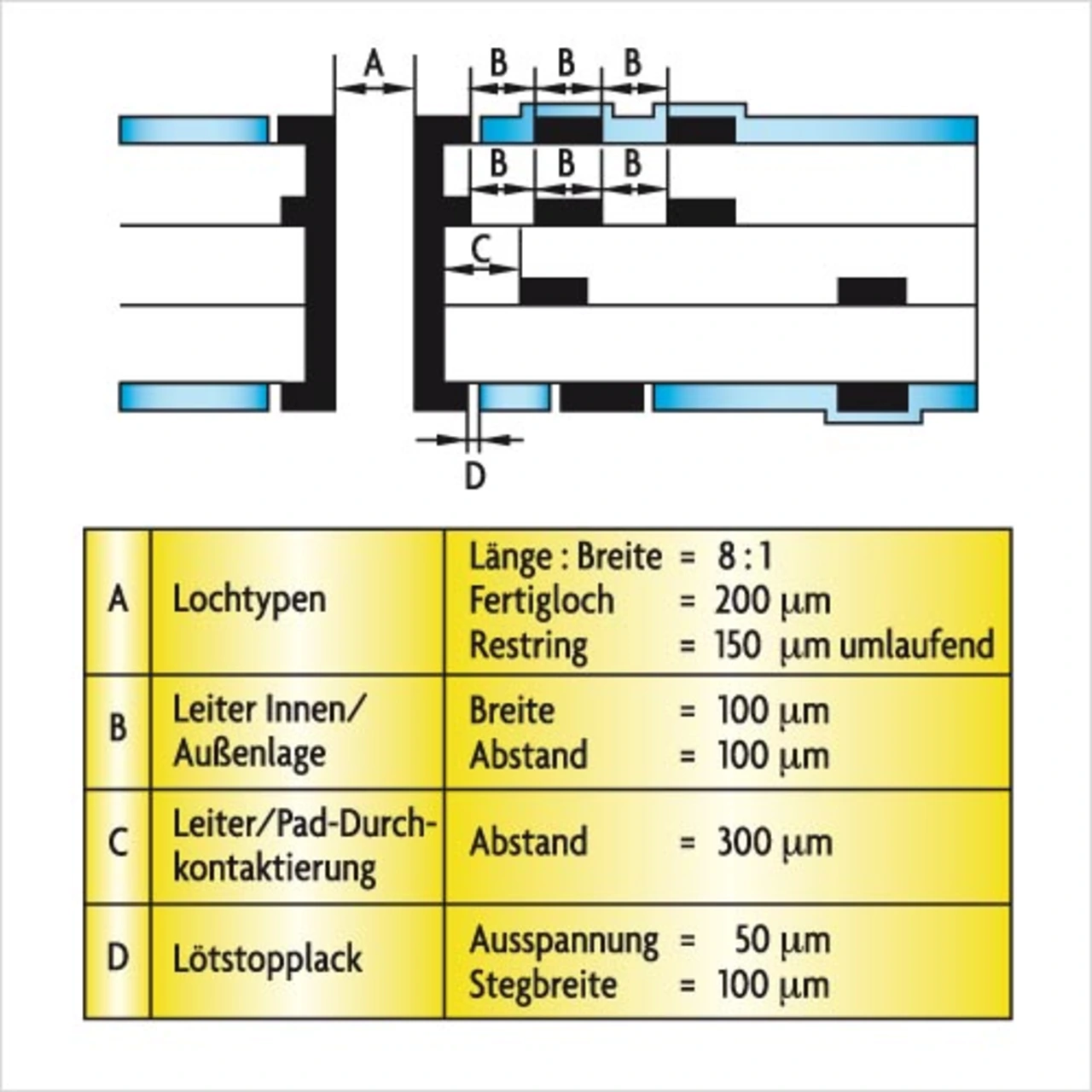

Als Basismaterial wird epoxidharzgetränktes Glasfasergewebe (FR4) verwendet. Die kleinsten Strukturabmessungen betragen 100 μm, der kleinste Bohrdurchmesser 200 μm (Bild 4), so dass bei der Leiterplattenfertigung alle Bohrungen noch mechanisch erzeugt werden können. Auf vergrabene Vias oder Sacklochtechnik wird bewusst verzichtet. Damit ist jede Leitung entweder über die Oberseite, Unterseite oder über Durchkontaktierungen für Messungen frei zugänglich.

HF-Signale = Wellen

Bei hochfrequenten Signalen bzw. Signalen mit steilen Flanken müssen die leitungstheoretischen Effekte [9] berücksichtigt werden. Als Faustformel gilt: Auf Leitungen treten wellentheoretische Effekte auf, sofern die Laufzeit digitaler Signale tp größer ist als die Hälfte der Signalanstiegszeit trise (tp ≥ trise/2). Oftmals wird diese Bedingung noch verschärft angewendet, um bessere Signalintegrität zu erlangen: tp ≥ trise/3 oder tp ≥ trise/10.

- Aufbau einer FPGA-basierten Co-Prozessorkarte

- Literatur

- In-Circuit-Debugging – schnell und einfach

- Der seriell ausgerichtete Systementwurf