Künstliche Intelligenz

Ethos-U55 beschleunigt KI-Inferenz auf Cortex-M

Der Cortex-M55 ist der erste Cortex-M-Mikrocontroller von Arm, der eine »microNPU«, eine Neural-Processing-Unit, enthält. Damit kann KI-Inferenz gegenüber Cortex-M-Controllern ohne diese Recheneinheit deutlich beschleunigt werden.

Convolutional Neural Networks (CNNs) sind eine vom menschlichen Gehirn inspirierte Rechenarchitektur, die für die Erkennung von Inhalten in Bildern und Audiosignalen angewandt wird. Die Daten liegen dabei in Form einer Matrix vor, deren Werte mit einer Multiply-Accumulate-(MAC-)Operation verarbeitet werden. Bild- und Audio-Daten werden typischerweise in 256 Stufen quantisiert, was einer Datentiefe von 8 Bit entspricht. 8-Bit-MAC-Operationen fehlen der Arm-v7-Architektur jedoch, weshalb Programmierer stattdessen 16-Bit-Befehle verwenden müssen. Arm hat unter anderem aus diesem Grund die Vektorerweiterung »Helium« in der Befehlssatzarchitektur v8.1-M eingeführt, mit der ein Cortex-M55 in einer 128-Bit-Vektor-/SIMD-Operation acht 8-Bit-MACs in einem Zyklus ausführen kann. Ohne diese Erweiterung wären acht Zyklen nötig.

Um die Leistung neuronaler Netzwerke weiter zu steigern, stellte Arm bereits im vergangenen Jahr Deep-Learning-Beschleuniger vor. Das Spitzenmodell ist der Ethos-N77, gefolgt vom Ethos-N57 und -N37. Sie dienen als Beschleuniger für die Cortex-A-CPUs, die auf Automobil-, Mobil- und andere Hochleistungsanwendungen ausgerichtet sind. Entwickler können sie mit 512 bis 2048 8-Bit-Intereger-MAC-Einheiten in binären Vielfachen konfigurieren, die 1 bis 4 Billionen Operationen pro Sekunde (TOPS) liefern.

Jobangebote+ passend zum Thema

Der neue Beschleuniger, der von Arm als Ethos-U55 bezeichnet wird, zielt auf IoT-Endpunkte und andere eingebettete Geräte mit geringem Stromverbrauch ab. Um Fläche und Leistung zu sparen, unterstützt er nur eine Teilmenge der Maschinenlernanweisungen der größeren Beschleuniger. Im Sommer soll der Ethos-U55 zur allgemeinen Lizenzierung freigegeben werden. NXP hat sich bereits als Hauptkunde angemeldet. Auch STMicroelectronics plant, die Ethos-U55-NPU ebenfalls in künftigen Produkten zu verwenden.

Leistungssteigerung in Etappen

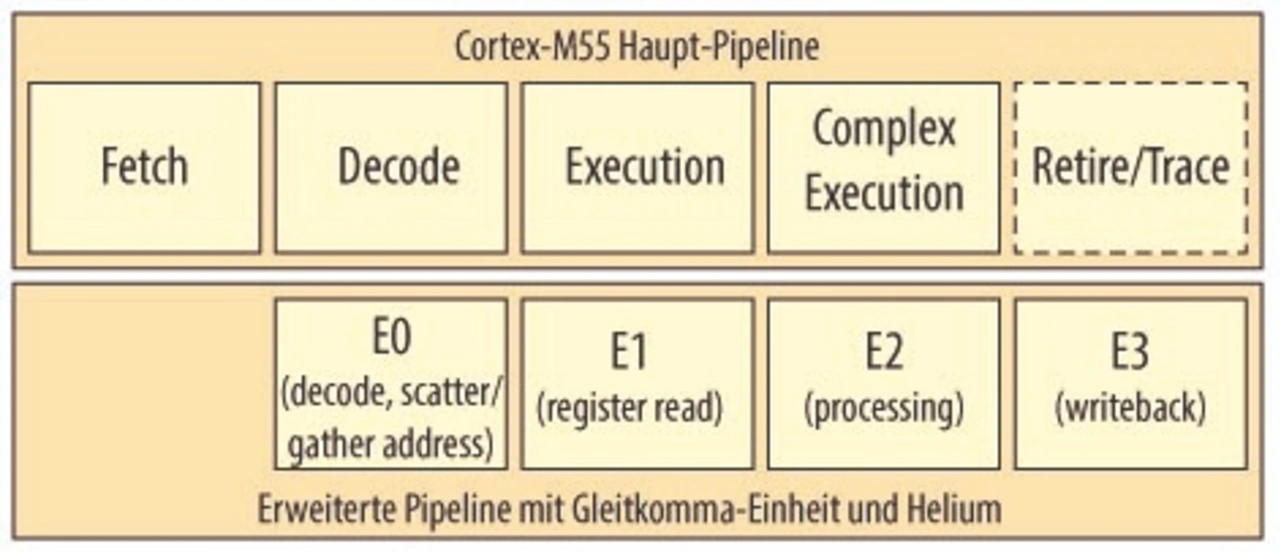

Der Cortex-M55 ist der Nachfolger des Cortex-M33 in der Arm v8-M-Reihe, aber während der M33 eine einfache dreistufige In-Order-Pipeline hat, hat der Basis-M55 vier Stufen plus eine optionale fünfte Stufe für MVE (Bild 1). Arm zählt die Retire/Trace-Stufe nicht als Teil der ganzzahligen Kern-Pipeline, da sie Debug-Befehle betrifft. Das Unternehmen spezifiziert die Leistung des M55 mit 4,2 CoreMarks pro Megahertz, nur 4 Prozent mehr als beim M33, aber DSP- und Machine-Learning-Anwendungen werden dank der optionalen Helium-Funktionen weitaus stärker beschleunigt.

Wahrscheinlich werden nur wenige Lizenznehmer den M55 ohne Helium lizenzieren, da diese Konfiguration – trotz der zusätzlichen Integer-Pipelinestufe – in etwa die gleiche Leistung pro Zyklus wie der M33 auf ungefähr derselben Fläche bietet. Allerdings erlaubt die längere Pipeline höhere Taktgeschwindigkeiten, nach Schätzung von Arm bis zu 25 Prozent.

Die Ausführung der Gleitkomma- und Vektoroperationen in einer separaten Pipeline führt dazu, dass diese Funktionseinheiten ausgeschaltet werden können, wenn sie nicht benötigt werden, oder sie in einen Schlafzustand zu versetzen, um den Status zu erhalten. Die Stromaufnahme wird daher nur dann erhöht, wenn die Operationen auch ausgeführt werden.

Läuft auch mit anderen Cortex-M-Cores

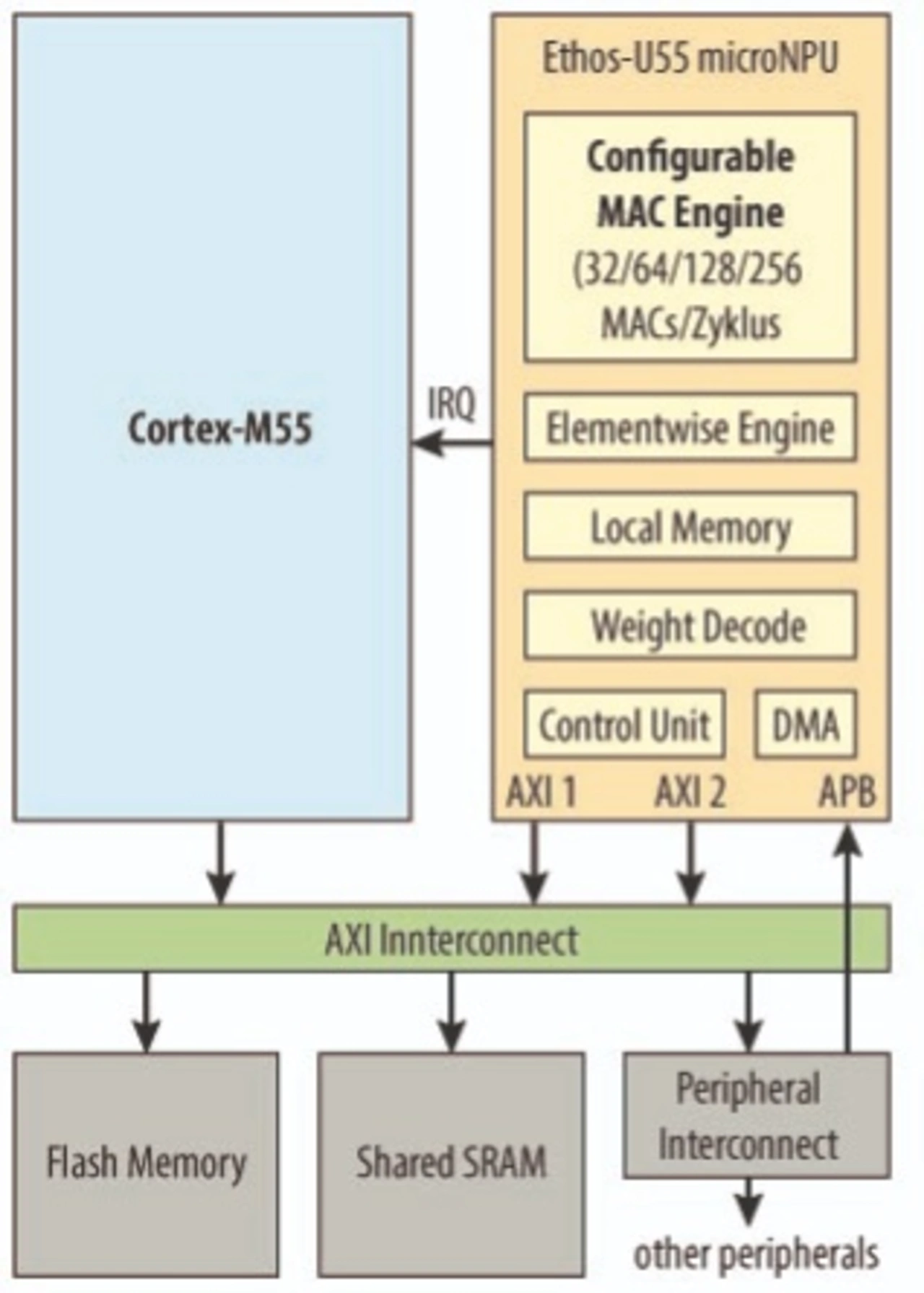

Chip-Designer können den Ethos-U55 mit jeder beliebigen CPU verwenden. Am besten funktioniert er jedoch mit dem Cortex-M55. Arm hat Ethos-U55 auch für den Einsatz mit den anderen DSP-fähigen Cortex-M-Kernen optimiert: M4, M7 und M33. Da der M4 und der M33 jedoch über AHB-Schnittstellen statt der AXI-Schnittstelle des M7 und des M55 verfügen, benötigen sie für die Verbindung mit dem U55 eine Bridge, die die Leistung verringert. Der M55 kann den ML-Beschleuniger dank seiner Arm-v8-M-Befehlssatzarchitektur auch mit TrustZone-Schutz betreiben.

Um die beiden Kerne in ein SoC zu integrieren, müssen die Designer jedoch die Größenunterschiede berücksichtigen. Der kleinste U55 hat 32 MAC-Einheiten und ist ungefähr gleich groß wie der M55; eine Implementierung mit 256 MAC-Einheiten macht ihn entsprechend größer. Dennoch ist das SRAM, das für die Speicherung der Daten des neuronalen Netzwerks erforderlich ist, viel größer als beide.

Bild 2 zeigt eine typische Systemkonfiguration, bei der ein M55 und ein U55 kombiniert sind. Um ein neuronales Netzwerk auf dem U55-Beschleuniger zu betreiben, lädt das System zunächst den vorkompilierten Befehlsstrom und die komprimierten Gewichte in den Flash-Speicher. Im SRAM liegen die Aktivierungen. Der M55-Host beginnt die Abarbeitung, indem er die relevanten Flash- und SRAM-Speicherbereiche dem U55 zuweist, der daraufhin alle Befehle autonom ausführt und nach Beendigung einen Interrupt ausgibt. Wenn ein neuronales Netzwerk eine Rechenoperation verwendet, die der U55 nicht beherrscht, fällt die Ausführung auf die CPU zurück. Ein Cortex-M kann solche Aufgaben mit Hilfe des CMSIS-NN-Arm-Toolkits für neuronale Netzwerke bewältigen, das eine Funktionsbibliothek und Werkzeuge enthält, die neuronale Netzwerke für die Ausführung auf Cortex-M-Mikrocontrollern optimieren.

Arm hat den M55 und den U55 mit wav2letter getestet, einem von Facebook entwickelten Open-Source-Modell für die Sprachübertragung. Im Gegensatz zu anderen Spracherkennungsmodellen, die auf Recurrent-Neural-Networks (RNN) basieren, nutzt wav2letter ein CNN. Bei gleicher Taktfrequenz und identischem Herstellungsverfahrens war der Cortex-M55 mit Helium bei der Inferenz sechsmal schneller als ein Cortex-M7, der aufgrund seiner sechsstufigen Doppelausgabe-Pipeline etwa 3,5-mal größer ist. Durch Verlagern der Berechnung des neuronalen Netzwerks auf den Ethos-U55 mit 128 MAC-Einheiten war er aber 50-mal schneller als der M7. Die Kombination M55+U55 ist etwa um 40 Prozent größer als ein Cortex-M7, liefert aber eine um 35 Prozent höhere Leistung pro Quadratmillimeter.

KI auf kleinen Systemen

Das Interesse an der Ausführung KI-Algorithmen nimmt zu. GreenWaves hat seinen GAP9 [1] vorgestellt und NXP hat sich bereits als »Early Adaptor« des Ethos-U55-Beschleunigers in Stellung gebracht. Google hat vor Kurzem das experimentelle TensorFlow Lite für Mikrocontroller veröffentlicht, das für die Ausführung von neuronalen Netzwerken auf MCUs mit wenig Speicher optimiert ist. Entwicklungstools zum Beispiel von Arm, NXP, Renesas und ST übersetzen die Modelle neuronaler Netzwerke in passenden Code für die jeweiligen Mikrocontroller. Eine Schlüsselworterkennung für Spracherkennung benötigt beispielsweise nur 22 KB, um den Code und die NN-Parameter auf einer Cortex-M-CPU zu speichern.

Mit der Kombination aus Cortex-M55 und Ethos-U55 steigert Arm die Leistung dieser Art von kleinen KI-Anwendungen. Das erhöht die Energieeffizient batteriebetriebener Geräte. Im Februar hat NXP bereits angekündigt, dass es der führende U55-Partner von Arm ist und plant, den Beschleuniger bei künftigen i.MX8-Upgrades einzusetzen. ST beabsichtigt ebenfalls, den M55 in seinen Mikrocontrollern der nächsten Generation zu verwenden.