Was in Flash-Speichern passiert, wenn der Strom ausfällt oder abgeschaltet wird, darf nicht dem Zufall überlassen bleiben

Strom weg – was nun?

Fortsetzung des Artikels von Teil 4

Testablauf

Zunächst findet ein Schreibvorgang des zu prüfenden Gerätes (UUT, Unit under Test) statt. Dabei handelt es sich um einen Single-Sector-Schreibvorgang, der den ANSI-ATA-Schreibbefehl verwendet und damit den Fehler vollständig isoliert. Beim Shutdown durch den Timer beträgt die Abschalt-Granularität 1 μs und ermöglicht ein Power-Down mit unterschiedlichen Sequenzen an verschiedenen Stellen im Schreibzyklus. Die anschließende Abschaltung der gesamten Versorgungsspannung und aller Signale simuliert ein Worst-Case-Szenario. Als nächster Schritt ist eine Verzögerung von mindestens 10 ms im Power-Down-Test einprogrammiert, um die Entladung möglicher Streukapazitäten abzuwarten. Schließlich wird wieder eingeschaltet, und die vorher beschriebenen Sektoren werden mit dem ANSIATA-Lesebefehl überprüft und der Auslesestatus wird verifiziert. Der Status 0x51 stellt einen Sektoren-Lesefehler dar. Der Prüfcode steht für die Anzahl der Zyklen bis zum ersten Ausfall. Zusätzliches Validieren von Daten in anderen Sektoren stellt sicher, dass Daten nicht unbeabsichtigt an eine andere Stelle geschrieben wurden. Der Umfang der erforderlichen Validierung hat erhebliche Auswirkungen auf die Testzeit.

Jobangebote+ passend zum Thema

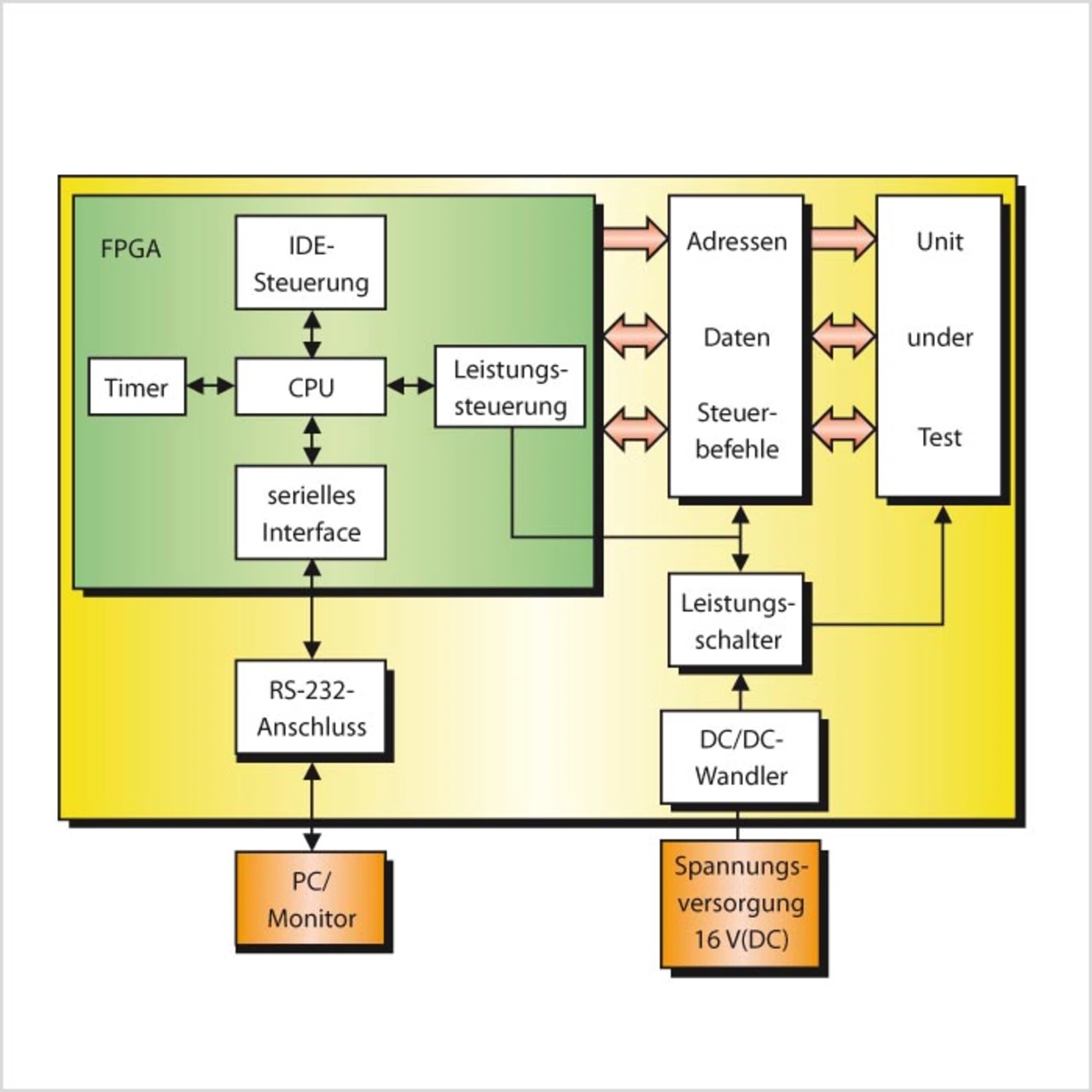

Bild 5 zeigt den beispielhaften Aufbau eines Power-Down-Testers. Der FPGA-Block enthält die gesamte Logik und das Timing für den Programmablauf. Er enthält die CPU, den Timer, den IDE-Controller, das serielle Interface und die Spannungsüberwachung. Die CPU steuert den Datenfluss zwischen allen Subsystemen innerhalb des FPGA. Der Timer regelt das An- und Abschalten mit einer Auflösung von 1 μs. Der IDE-Controller stellt I/O-Puffer für die Adress-, Daten- und Steuerzeilen des zu testenden Gerätes zur Verfügung. Die Spannungsüberwachung sendet Steuersignale an den integrierten Leistungs- und Analogschalter, und das serielle Interface bildet einen Duplex-Kommunikationskanal zwischen FPGA und Host-PC für den Empfang von Anwenderbefehlen und die Tester-Statusanzeige. Um ein reelles Power-Down-Szenario zu simulieren, sollten die Transceiver zu den Adress-, Daten- und Steuersignalen vom zu testenden Gerät abgetrennt werden. Die Analogschalter haben einen Einschaltwiderstand von 50 mΩ und einen Abschaltwiderstand von mehreren MΩ. Der Leistungsschalter schaltet die Versorgungsspannung des zu prüfenden Geräts wie vom Timer im FPGA definiert ein und aus. Der DC/DC-Wandler setzt die 16 V(DC) Eingangsspannung in die erforderlichen Systemspannungen um. Der PC hat ein generisches HyperTerminal, das Befehle an den Tester sendet und darüber hinaus den aktuellen Status des Testers anzeigt.

- Strom weg – was nun?

- Strom weg – was nun?

- Strom weg – was nun?

- Strom weg – was nun?

- Testablauf

- Probleme aufgrund von Stromstörungen in SSDs lassen sich lösen