Neue Debug-Schnittstellen

Guter Draht zum Target

Fortsetzung des Artikels von Teil 1

Schnittstellen mit hohen Bandbreiten

In der Entwicklungsphase komplexer Anwendungen kommt oft der Wunsch nach einem Systemzugang mit hohen Bandbreiten auf - vor allem dann, wenn komplexe Abläufe im SoC über einen längeren Zeitraum beobachtet und auf dem Entwicklungs-PC analysiert und ausgewertet werden sollen, also ein Echtzeit-Trace erforderlich ist. Es existieren im Wesentlichen zwei recht weit verbreitete, breitbandige Trace-Schnittstellen: : »Nexus« als ein echter Standard nach IEEE und das »CoreSight Trace Interface« von ARM, das schon aufgrund der Verbreitung der ARM-Architektur bei vielen Prozessorherstellern zum Quasistandard aufsteigen könnte.

Nexus

Nexus ist die gebräuchliche Abkürzung für »IEEE-ISTO 5001-2003, The Nexus 5001 Forum Standard for a Global Embedded Processor Debug Interface«. Dahinter verbergen sich im Wesentlichen zwei Dinge: zum einen die in so genannten »Compliance Classes« gestaffelte Definition von On-Chip-Debugfunktionen, die ein SoC bereitstellen sollte, zum anderen eine physische Debug-Schnittstelle, die zunächst einmal eine Erweiterung des JTAG-Standards beinhaltet.

Der im Nexus-Standard definierte, als »Auxilary Port« (AUX) bezeichnete physische Zugang zum SoC kann entweder parallel zu einer vorhandenen JTAG-Schnittstelle implementiert sein oder vereint die Grundfunktionen von JTAG mit den erweiterten Anforderungen eines Nexus-konformen On-Chip-Debugsystems. Diese erweiterten, in den Compliance-Classes festgelegten Anforderungen können Trace, Speicherzugriffe durch den Debugger zur Laufzeit oder auch Speichersubstitution beinhalten. Mit Letzterer lassen sich Teile des Systemspeichers mit Daten überblenden, die direkt über den AUX-Port gelesen werden.

Jobangebote+ passend zum Thema

Die Anzahl der Datenleitungen (MDO und MDI) ist je nach erforderlicher Bandbreite zum Beispiel für Trace oder Speichersubstitution erweiterbar. Auch ist es dem Hersteller überlassen, ob das Debug-Werkzeug über eine extra Taktleitung oder andere Wege Zugriff auf den Systemtakt erhält.

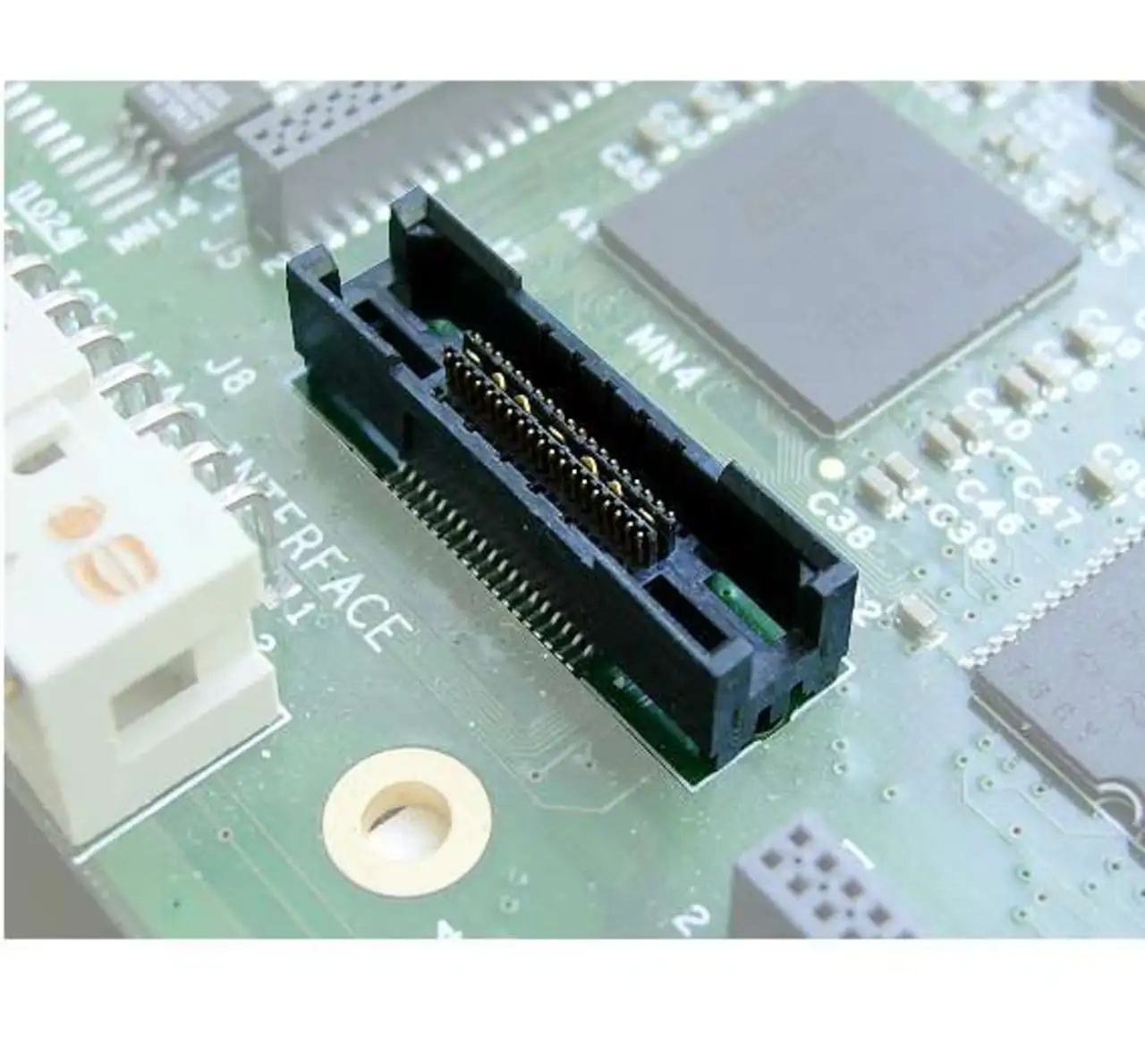

Zwar lässt der Nexus-Standard neben dem 38-Pin-»Mictor«-Stecker (Bild 2) auch »AMP System 50«- und »Glen-Air MicroD«-Verbinder zu, gibt Ersterem jedoch ausdrücklich den Vorzug.

Wie bereits erwähnt, ist die Unterstützung des Compact-JTAG-Standards durch Nexus bereits angekündigt, was eine Reduzierung der notwendigen Pins bei höherer Performance mit sich bringt. Dabei sollen die AUX-Pins wiederum zur Erhöhung der Bandbreite für Trace und Speicherzugriff beitragen.

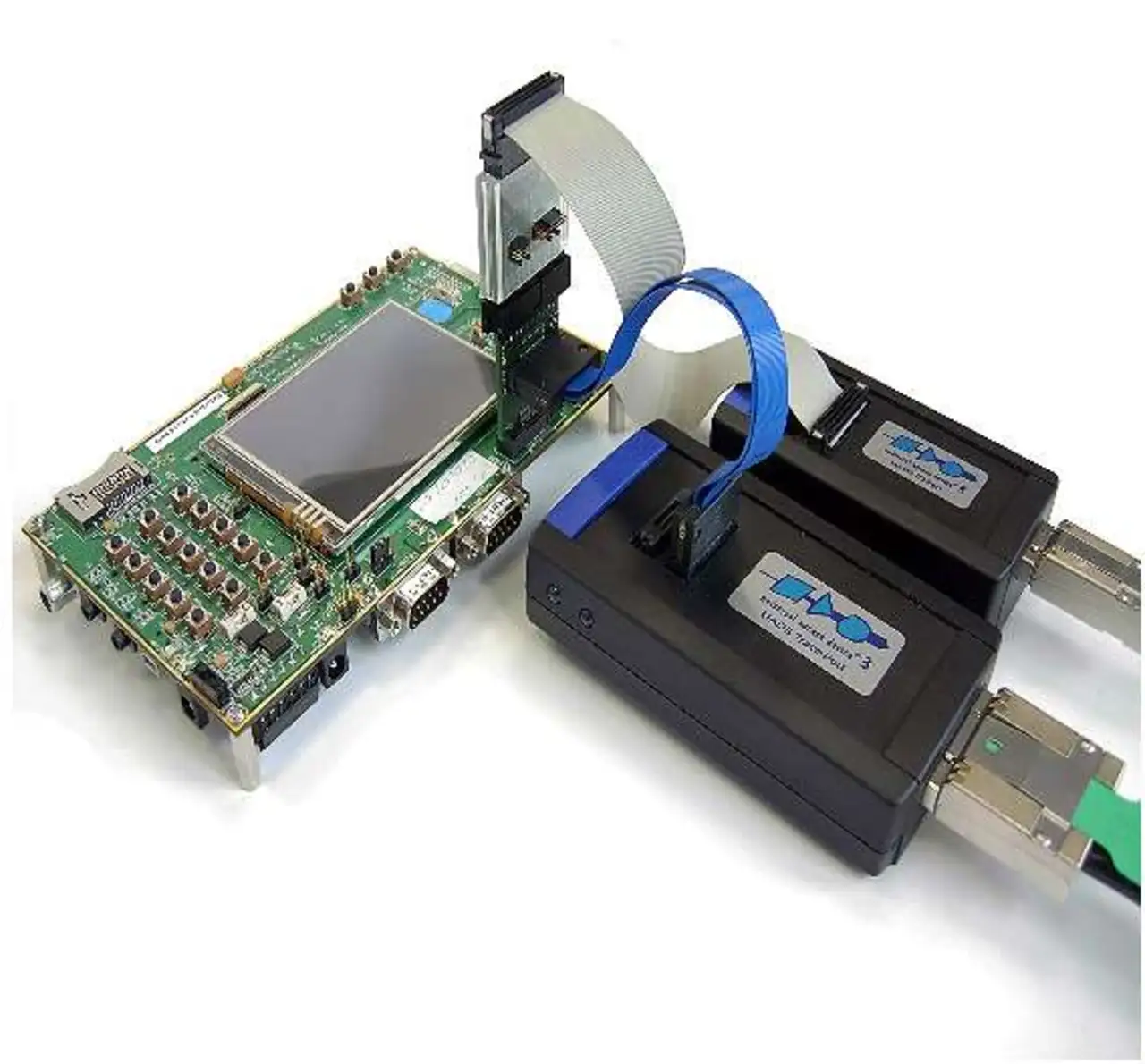

»CoreSight« Trace Port Interface Unit

Die »Trace Port Interface Unit« (TPIU) ist ein weiterer Baustein aus dem »CoreSight«-Baukasten von ARM. Im Gegensatz zum Single-Wire-Debug handelt es sich bei der TPIU um eine unidirektionale Schnittstelle mit dem Zweck, möglichst schnell große Mengen an Trace-Daten aus dem SoC heraus zu bekommen. Empfänger der Daten ist eine von ARM als »Trace Port Analyzer« (TPA) bezeichnete spezielle Hardware (Bild 3).

Dort werden die übertragenen Daten für eine möglichst effektive Kommunikation mit dem Entwicklungs-PC nicht nur zwischengespeichert, sondern bereits vorverarbeitet. Zusätzlich zu den Nutzdaten muss auch noch der Takt der TPIU zur Synchronisation übertragen werden, da dieser unabhängig vom Systemtakt ist.

Diese Taktunabhängigkeit ist durchaus sinnvoll, da SoCs heutzutage über mehrere unterschiedliche Taktdomänen verfügen, man also keinen einheitlichen Takt als Bezug vorfindet. Die CoreSight-Spezifikation lässt den Halbleiterherstellern bei der Wahl der Taktfrequenz freie Hand.

Aktuelle Implementierungen erreichen jedoch bis zu 250 MHz, was infolge einer Abtastung bei sowohl steigender als auch fallender Flanke (Double Data Rate) eine Übertragungsrate von 500 MHz pro Pin zulässt. Die eigentliche Debug-Schnittstelle wird durch die TPIU nicht ersetzt. Sowohl für die normale Debug-Funktion als auch für die Konfiguration der Trace-Schnittstelle sind JTAG oder SWD nach wie vor unerlässlich.

- Guter Draht zum Target

- Schnittstellen mit hohen Bandbreiten

- Was bringt die Zukunft?