新的高端 CPU

Arm Cortex-A77 — 更快且无摩尔定律

在 Arm 的技术日上,首席架构师介绍了新的 Cortex-A77 应用处理器。虽然 Cortex-A76 采用了基本的微型架构,但在相同的生产工艺和周期下,计算能力可以提高 20%。这是如何实现的呢?

正如前面多次提到的,Cortex-A 的开发中心位于德克萨斯州奥斯汀市附近的剑桥 Arm 总部和尼斯附近美丽的索菲亚-安提波利斯,十年前,德州仪器公司就是在这里设计了 OMAP 处理器。Cortex-A73 和 -75 代都来自法国,而节能型 Cortex-A53 和 -A55 则来自剑桥。奥斯汀上一款处理器是 Cortex-A76,这款处理器不仅安装在智能手机的 SoC 中,也应用在汽车 SoC 的 AE 版中。作为 A76 的首席架构师,Mike Filippo 现在负责基础设施应用的 Neoverse-CPU,代码名为 Deimos” 的 A77 项目由同样在奥斯汀的同事 Chris Abernathy(图 1)主导。

虽然在工作四年后,A76 在一个完全重建的微型架构上应用,建立了 Cortex-A77,但这并不奇怪:早在 2018 年,Filippo 就宣布 A76 将是至少两代 CPU 的基础,Cortex-A77 是第一个。

与它的前辈 Cortex-A75 相比,A76 在它的时代实现了由英特尔接受的知名基准 SPECInt_2006 中整数计算性能上升 35%,然而,A75 在 10 nm 过程中»仅能«使用 2.8 GHz,而 A76 7nm 的目标过程是以 3 GHz 的周期为基础。Cortex-A77 现在在相同的 7nm 过程中以相同的周期提高了 23% 的整数计算性能,这完全是通过改进微型架构实现的。在浮点计算性能方面,甚至实现了 35% (SPECFP_2006) 或 25% (SPECFP_2017) 的增长,同时能效也优于 Cortex-A76,因为»仅«多出了 20% 的功耗。测量的所有值都用于一个磁芯,即单线程计算能力。硅面比 Cortex-A76 大约 17%,原因之后会进行说明。

用于命令和数据的 L1 缓存大小为 64 KB,每个磁芯的 L2 缓存可以配置为 256 KB 或 512 KB,共享的 L3 缓存大小可达 4 MB。Cortex-A77 可以与“小型”Cortex-A55 一起在一个 DynamIQ 集群中运行。

微型结构概览

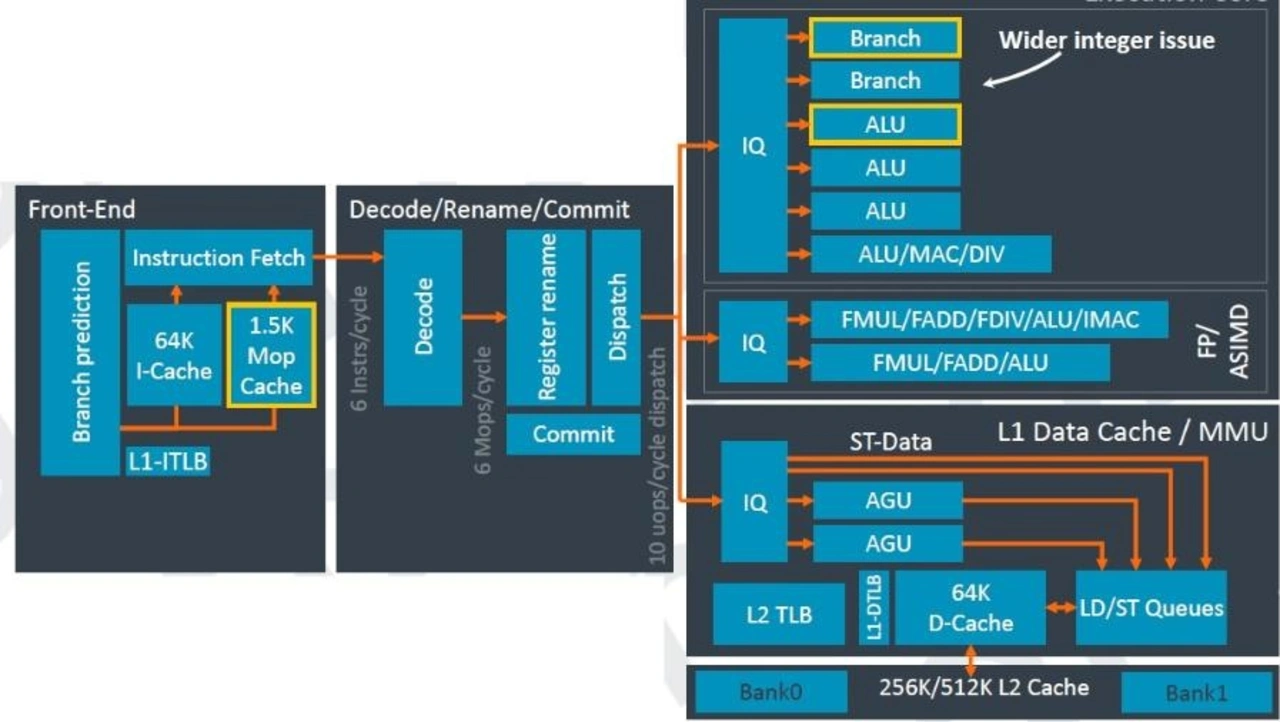

超纯量无序 CPU 现在有 6 个指令译码器,而不是 4 个,且现在有 10 个执行单元,而不是 8 个(图 2)。在前端,Arm 重新安装了通过 A76 引入的用于分支预测和指令加载的单元,称为预测定向获取,因为分支预测器会将数据直接输入到指令获取单元中。这是一种提高数据吞吐量和降低功耗的方法。

分支预测使用的是一个混合间接预测器。预测器与获取单元解耦,其最重要的结构独立于 CPU 的其余部分进行工作。它不是由 A76 的三级分支目标缓存,而是由两级缓存提供支持:一个有周期转动时延的全面的 L1 BTB(在 A76 中还称为 nanoBTB),现在有 64 个而不是 16 个条目,以及一个主 BTB,现在为 8000 而不是 6000。Cortex-A76 microBTB 的 64 个条目作为 2。由于纳米 BTB 增大,在逻辑上结构层次可能会取消。

与 A76 相比,还应该再增加程序流中正确预测分支的命中率,为此,分支预测器的带宽已经翻番达到 64 字节/周期,这意味着预取器可以在每个周期可以获取多达 16 个指令(Arm 指令为 32 位宽,Thumb 指令仅有 16 位),它能在 L1 缓存缺失时进行更早的预取,但在假设没有分支的情况下,避免了可能出现的冒泡(=流水线停顿)。

另一个新特点是额外引入的宏操作缓存 (Mop),它表示一个 1.5 K 条目(约 50 KB)的指令缓存,用于解码指令,即所谓的宏操作,以及提醒 Intel 和 AMDs x86-CPU 中的类似操作。在缓存命中的情况下,流水线中的重命名阶段直接由 Mop 提供,因此它几乎是一个 L0 缓存,其命中率根据 Arm 的信息应超过 85%。跳转指令预测的延迟在 A76 上最多只有 10 个周期,而不是 11 个周期,这是一个惊人的数值,例如比英特尔的 Skylake CPU 或三星基于 Armv8 的 CPU 自开发 M3 的 16 个周期低 30%。Mop 大约占 64K L1 缓存的一半面积。

分支单元可以在每个周期内处理 8 条 16 位指令,这将导致在加载命令前形成一个获取队列。这个队列由十二个块组成。获取单元本身仅以一半的数据吞吐量运行,即每个周期最多加载四条 16 位指令。在预测分支错误的情况下,这种结构可以对流水线的其它部分隐藏分支,而不会阻塞获取单元和 CPU 的其余部分。

译码器和寄存器重命名块每个周期可以处理六个,即比含四个指令的 A76、含两个指令的 A73 和含三个指令的 A75 更宽。为了避免功耗增长过多,实现了端口共享机制。

宏操作是在译码器的输出端上,根据 Arm 比原始命令平均大 1.06 倍。对于整数/ ASIMD /标志操作,寄存器重命名是在单独的单元中分别执行的,这些单元在不需要时钟供应时被时钟锁定。这样可以节约大量能源。如果 A77 的译码需要两个周期,则寄存器重命名只需要一个周期。宏操作每条指令的扩展比率为微操作的 1.2 倍,最后阶段每个周期可输出 10 个微操作,与 A76、A73 和 A75 相比增长 25%、67% 和 150%(对于 A76 8 个微操作/周期、对于 A75 6 个微操作/周期,对于 A73 4 个微操作/周期)。

A77 的提交缓冲区大小现在为 160,而不是 128 个条目,该缓冲区分为两种结构,用于命令管理和寄存器恢复 — Arm 将其称为混合提交系统。这允许更大的代码并行化。

执行单元

与以前一样,整数部分包含两个加载/存储单元,但是是两个而不是一个分支流水线,考虑到前端分支预测器的带宽增加了一倍,这就变得非常有意义。

现在有两个而不是三个运算器,能在一个周期内执行简单的算术操作以及在两个周期内执行逻辑操作、测试/比较操作或移位操作等较复杂的算数操作,并且和 A76 一样,有含乘法、除法和 CRC 操作的复杂流水线。

复杂运算器的整数乘法延迟从 4 个周期减少为 2-3 个周期。这会共同导致整数部分的吞吐量增加 50%。负责浮点和向量操作 (ASIMD) 的部分与 A76 中一样包含两个流水线,并且添加了用于 AES 加密的第二个流水线。

- Arm Cortex-A77 — 更快且无摩尔定律

- 加载和保存数据