Stromregelung bei Motion Control

Beobachtergestützte Strommessung mit Sigma-Delta-Modulatoren

Fortsetzung des Artikels von Teil 2

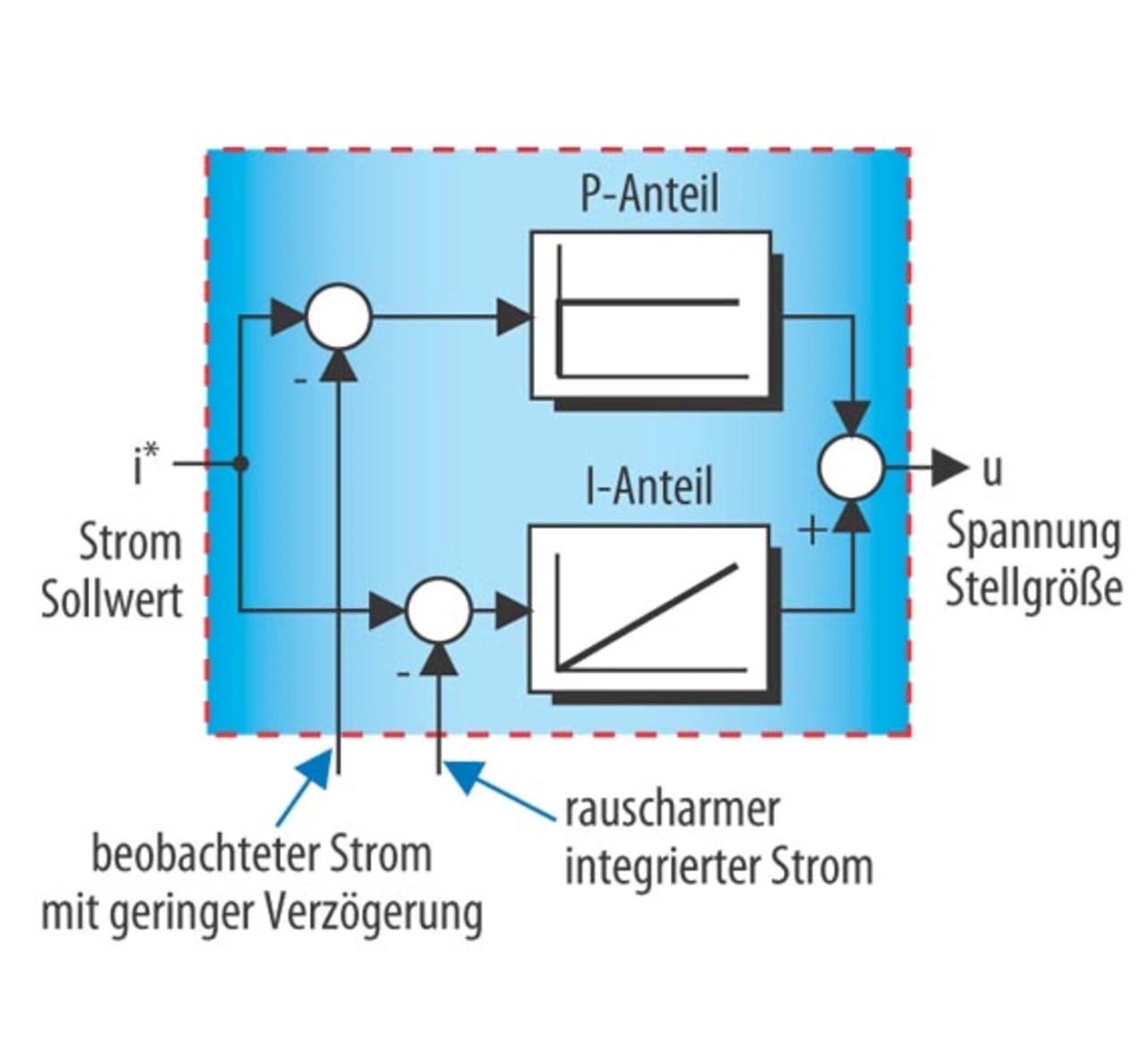

Stromregelung mit getrennter Rückführung

Die meisten in der Industrie eingesetzten Stromregelarchitekturen benutzen mehr oder weniger modifizierte PI-Regler. Der Integralanteil bewirkt die Ausregelung von stationären Regeldifferenzen. Der unmittelbar wirkende Proportionalanteil des PI-Reglers ist für die Regelgeschwindigkeit und die Stabilität maßgebend.

Eine Stromregelarchitektur mit getrennter Rückführung kann die vorteilhaften Eigenschaften von Proportional- und Integralanteil mit den Stärken der beschriebenen Strommessmethoden kombinieren. Der beobachtete, unverzögerte Strom wird für den Proportionalanteil des Stromreglers genutzt (Bild 8). Das schnelle Stromsignal des Beobachters ermöglicht die gewünschte hohe Stromregelbandbreite. Das genauere, über eine PWM-Periode integrierte Stromsignal dient als Rückführung für den Integralanteil des Stromreglers. Das Ergebnis ist eine Stromregelung mit hoher stationärer Genauigkeit ohne eventuelle aliasingbedingte Offsetfehler.

Wird der Algorithmus eines solchen feldorientierten Stromreglers in VHDL codiert, so dauert die Berechnung - je nach Implementierung und FPGA-Taktfrequenz - nur ca. 100 ns. Die Regelstrecke - Wicklungsinduktivität L und Wicklungswiderstand R - können bei einer feldorientierten Regelung als zwei einzelne und entkoppelte Systeme erster Ordnung betrachtet werden. Durch den Beobachter und die verschwindend geringe, FPGA-basierte Berechnungszeit kann die Regelung als ideal, also ohne zusätzliche Verzögerung angesehen werden.

Die Auslegung für ein einschrittiges Deadbeat-Verhalten führt zum gleichen Regelalgorithmus wie ein diskreter PI-Regler:

mit b0 = Kp und b1 = Kp(Ta/Tn - 1)

Die Reglerparameter für das Deadbeat-Verhalten berechnen sich wie folgt[5]:

Diese Auslegung ähnelt sehr der dynamischen Kompensation aus der klassischen Regelungstechnik. Insbesondere bei großen elektrischen Zeitkontanten (L/R >> Ta) wird in der Praxis die Nachstellzeit Tn nicht größer als sechs Ta (Abtastzeit) gewählt, um eine schnellere Ausregelung von Störungen zu erreichen.

Bei dem betrachteten System beträgt die Motorinduktivität umrechnet auf ein einphasiges Ersatzschaltbild 18 mH, der Wicklungswiderstand ist mit 4,4 Ω angegeben. Die PWM wird mit 8 kHz getaktet, und es werden beide Schaltflanken separat berechnet. Dadurch ergibt sich eine Abtastzeit (Ta = TPWM/2) von 62,5 µs.

- Kp berechnet sich nach (2) zu 290 V/A

- Tn berechnet sich nach (3) zu 4,12 ms

Die theoretisch berechnete Durchtrittsfrequenz fD beträgt bei diesen Parametern 2,55 kHz.

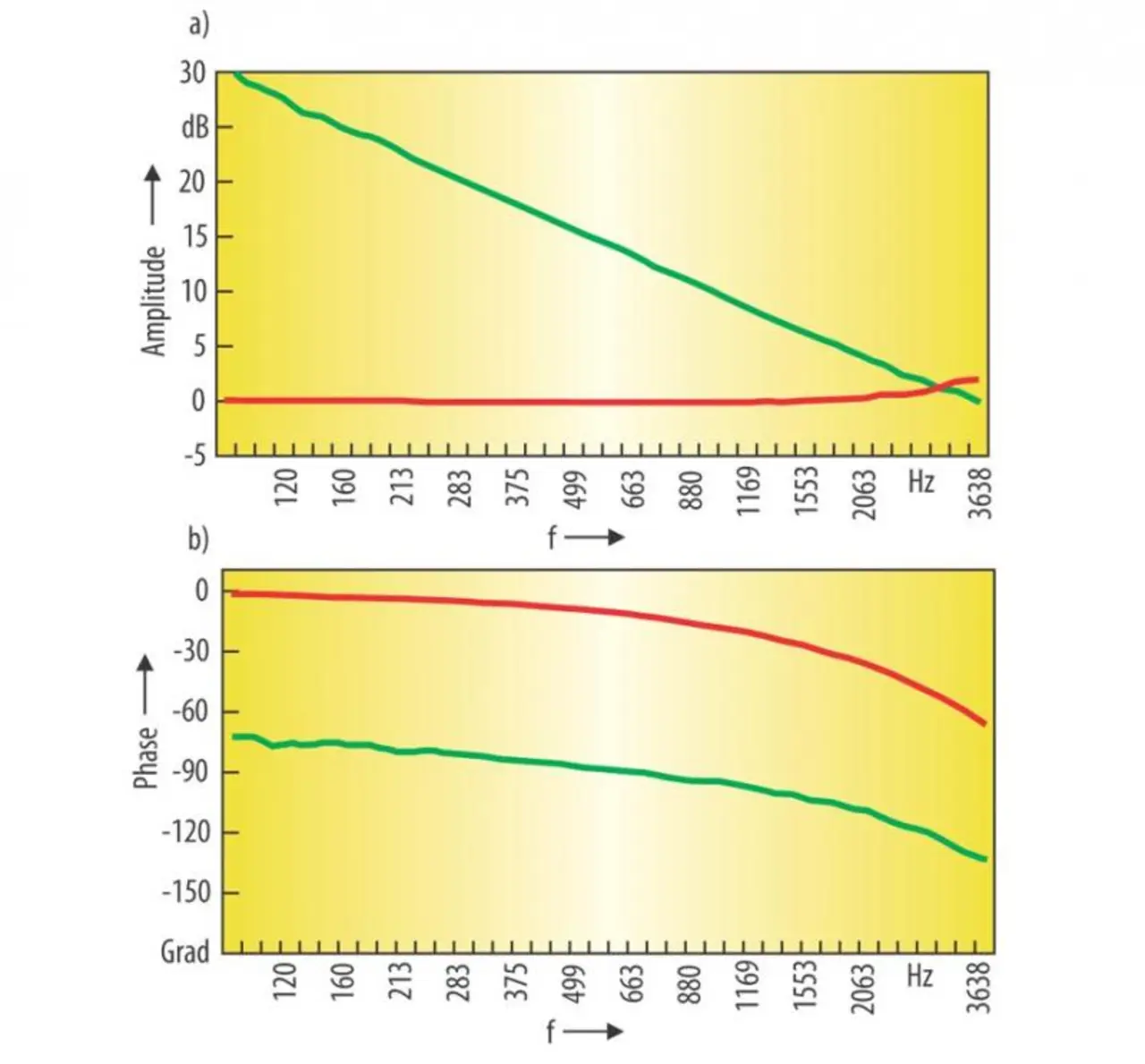

Bei Optimierungen am Versuchsaufbau wurde die Proportionalverstärkung KP etwas höher eingestellt, die Nachstellzeit Tn aber deutlich kleiner. Die sich messtechnisch aus dem Open-loop-Diagramm ergebende entsprechend höhere Durchtrittsfrequenz beträgt 3,5 kHz (Bild 9).

Diese praktisch gewählte Proportionalverstärkung ist höher als die eines Regelkreises mit Deadbeat-Verhalten. Das führt zu einem sehr schnellen, leicht überschwingenden Stromregler, was aus Sicht des überlagerten Drehzahlreglers durchaus gewünscht ist und zu einer dynamisch steiferen Servo-Achse führt.

Das betrachtete System erreicht eine Closed-loop-Stromreglerbandbreite bis zu 4 kHz bei nur 8 kHz Schaltfrequenz, was auch dem theoretisch Möglichen entspricht. Durch die FPGA-basierte Regelung mit Strombeobachter kann entweder die Dynamik eines Motion-Control-Systems bei gleicher Schaltfrequenz gesteigert werden, oder die Schaltfrequenz kann bei vergleichbarer Bandbreite zur Verringerung der Verluste gesenkt werden, um z.B. den Wirkungsgrad zu verbessern.

- Beobachtergestützte Strommessung mit Sigma-Delta-Modulatoren

- FPGA basierte Strommessung mit getrennter Signalrückführung

- Stromregelung mit getrennter Rückführung

- Literatur und Autoren