Stromregelung bei Motion Control

Beobachtergestützte Strommessung mit Sigma-Delta-Modulatoren

Fortsetzung des Artikels von Teil 1

FPGA basierte Strommessung mit getrennter Signalrückführung

Jeweils ein ΣΔ-Modulator pro Phase generiert einen mit 20 MHz getakteten Datenstrom, der jedoch keine digitalen Wörter beinhaltet, wie man sie von SAR-Umsetzern kennt. Um ein solches Datenwort zu generieren, muss das Quantisierungsrauschen der Datenströme noch mit einem digitalen Filter unterdrückt werden.

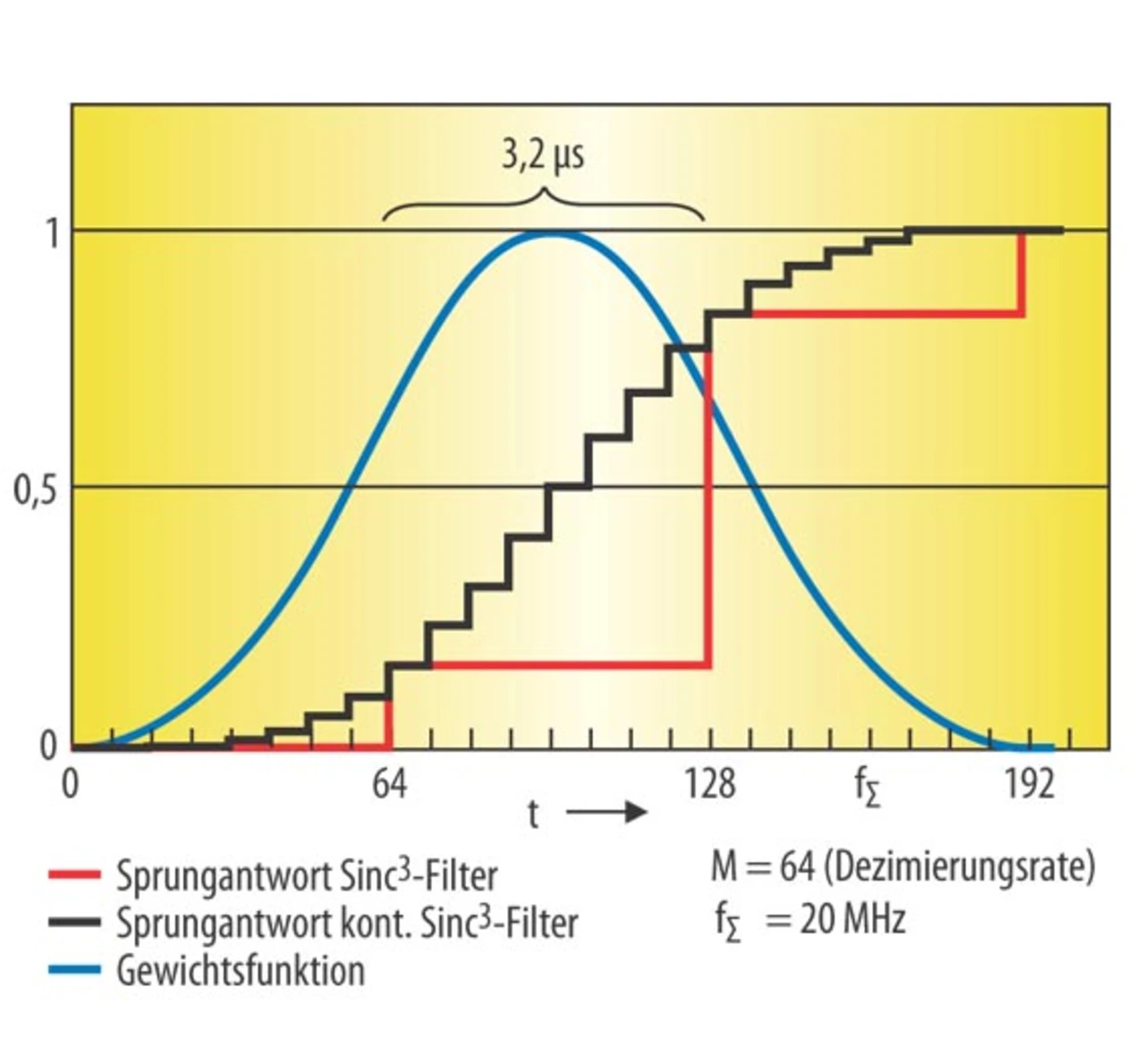

Ein sehr einfach zu realisierendes Filter ist das Sinc³-Filter. Es bietet ein gutes Verhältnis der Filtereigenschaften bezogen auf die Anzahl der benötigten Logikelemente. Für Dezimierungsraten von 16 bis 256 ist das Sinc³-Filter eine gute Wahl (Bild 5). Die Dezimierungsrate M bestimmt dabei die Signalverzögerung und das Signal/Rausch-Verhältnis (SNR) bzw. die effektive Anzahl von Bits des Datenwortes (ENOB).

Durch die digitalen Sinc³-Filter sind analoge Filter zur Störunterdrückung nicht notwendig. Jeder Phasenstrom wird im FPGA mit bis zu drei Filtern ausgewertet:

1.) Filterung mit geringer Signalverzögerung für die Überstromerkennung mit ausreichender, geringerer Genauigkeit. Eine Dezimierungsrate M = 16 führt hier zu ca. 2 % Toleranz.

2.) Filterung mit mittlerer Signalverzögerung für den Proportionalanteil des Stromreglers mit ca. 12 bit Genauigkeit bei einer Dezimierungsrate von M = 64.

3.) Hochgenaue Filterung durch Integration über eine Periode des PWM-Trägersignals (TPWM = 1/fs) . Diese Technik ist vergleichbar mit Dual-Slope-A/D-Wandlern, wie sie in Digitalmultimetern verwendet werden.

Die effektiv wirksame Abtastfrequenz des Standard Sinc³-Filters wird über die Taktfrequenz des ΣΔ-Modulators fΣΔ und die Dezimierungsrate M bestimmt. Bei Nutzung einer Modulatorfrequenz von fΣΔ = 20 MHz und einer Dezimierungsrate von M = 64 wird das Stromsignal alle 64 × 50 ns = 3,2 μs abgetastet. Die Verzögerung ist akzeptabel für PWM-basierte Regelungsarchitekturen, solange sie in Addition zu der Verzögerung zur Berechnung der Regelalgorithmen die Signalabtastzeit von einer halben PWM-Periode T s = 1/(2fs) nicht überschreitet.

Unter Nutzung zusätzlicher Logikelemente im FPGA kann mit einem erweiterten Sinc³-Filter mit identischen Eigenschaften eine Abtastzeit von z.B. 0,4 µs (3,2 µs/8) erreicht werden. Ein solches Dezimierungsfilter mit erhöhter Abtastrate ist beispielsweise für hysterese-basierte Regelarchitekturen von Vorteil, um eine zu grobe Zeitdiskretisierung mit nur 3,2 µs Auflösung zu verhindern.

FPGA-basierter Strombeobachter

Dank der parallelen Algorithmenverarbeitung innerhalb von FPGAs wird die Berechnung von aufwendigen Algorithmen in deutlich weniger als 1 µs ermöglicht. Ein Prozessor würde durch seine sequenzielle Befehlsabarbeitung wesentlich mehr Zeit für die gleichen Rechnungen benötigen.

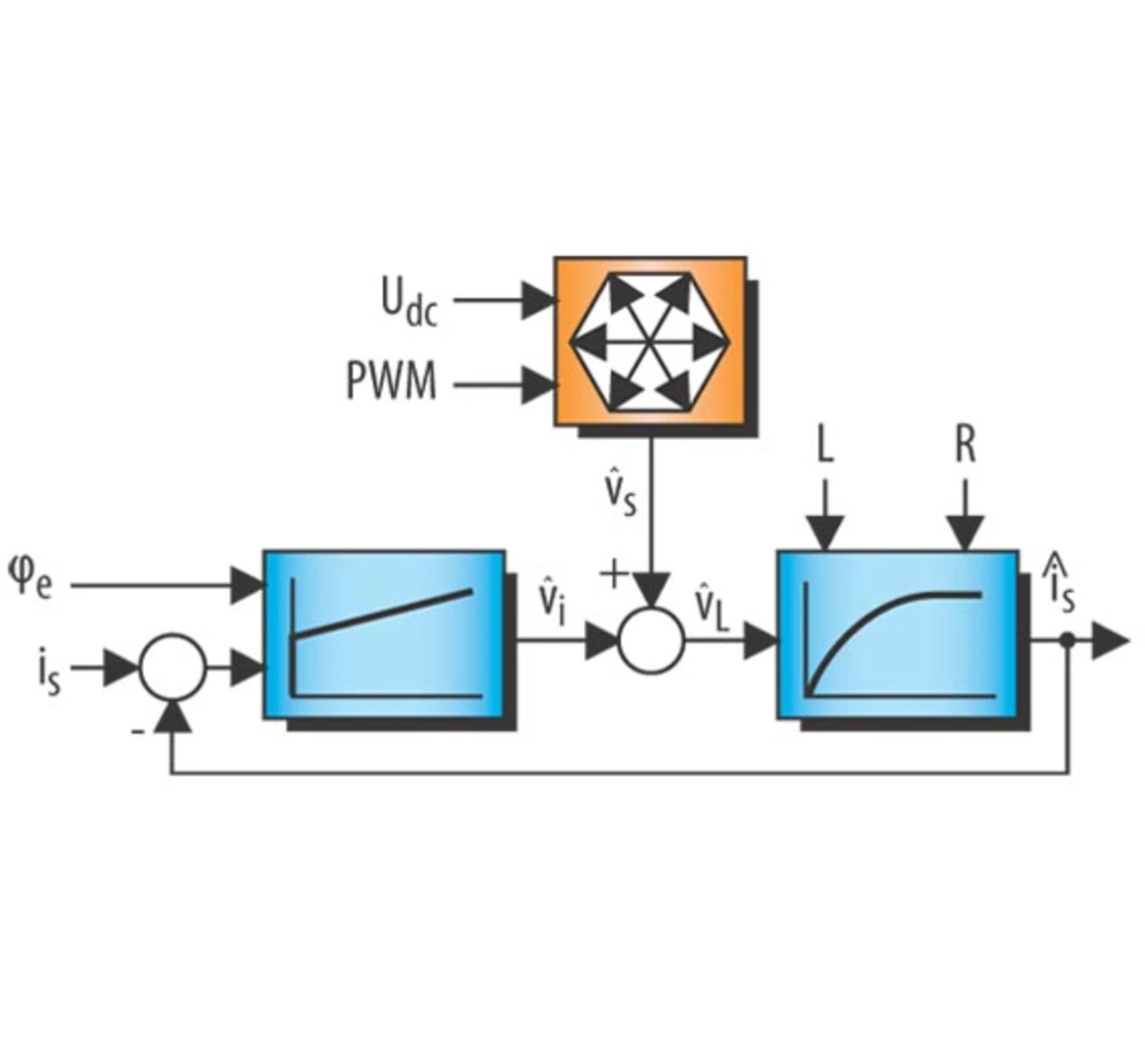

Verbleibende unerwünschte Effekte des Sinc³-Filters sind die filtereigene frequenzabhängige Signaldämpfung und die durch die Filterung verursachte Phasenverschiebung. Beides kann durch einen FPGA-basierten Strombeobachter vermieden werden. Er basiert auf einem vereinfachten Maschinenmodell mit der Wicklungsinduktivität L und dem Wicklungswiderstand R als Modellparameter (Bild 6). Eingangsgröße ist zusätzlich zu den durch die Sinc³-Filter gemessenen Phasenströmen und der Rotorposition die Ausgangsspannung der Leistungsendstufe.

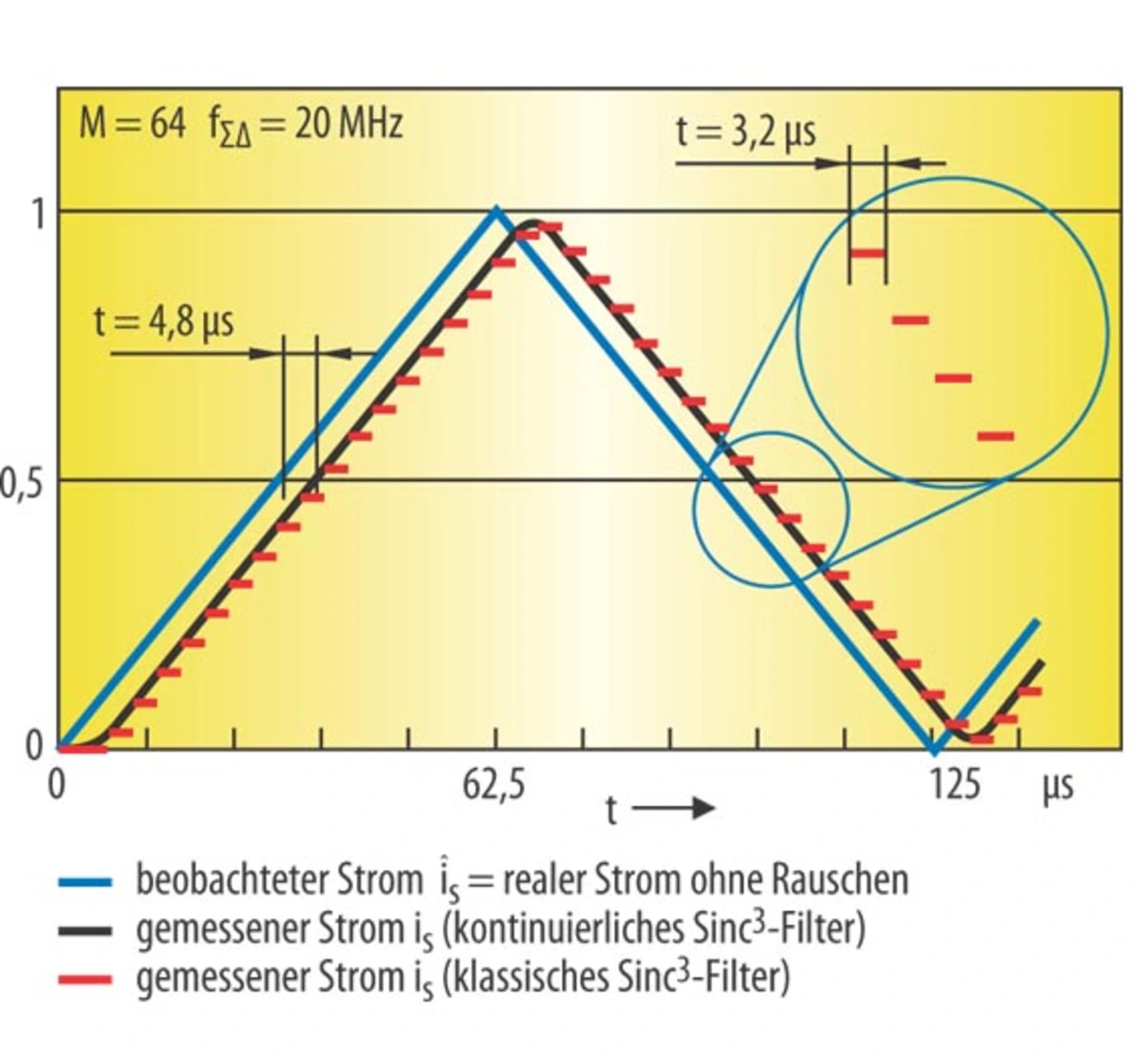

Sie kann einfach über die Zwischenkreisspannung und und die Gate-Signale der Leistungshalbleiter berechnet werden. Der Beobachter liefert ein unverzögertes und ungedämpftes Stromsignal mit effektiv unterdrückten EMV-Störungen. Das Stromsignal wird dabei mit der Abtastzeit TFPGA = 20 ns (50 MHz) des FPGA aktualisiert und eignet sich gut für die Stromregelung unabhängig von der genutzten Schaltfrequenz und der Modulationsstrategie. Durch die stromglättende Wirkung der Induktivität kann es keine sprungförmige Stromänderung geben.

In Bild 7 ist der typische dreieckförmige Stromverlauf aufgetragen. Das Signal des Beobachters verläuft kontinuierlich ohne filterungsbedingte Verzögerung.

- Beobachtergestützte Strommessung mit Sigma-Delta-Modulatoren

- FPGA basierte Strommessung mit getrennter Signalrückführung

- Stromregelung mit getrennter Rückführung

- Literatur und Autoren