Leistungsfaktorkorrektur

Höherer Leistungsfaktor, höherer Wirkungsgrad

Fortsetzung des Artikels von Teil 1

PWM mit variabler Frequenz

Die digitalen PFC-Controller CS1500/1600 arbeiten im lückenden Betrieb (DCM, Discontinuous Conduction Mode). Im Bereich der Amplitudenspitzen ist auch ein Betrieb an der Lückgrenze möglich (Quasi-CRM, Critical Conduction Mode). Abhängig von der Last und dem aktuellen Wert der gleichgerichteten Netzspannung steuert der EXL-Prozessor die Schaltfrequenz und das Tastverhältnis.

Der Leistungs-MOSFET für den PFC-Aufwärtswandler wird von einem Pulsbreitenmodulator mit Gate-Treiberstufe angesteuert. Das Tastverhätnis ist auf maximal 66 % begrenzt, die Schaltfrequenz kann zwischen 22 kHz und 66 kHz gesteuert werden. Die maximale Schaltfrequenz von 66 kHz wird nur im Betrieb mit einer Netzeingangsspannung < 150 V(AC) und hoher Belastung genutzt. Für Eingangsspannungen > 150 V(AC) wird die Schaltfrequenz bei hoher Belastung auf 46 kHz reduziert. Im Teillastbetrieb mit einer Belastung < 40 % der Nennlast liegt die maximale Schaltfrequenz bei 56 kHz (UE < 150 V(AC)) bzw. bei 40 kHz (UE > 150 V(AC)).

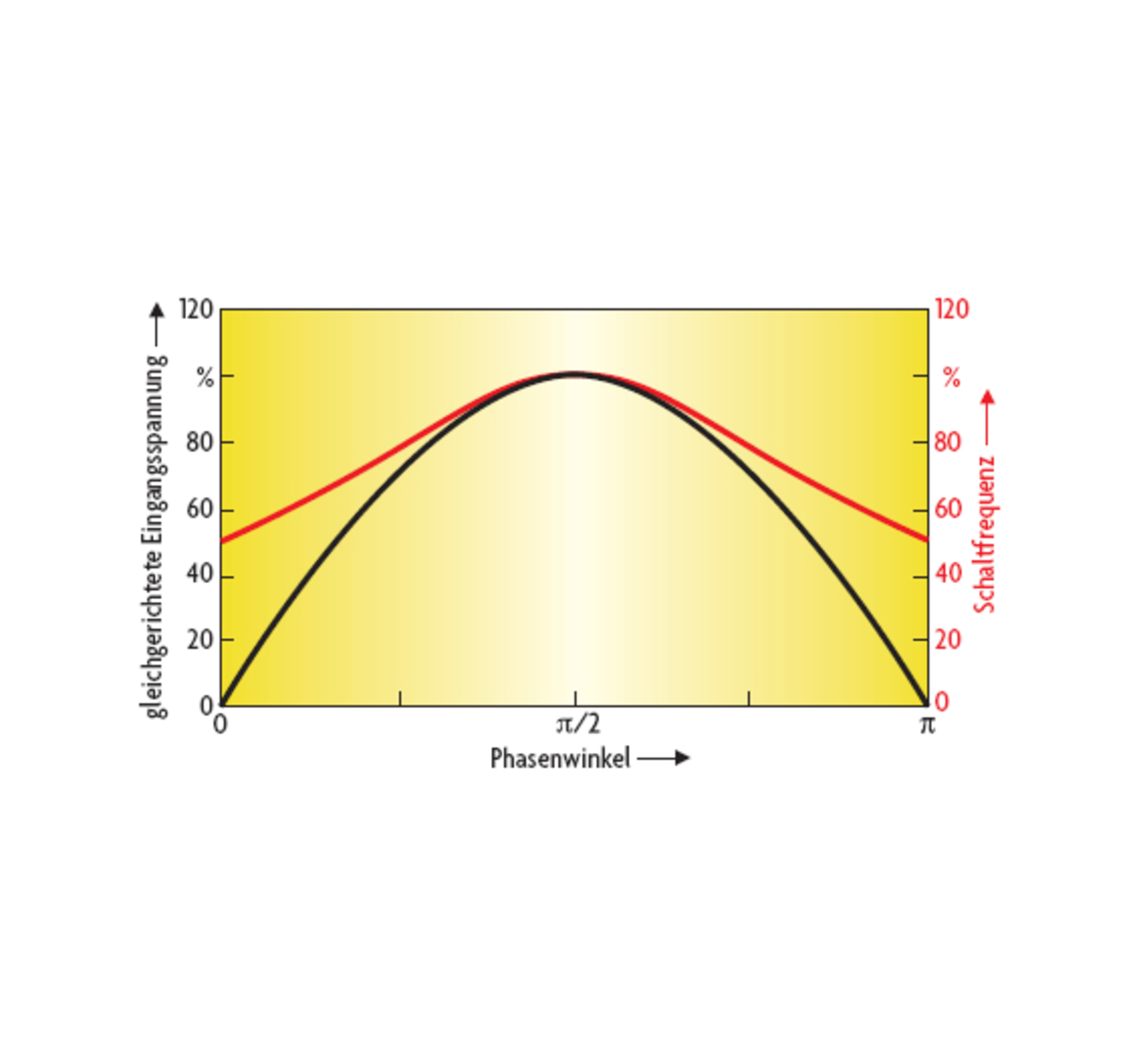

Ausgehend von dieser maximalen Schaltfrequenz steuert der EXL-Prozessor die Schaltfrequenz des Leistungs- MOSFET abhängig von der gleichgerichteten Netzeingangsspannung (Bild 3) und errechnet das Tastverhältnis für jede Periode so, dass bei jeder Lastbedingung der maximale Leistungsfaktor erreicht wird. Im Bereich des Spannungsnulldurchgangs senkt der EXL-Prozessor die Schaltfrequenz des MOSFET auf 50 % des Maximalwertes. Damit verhalten sich die digitalen PFC-Controller CS1500/ 1600 entgegengesetzt zu den traditionellen, analogen PFC-Controllern, die an der Lückgrenze (CRM) betrieben werden: Deren Schaltfrequenz ist im Bereich des Nulldurchgangs am höchsten. Die umgekehrte Frequenzsteuerung der CS1500/1600 senkt zum einen die Schaltverluste im Teillastbereich und zum anderen die Stärke der leitungsgebundenen Störsignale (EMI, Elektromagnetische Interferenz) um bis zu 14 dB.

Drei Betriebsweisen, sechs Schutzfunktionen

Solange die Zwischenkreisspannung am Ausgang der PFC-Stufe unter dem Nennwert liegt, läuft im CS1500/1600 die Anlaufprozedur ab. Diese Anlaufphase beginnt üblicherweise mit dem Einschaltvorgang und wird erst verlassen, wenn die Gleichspannung am Ausgang 100 % erreicht. Sinkt die Zwischenkreisspannung unter den Schwellwert von 90 %, so startet der PFC-Controller erneut mit einer Anlaufphase, bis die Spannung am Ausgang wieder auf 100 % gestiegen ist. Dies kann auch durch einen Lastwechsel verursacht werden.

Übersteigt die am Ausgang geforderte Leistung den Maximalwert, so sinkt die Ausgangsspannung. Sobald der 90-%-Schwellwert unterschritten wird, beginnt der CS1500/1600 mit einer Anlaufphase, bis die Nennspannung am Ausgang wieder erreicht ist. Sinkt die Ausgangsspannung erneut unter die 90-%-Schwelle, so wechselt der PFCController ständig zwischen Normalbetrieb und Anlaufphase hin und her, bis der Prozessor dies als Überlast erkennt. Infolgedessen schaltet der Prozessor den Gate-Treiber ab und schaltet den kompletten PFC-Controller in den Energiesparbetrieb. Nach 3 s initiiert der Prozessor eine erneute Anlaufphase und prüft so, ob die Überlastbedingung am Ausgang weiterhin besteht. Schafft es der PFC-Controller in der Anlaufphase nicht, die Ausgangsspannung innerhalb einer vorgegebenen Zeit auf den Nennwert zu bringen, so aktiviert der Prozessor gleich den Überlastschutz und schaltet den Gate-Treiber ab.

Wird der Ausgang (Zwischenkreis) der PFC-Stufe mit weniger als 5 % der Nennleistung belastet, so wechselt der PFC-Controller in den Burst-Modus. In dieser Betriebsart wird die PFCStufe abgeschaltet, und zwar für die Dauer einer halben Netzperiode.

Neben dem Überlastschutz sind die Bausteine CS1500/1600 mit Schutzfunktionen gegen Überlast und Überspannung und gegen Kurzschluss sowie den Betrieb mit offener Regelschleife und einer Strombegrenzung ausgestattet. Bei Unterspannung – detektiert durch Unterschreiten eines Schwellwertes (65 V) – schaltet der PFC-Controller in den Bereitschaftsbetrieb, misst aber weiterhin die Eingangsspannung. Der PFC-Controller schaltet allerdings nicht sofort in diesen Zustand, sondern erst nach 56 ms, nachdem der Prozessor eine zu kleine Eingangsspannung eindeutig erkannt hat.

Hierfür lässt der Prozessor den im Normalbetrieb auf 128 V begrenzten Messwert der Eingangsspannung mit einer Rate von 5 V/8 ms sinken. Unterschreitet die Messspannung schließlich den unteren Schwellwert (65 V), weil die Netzspannung immer noch zu niedrig ist, dann startet der 56-ms- Timer. Steigt die Eingangsspannung nicht innerhalb der 56 ms an, dann schaltet der Prozessor in den Bereitschaftsbetrieb. Erkennt der Prozessor, dass die Eingangsspannung wieder steigt – die gemessene Eingangsspannung überschreitet den oberen Schwellwert (80 V) –, startet er erneut den 56-ms- Timer. Erst wenn nach Ablauf des Timers die Eingangsspannung immer noch über dem Mindestwert liegt, verlässt der PFC-Controller den Bereitschaftsbetrieb, indem er eine Anlaufphase ausführt, um dann in den Normalbetrieb zu wechseln.

Dauert die Unterspannungsbedingung über eine längere Zeit an, so versucht der Prozessor alle 3 s, mit einer Anlaufphase in den Normalbetrieb zurückzukehren – analog dem Überlastschutz. Der Überspannungsschutz dagegen sperrt den Gate-Treiber sofort, wenn die Eingangsspannung die 105-%-Schwelle überschreitet.

Unterschreitet der gemessene Wert der Zwischenkreisspannung den Messwert der Eingangsspannung, wird dies als Kurzschluss am Ausgang oder Unterbrechung des Messwiderstandes (RmAC, Bild 1) interpretiert. Der Prozessor sperrt in diesem Fall den Gate- Treiber auch mit einer Zeitverzögerung, die durch die Abtastrate des Analog/Digital-Umsetzers (ADU) verursacht wird. Die Eingangsspannung des ADU kann maximal mit 2 V/μs sinken. Der CS1500 reagiert aber spätestens nach 150 μs auf einen Kurzschluss am Ausgang.

Die Überstromschutzfunktion ist als Algorithmus implementiert und verhindert, dass die Induktivität in die Sättigung gelangt. Hierfür muss der Schaltungsentwickler die Speicherdrossel lediglich etwas überdimensionieren – also für Nennlast, bei minimaler Eingangsspannung und maximaler Schaltfrequenz so dimensionieren, dass im Normalbetrieb noch eine ausreichende Reserve bis zur Sättigung bleibt.

Der Autor:

| Will Draper |

|---|

| ist verantwortlich für die Produktentwicklung und die Vermarktung von digitalen AC/DCLicht- Steuer-ICs mit einem speziellen Schwerpunkt auf die nächste Generation von LEDLeuchten. Vor seinem Eintritt bei Cirrus Logic war er als technischer Vertriebsleiter bei Semi- South Laboratories tätig, einem Hersteller von SiC-Halbleitern. Er studierte Elektrotechnik (B.S.) an der staatlichen Universität von Mississippi. |

will.draper@cirrus.com

- Höherer Leistungsfaktor, höherer Wirkungsgrad

- PWM mit variabler Frequenz