Einführung in den PMBus

Power-Manager in Aktion

Fortsetzung des Artikels von Teil 1

Adressplanung und -einstellung

Die Adressplanung ist einfach. Man erstellt eine Tabelle in der alle Bausteine und Adressen aufgelistet sind, wobei man die folgenden Adressarten nutzt:

- Normale Adressen,

- Globale Adressen,

- Spannungsversorgungsadressen,

- Kanaladressen,

- Spezialadressen (ARA) und

- Nicht-PSM-Adressen.

Dabei sollten sich – ausgenommen globale Adressen – keine Adressen überlappen, und alle Adressen sollten unverwechselbar sein, wenn sie eine gemeinsame Basisadresse haben.

Obwohl es für die meisten Bauteile sehr ähnlich ist, wie man die Adressen anlegt, gibt es feine Unterschiede zwischen der DC/DC-Controllerfamilie LTC388x und der Power-Manager-Familie LTC297x und auch wie die Komponenten reagieren. Es gibt auch noch geringe Unterschiede innerhalb der Familien. Die Funktionsprinzipien sind jedoch gleich und alle Bausteine können zunächst allgemein betrachtet werden, bevor man spezifische Unterschiede betrachtet.

Für alle PSM-Bausteine am Bus ist die aktuelle Adresse eine Kombination eines Registerwertes, genannt BASE-ADDRESS, und einer optionalen Modifikation über Widerstände, die an die Pins des Baustein zur Adressauswahl angelegt werden, genannt ASEL-Pins.

Es gibt verschiedene Gründe für den Einsatz von ASEL-Pins anstatt von vorprogrammierten Bausteinen. Erstens: Das Vorprogrammieren kostet Zeit und Geld und es ist nicht unbedingt wünschenswert, die Bausteine generell vorzuprogrammieren. Viele Bausteine haben auch Konfigurations-Pins, um die Ausgangsspannung einzustellen, und das ist eventuell auch alles, was man machen muss. Zweitens: Wenn ein Baustein einen CRC-NVM-Fehler aufweist, würde er seine Adresse verlieren und es gäbe für den Bus-Master keine Möglichkeit, mit jedem Teilnehmer für sich zu kommunizieren, um diese zu reprogrammieren.

Die Lösung sind deshalb ASEL-Pins und eine Basisadresse. Ein Bus-Master kann mit allen Teilnehmern über die globale Adresse 0x5B kommunizieren. In einem solchen Fall kann er auch die BASE-ADDRESS einstellen, weil alle PSM-Bausteine das Register MFR_I2C_BASE_ADDRESS3 unterstützen. Der Bus-Master kann dann alle Teilnehmer zwingen, ihre Adress-Pins zu lesen, und alle Bausteine werden eine eindeutige Adresse haben, die der Bus-Master kennt. Kann der Bus-Master einmal mit jedem einzelnen Busteilnehmer unabhängig kommunizieren, so kann das EEPROM erneut programmiert werden.

Dies bedeutet Folgendes und ist das Wichtigste, was man aus diesem Artikel mitnehmen sollte: Alle Busteilnehmer müssen eine unverwechselbare Adresse aufweisen, wenn sie alle die gemeinsame BASE-ADDRESS nutzen, auch müssen ihre ASEL-Pins ausgelesen und angelegt werden. Folgt man dieser Regel, lässt sich ein System mit LTpowerPlay, mit Linduino-Referenzcode oder kundenspezifischer Firmware reparieren, wenn der NVM beschädigt wird. Deshalb müssen PSM-Bausteine von Analog Devices niemals ausgelötet werden, um ein System zu reparieren.

Im Folgenden werden die Details der Produktfamilien beschrieben, um ein vollständiges Verständnis über das Setup der Adressen zu erhalten, und wie sie mit den Parametern der Adressenabbildung arbeiten.

Die LTC388x-Familie

Die PSM-Bausteinadressen der LTC38x-Familie werden von einer Kombination aus dem Wert der BASE-ADDRESS und dem Wert, der von den ASEL-Pins kommt, eingestellt. Einige LTC388x-Bausteine haben einen einzigen ASEL-Pin und einige zwei, sodass man sie unterschiedlich behandeln muss.

- Einfache ASEL-Pins

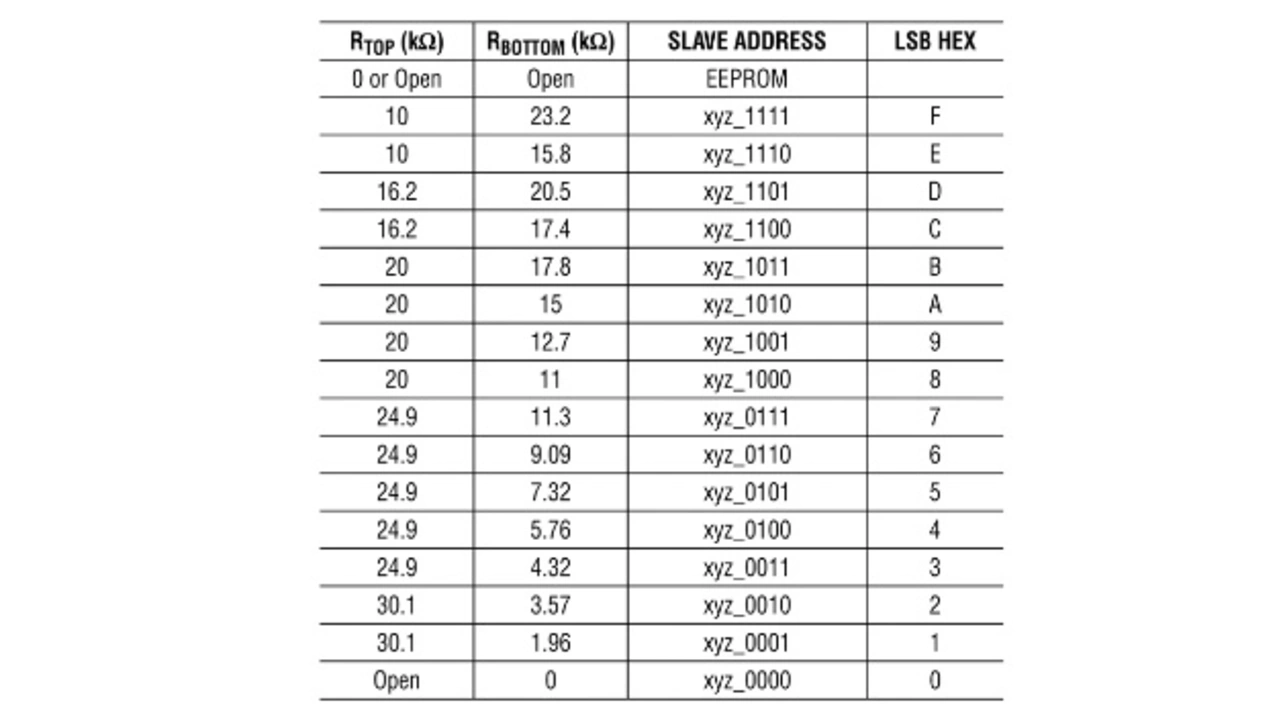

Tabelle 2 zeigt die ASEL-Pins aus dem LTC3880-Datenblatt. Dieses IC hat nur einen ASEL-Pin. Die drei »xyz«-Bits in der Spalte der Slave-Adresse sind die BASE-ADDRESS, die im Register MFR_I2C_BASE_ADDRESS (0xE6) gespeichert sind. Der ASEL-Pin programmiert die vier LSBs aus der Tabelle, außer wenn es keine ASEL-Pins am Register gibt. In diesem Fall werden alle sieben Bits der BASE-ADDRESS benutzt.

Man benutzt »open« an den ASEL-Pins nur dann, wenn es nur einen einzigen Teilnehmer am Bus gibt. Die ASEL-Pins müssen in jeder Applikation mit mehreren Bausteinen verwendet werden, um die Adresse zu programmieren. Nutzt man den einzigen ASEL-Pin, um das Bauteil zu programmieren, beschränkt sich die Anzahl an Adressen am Bus auf 16.

Mithilfe eines Bus-MUX lässt sich die Anzahl der Adressen erhöhen. Dies wird weiter unten noch beschrieben.

- Zweifache ASEL-Pins

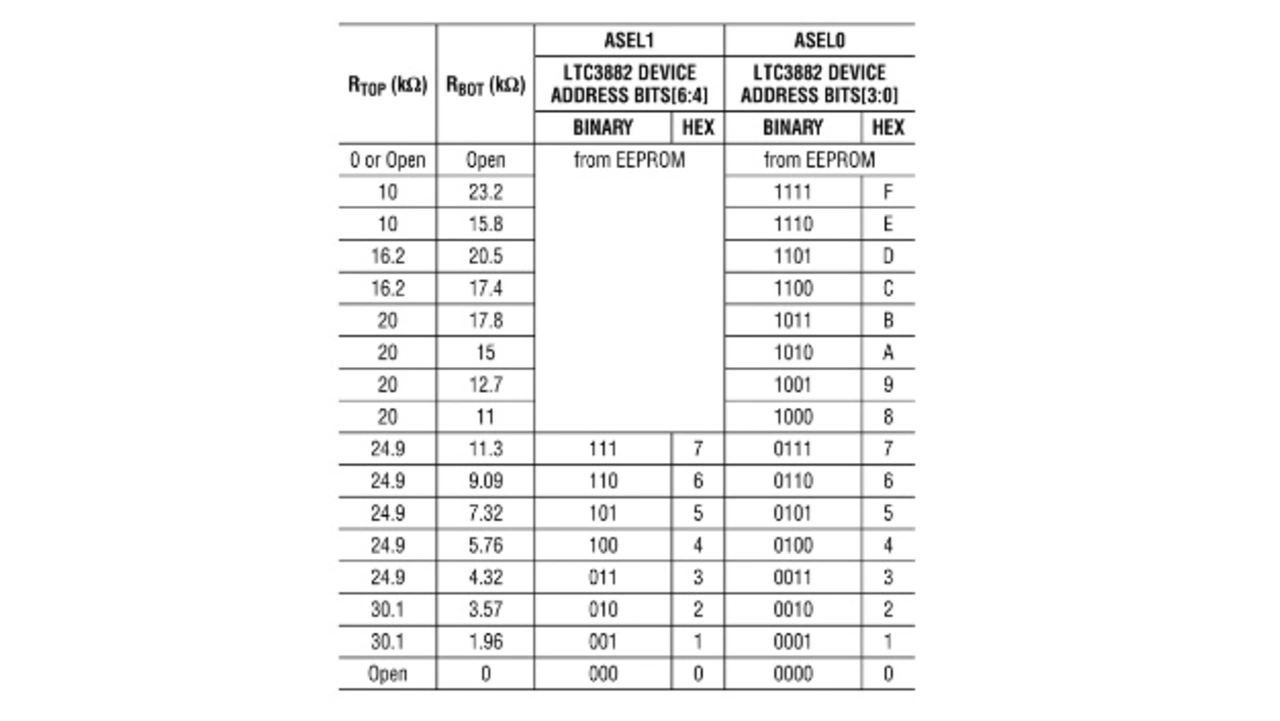

Zweifache ASEL-Pins erweitern die Anzahl der Adressen von 16 auf 127. Tabelle 3 zeigt die ASEL-Pins aus dem Datenblatt des LTC3882. Wenn ein ASEL-Pin auf »vom EEPROM« eingestellt ist, dann arbeitet ASEL0 wie ein einziges ASEL-Verhalten des LTC3880. Mit dem ASEL-Pin 1 verbundene Widerstände steuern die drei MSBs der Bausteinadresse. Dies erweitert die Anzahl der unverwechselbaren Adressen auf 127 Werte.

Ein System, das aus Bausteinen mit einfachem und zweifachem ASEL-Pin besteht, kann bis zu 16 Bausteintypen mit Einfach-ASEL-Pin und so vielen Bausteinen mit zweifachen ASEL-Pins bestehen, wie Adressen verfügbar sind.

Die LTC297x-Familie

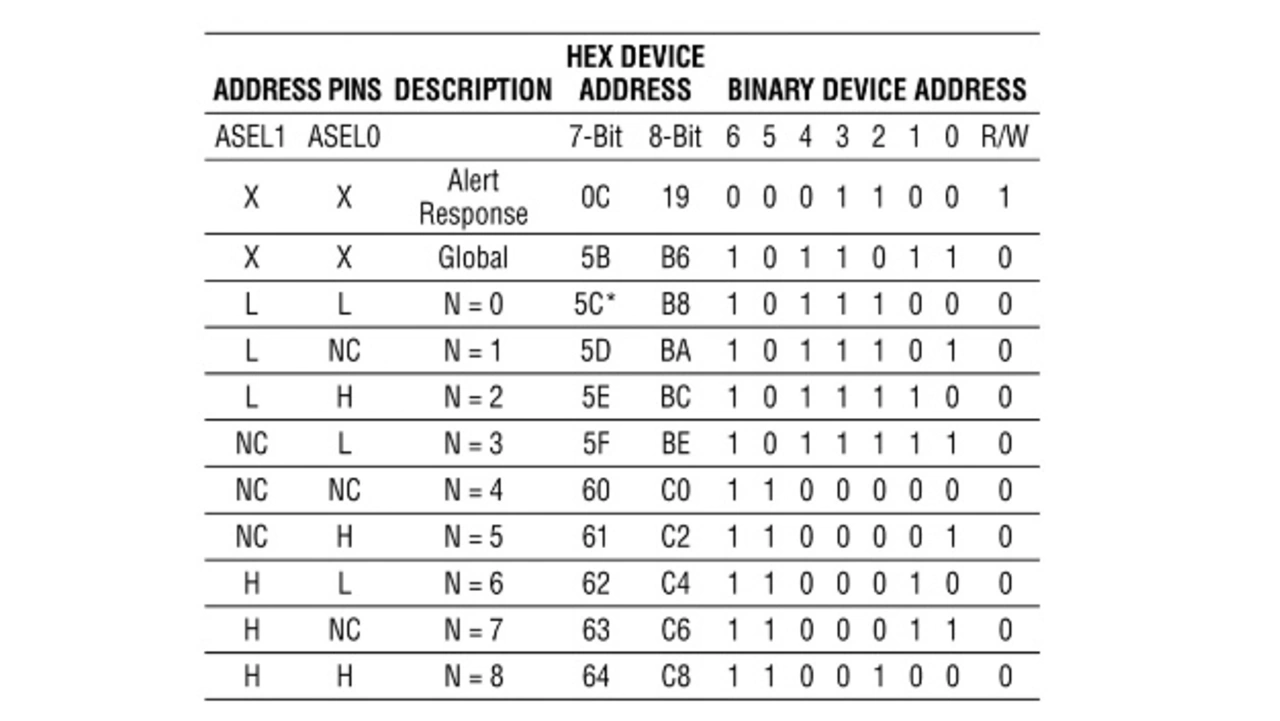

Der Hauptunterschied der LTC297x-Familie ist, dass Auswahlwerte der ASEL-Pins zur BASE-ADDRESS addiert werden. Addiert heißt hinzufügen und nicht Bits ersetzen oder maskieren. Tabelle 4 zeigt die Look-up-Tabelle des LTC2975. Seine ASEL-Pins kennen die drei Zustände High, Low und nicht verbunden. Zwei der Pins wählen neun unterschiedliche Werte, die als »N =« dargestellt werden. In dieser Tabelle ist die BASE-ADDRESS 0x5C, wenn »N = 0« die Adresse 0x5C ist.

Diese Tabelle hat ebenfalls 8-Bit-Spalten. Dies ist die Adresse, die in der Applikationsschrift verwendet wird, um eine Stelle nach links zu schieben.

- CRC-Fehlanpassung

Sämtliche PSM-Bausteine von Analog Devices besitzen ein EEPROM, das Einstellungen speichert, die die Ausgangsspannung, Supervisor-Begrenzung und den grundlegenden Betrieb bestimmen. Jeder Fehler im Speicher könnte einen Schaden an den Lasten hervorrufen. Diese PSM-Bausteine können die Daten laut Spezifikation mindestens zehn Jahre halten. Unvorhergesehene Systembedingungen während eines EEPROM-Schreibzyklus, wie zu hohe Temperatur oder Spannungseinbruch, können jedoch dazu führen, dass das Schreiben fehlschlägt, und den Inhalt des EEPROMs beschädigt.

Die Aufgabe der zyklischen Redundanzprüfung (Cyclic Redundancy Check, CRC) ist es, zu verifizieren, ob der EEPROM-Inhalt auch korrekt ist. Eine gültige CRC garantiert, dass ein Baustein sicher arbeitet, und eine ungültige CRC sperrt den Betrieb des Bausteins und benachrichtigt den Host über einen PMBus-ALERTB.

- Wie arbeitet die CRC?

Wenn ein PSM-Bauteil zum ersten Mal eingeschaltet wird, überträgt es die Inhalte des EEPROMs in ein RAM, da das RAM der Arbeitsspeicher des Bausteins ist. Wenn dies erfolgt, berechnet das Bauteil eine CRC-Summe der RAM-Inhalte und vergleicht sie dann mit dem gespeicherten CRC im EEPROM. Stimmen die beiden CRCs überein, arbeitet das Bauteil; stimmen sie nicht überein, berichtet das Bauteil einen CRC-Fehler und bleibt im Reset-Zustand.

Alle GPIOB/FAULTB-Pins aller PSM-Bauteile zu verbinden, die Bauteile zu programmieren und diese während eines Fehlers zu sperren, ruft eine CRC in gesamten System hervor. Es gilt zu verhindern, dass an allen Versorgungsschienen im System Spannung anliegt. Dies ist generell das beste Systemdesign, wenn nicht eine Analyse mehrerer Fehler ergeben hat, dass alle Fehlerkombinationen zu einem sicheren Betriebszustand führen.

Wenn alle Versorgungsspannungen ausgeschaltet sind, ist die Analyse wesentlich einfacher, und das System wird deutlich sicherer, weil jeder Fehler dazu führt, dass alle Versorgungsschienen vollständig abschalten.

- CRC des LTC388x und des LTC297x

Zeitigt ein LTC388x-Baustein einen CRC-Fehler, so ändert er seine Adresse auf 0x7C. Gleiches gilt, wenn weitere LTC388x-Bausteine ebenfalls einen CRC-Fehler haben. Diese Bausteine bleiben auf 0x7C, bis ihre NVMs mit gültigen Daten überschrieben werden und sie die Initialisierung durchlaufen, die vom MFR_RESET-Befehl (0XFD) oder vom Power-Cycle kommt.

Zeitigt aber ein LTC297x-Baustein einen CRC-Fehler, kann sein Wert eine von zwei Adressen annehmen, im einfachsten Fall die Standard-Basisadresse 0x5C. Diese tritt ein, wenn das gesamte EEPROM einen CRC-Fehler hat.

Weil der LTC297x das EEPROM jedoch in Blöcken verarbeitet und Blöcke nahe am unteren Ende einen gültigen CRC-Wert haben können und Blöcke nahe am oberen Ende nicht, ist es auch möglich, eine Adresse zu haben, die in der Basisadresse gespeichert ist. Die ist verschieden zum LTC388x, weil dieser eine vollständige CRC-Verifikation des gesamten EEPROMs durchführt, bevor er die Adresse bestimmt, während der LTC3297x die Adresse schrittweise bestimmt.

- CRC-Fehler abgleichen

Generell werden CRC-Fehler niemals manuell abgeglichen. LTpowerPlay kann CRC-Fehler mit seinem Programmierwerkzeug einfach abgleichen und In-Flight-Update gleicht sie ebenfalls aus. Es ist jedoch hilfreich zu verstehen, wie sie CRC-Fehler beheben, um die Adressierung besser zu verstehen.

Der erste Schritt, um CRC-Fehler zu beheben, besteht darin, auf alle Bausteine mit CRC-Fehlern zugreifen zu können. Das bedeutet PMBus-Befehle zu senden, um die individuellen Adressen erneut zu speichern. Der Befehl MFR_I2C_BASE_ADDRESS wird zur globalen Adresse 0x5B gesendet. Dann folgt eine Sequenz an Befehlen, um alle Bausteine zu zwingen, ihre ASEL-Pins zu lesen. Im zweiten Schritt werden Daten an die Bausteine gesendet. In der Theorie könnte jeder Befehl benutzt werden, den das Bauteil unterstützt, es ist aber wesentlich effizienter, Massendaten mit dem Befehl MFR_EE_Data zu senden. Sowohl LTpowerPlay als auch In-Flight-Update benutzen diesen Befehl.

Bei einer schlechten Adressplanung, welche die ASEL-Pins nicht nutzt, um alle Bausteine mit einer eindeutigen Adresse zu versehen, wird der gerade beschriebene erste Schritt nicht funktionieren. Stellt man die MFR_I2C_BASE_ADDRESS ein, werden mehrere PSM-Bausteine die gleiche Adresse haben. Außerdem lassen sich mit MFR_EE_DATA nicht mehr einzelne Bausteine reparieren, weil dadurch alle Bausteine mit der gleichen Adresse ebenfalls mit denselben Daten programmiert werden.

- Power-Manager in Aktion

- Adressplanung und -einstellung

- Beispiel einer Bussegmentierung