Power over Ethernet

Echtzeit-Leistungsüberwachung in Netzwerken

Fortsetzung des Artikels von Teil 1

Stromversorgung über das Netzwerk

Ein Energiemanagement auf System-ebene erfordert Echtzeit-Telemetrie sowie die Möglichkeit zur Steuerung aller Regler im System. Da ein Ethernet-Netzwerk ein verteiltes System mit Kabeln der Kategorie CAT5 oder höher ist, ist zur Unterdrückung von Masseschleifen sowie aus Sicherheitsgründen eine galvanische Trennung vorgeschrieben [2].

Energie-Einsparpotenzial in Firmennetzen

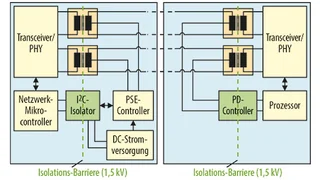

Bild 1 zeigt eine typische Power-over-Ethernet-Implementierung mit einem versorgten Gerät (PD) und einem als Power Sourcing Equipment (PSE) fungierenden Netzwerk-Switch. Die Protokolle für das Energiemanagement auf Systemebene sind in einem Prozessor im Netzwerk-Switch implementiert, der den PSE-Controller über eine isolierte I²C-Schnittstelle steuert. Der PSE-Controller steuert die Leistung, die an jedes einzelne PD geliefert wird, und meldet darüber hinaus Strom- und Spannungswerte über dieselbe I²C-Schnittstelle an den Prozessor zurück, so dass dieser die zur Verwaltung des Energiebedarfs benötigten Informationen zur Verfügung hat.

Eine Herausforderung ist die Datenübertragung über die Isolationsbarriere bei einer Frequenz, die ein optimiertes Energiemanagement im Netz ermöglicht. Zur Echtzeitüberwachung wie auch zur Steuerung mehrerer Ethernet-Ports von einem einzigen Prozessor aus sind Datenübertragungsraten von bis zu 3,4 MHz auf dem I²C-Bus erforderlich. Das bedeutet nicht nur eine schnellere Kommunikation zwischen dem Prozessor und den einzelnen PSEs. Aufgrund der inzwischen auf dem Markt verfügbaren High-End Switches mit bis zu 96 Ports ist der Bedarf an Kommunikationsbandbreite auch noch höher als je zuvor. Ein weiterer Punkt ist, dass sich die PSE-Controller ebenfalls von vier bis hin zu zwölf Kanälen pro IC bewegen, was also die dreifache Kommunikationsbandbreite zwischen dem Prozessor und den einzelnen PSE-Controllern erfordert. Die herkömmlichen Lösungen in Form von Optokopplern haben hohe Laufzeitverzögerungen, was deren Eignung für höhere Kommunikationsgeschwindigkeiten einschränkt [3]. Hochgeschwindigkeits-Digital-Isolatoren machen diese höheren Übertragungsraten hingegen möglich.

Die Isolation von I²C-Bussen

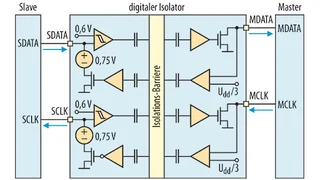

Der I²C-Bus ist eine weit verbreitete Schnittstelle für die bidirektionale Datenübertragung in vielen Anwendungen [4]. Der Bus wird von einem Gerät, dem Master, gesteuert, der mit einem oder mehreren Slave-Geräten kommunizieren kann. Die Takt- (SCLK) und Datenleitungen (SDATA) werden von allen Slaves gemeinsam genutzt. Jede bidirektionale Datenübertragung erfolgt innerhalb eines Taktzyklus (Bild 2).

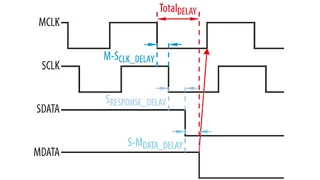

Das Timing ist für eine fehlerfreie Datenübertragung insbesondere bei Hochgeschwindigkeitsanwendungen – von äußerster Wichtigkeit. Um eine fehlerfreie Datenübertragung sicherzustellen, müssen sämtliche Laufzeitverzögerungen über den gesamten Übertragungsweg berücksichtigt werden. Wie in Bild 3 zu sehen, wird die fallende Flanke von MCLK über die Isolationsbarriere geleitet, bevor diese den SCLK-Eingang mit der Verzögerungszeit M-SCLK_DELAY erreicht. Die Antwortzeit des PSE im Anschluss an den Empfang der fallenden Flanke von SCLK ist SRESPONSE_DELAY. Wenn das PSE mit einer fallenden Flanke am SDATA-Ausgang antwortet, wird diese an den Prozessor zurückgeführt und erreicht den MDATA-Eingang mit der Verzögerungszeit S-MDATA_DELAY. Die Addition dieser Verzögerungszeiten ergibt:

TotalDELAY = M-SCLK_DELAY + SRESPONSE_DELAY + S-MDATA_DELAY

Für eine korrekte Datenübertragung muss die Gesamtverzögerungszeit TotalDELAY geringer als die Zeit sein, in der das Signal MCLK bei einer Betriebsfrequenz von 3,4 MHz bzw. einer Taktrate von 150 ns mit einem Tastverhältnis von 50 % low ist.

In Anbetracht der zuvor genannten Herausforderungen lässt sich die Laufzeitverzögerung über die Isolationsgrenze äußerst genau mit Hilfe von Hochgeschwindigkeits-Digitalisolatoren handhaben. Beispielsweise ist die Laufzeitverzögerung über einen digitalen Isolator im Vergleich zu Optokopplern wesentlich geringer.

Die Laufzeitverzögerung über einen Optokoppler ist typischerweise größer als 100 ns, während diese bei einem Hochgeschwindigkeits-Digital-Isolator typischerweise 40 ns beträgt [5]. Bild 4 zeigt ein Oszillogramm der Kommunikation vom Prozessor zum PSE über den digitalen Isolator.

- Echtzeit-Leistungsüberwachung in Netzwerken

- Stromversorgung über das Netzwerk

- Optokoppler vs. digitale Isolatoren