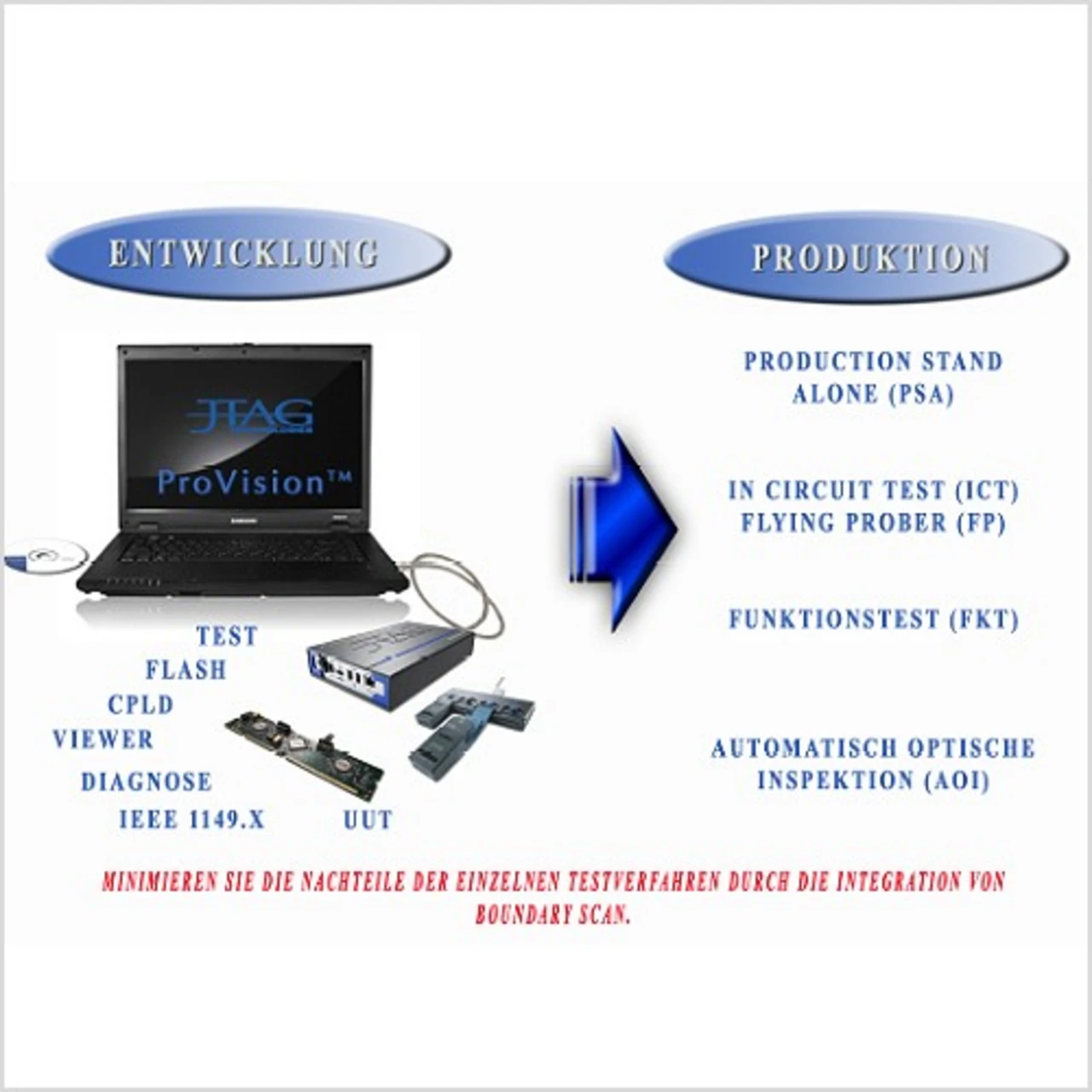

Boundary-Scan-Test ergänzt die »traditionellen« Prüf- und Inspektionsverfahren

Welche Tests braucht die Baugruppe wirklich?

Fortsetzung des Artikels von Teil 1

ICT, FKT und AOI profitieren vom Boundary-Scan-Test

Vor allem beim weit verbreiteten In-Circuit-Test (ICT) kommt es nach Sliwas Überzeugung durch den Einsatz hochohmiger BGAs und der immer schwierigeren Nadelplatzierung durch die Erhöhung der Leiterzugdichte zu einer Verringerung der Testabdeckung von 25 bis 50 Prozent. Ursache sei der fehlende Zugriff auf die benötigten Knotenpunkte. »Selbst der Einsatz teurer Fine-Pitch-Adaptionen bringt oft nicht den gewünschten Erfolg, sondern treibt den Adapterpreis schnell in Preisregionen von 10.000 bis 15.000 Euro«, so der Experte. »Bei einer solchen Investition kann man nur hoffen, dass kein Re-Design mehr ansteht, das eine neue Adaption zur Folge hat.« Zur Kontaktierung einer Boundary-Scan-Kette müssen lediglich die vier Testbussignale im Layout berücksichtigt und nach außen geführt werden. Ändert sich das Design, weil einige Bauteile verschoben oder ein Stecker anders platziert werden muss, spielt dies für Boundary Scan keine Rolle. Die Tests basieren auf der Netzliste, also auf den Informationen, wie die einzelnen Pins der Bausteine miteinander verbunden sind. Wo sich diese auf der Baugruppe befinden, ist irrelevant.

Jobangebote+ passend zum Thema

Dank des parallelen Zugriffs des ICTs und der schnellen Abarbeitung der Testmuster lässt sich der analoge Bereich der Baugruppe sehr effizient prüfen. Im digitalen Bereich hingegen liegen die Vorteile bei Boundary Scan, da aufwändige Funktionsbeschreibungen der komplexen Baugruppen entfallen und der Zugriff ohne weitere Testpunkte jederzeit möglich ist. JTAG Technologies bietet verschiedene »Symphonie «-Pakete zur Integration in alle namhaften ICT-Systeme an.

Eine Weiterentwicklung des ICT ist der Flying-Probe-Test. Hier wird auf die Adaption verzichtet, was sich u.a. im Preis bemerkbar macht. Bewegliche Nadeln kontaktieren die entsprechenden Testpunkte. Da die Prüfvektoren nicht wie beim ICT parallel sondern sequentiell abgearbeitet werden, ist die Dauer des Tests von der Anzahl der Kontaktierungen und der Verfahrwege abhängig. »Durch den Einsatz von Boundary Scan verkürzt sich die Testzeit um bis zu 50 Prozent«, ist Sliwa überzeugt. »Die Nadeln des Flying Probers stehen während des Boundary-Scan-Tests als virtuelle Boundary-Scan-Zelle zur Verfügung und erhöhen somit nochmals die Gesamtabdeckung.«

Ein anderer Ansatzpunkt ist der Funktionstest (FKT), hier werden die funktionellen Eigenschaften einer Flachbaugruppe oder eines Clusters geprüft. Zur Programmerstellung stehen keine automatischen Programmgeneratoren zur Verfügung, sondern es wird eine detaillierte Aufstellung der Funktion der Baugruppe oder der einzelnen Cluster vom Entwickler der Baugruppe benötigt. »Leider ist bei diesem Verfahren eine Fehlerursache gar nicht oder nur mit großem Aufwand zu finden, da diese nicht bzw. nur schwerlich auf Pinebene herunter gebrochen werden kann«, führt Sliwa aus. »Somit kann nur qualifiziertes Personal die Fehler erkennen und beheben. Greift der Entwickler jedoch bereits in der Designphase auf Boundary-Scan- Bausteine zurück, besteht die Möglichkeit, einen Großteil der Baugruppe durch ein automatisches Testverfahren mit einer Fehleraussage auf Pinebene zu ergänzen, um die restlichen Cluster mit einem funktionalen Test zu prüfen. Somit verringert sich der Engineering- Aufwand in der Programmerstellung und Fehleraussage/ Reparatur drastisch.«

Ein weit verbreitetes Testverfahren ist die automatische optische Inspektion (AOI). Auch hier bietet sich die Kombination aus optischem und elektrischem Test zur Erhöhung der Prüfabdeckung an: Das AOI-System prüft die Lage der Bauteile sowie die sichtbaren Lötstellen, nicht sichtbare Lötstellen deckt Boundary Scan ab. Um die relativ hohen Taktzeiten beim AOI zu nutzen, besteht die Möglichkeit der Programmierung von FPGAs, CPLDs oder auch von Mikrocontrollern mit Embedded Flash während der AOI-Prüfung. »Der Qualitätsanspruch, und damit auch die geforderte Prüftiefe an elektrischen Baugruppen, wird weiterhin steigen«, resümiert Sliwa. »Kombiniert man traditionelle Prüfverfahren mit dem Boundary- Scan-Test, erhöht sich nicht nur die Prüfabdeckung, sondern es entsteht auch die Möglichkeit der Onboard-Programmierung und der Visualisierung der Fehler bis auf Pinebene. Und nicht zuletzt sichert man seine bereits getätigten Investitionen.« (nk)

- Welche Tests braucht die Baugruppe wirklich?

- ICT, FKT und AOI profitieren vom Boundary-Scan-Test