Boundary-Scan- und Funktionstest

Die fehlende Verbindung

Die Vorteile des Standard-Boundary-Scan-Tests gemäß IE 1149.1 sind hinreichend bekannt, wobei das Verfahren hauptsächlich einen strukturellen Test, einschließlich der Verbindungen, Speicherblöcke und Logik-Cluster, unterstützt. Weniger bekannt ist dagegen, welche Rolle der Boundary-Scan-Test beim Funktionstest spielen kann.

Der Funktionstest (FT) dient in der Regel dem Test der fertigen Produktfirmware, wobei allerdings die Entwicklung und die Durchführung von FTs zu gewissen Engpässen während der Produkteinführung führen können. Zudem können von externen Anbietern zugekaufte FT-Cores mit hohen IP-Lizenzierungskosten verbunden sein.

Durch den geschickten Einsatz vorhandener Ressourcen lässt sich ein JTAG-FPGA-Zugang auf interne BIST-Funktionen (Built-In Self Test) erweitern. Um FT-Engpässe soweit wie möglich zu vermeiden, untersuchte das englische Messtechnik-Unternehmen Renishaw, wie sich mit Hilfe der programmierbaren FPGA-Cores von JTAG ein funktioneller »At Speed«-Test von Peripherieschaltungen implementieren und dann in ein produktionsfreundliches Paket integriert lässt.

Renishaw hatte bereits vor einiger Zeit eine Methode für den Zugang zur nachträglichen Konfiguration der FPGALogik entwickelt. Dabei wurde eine proprietäre Funktion der »Cyclone«-Bausteine von Altera genutzt, die als »VJI-MegaFunction« (Virtual JTAG Interface) bekannt ist.

Diese dient hauptsächlich der schnellen Flash-Programmierung. Die Anpassung dieses VJI-Ansatzes zur Unterstützung von BIST-Funktionen war damit der nächste logische Schritt. Die erste Aufgabe bestand in der Entwicklung von wieder verwendbaren BIST-Cores für A/D- und D/AWandlerschaltungen, auf die über ein FPGA zugegriffen wird.

Jobangebote+ passend zum Thema

Das erste Projekt, in dem dieses Verfahren zum Einsatz kam, war eine Ethernet-Schnittstellenkarte für eine Werkzeugmaschine (Bild 1).

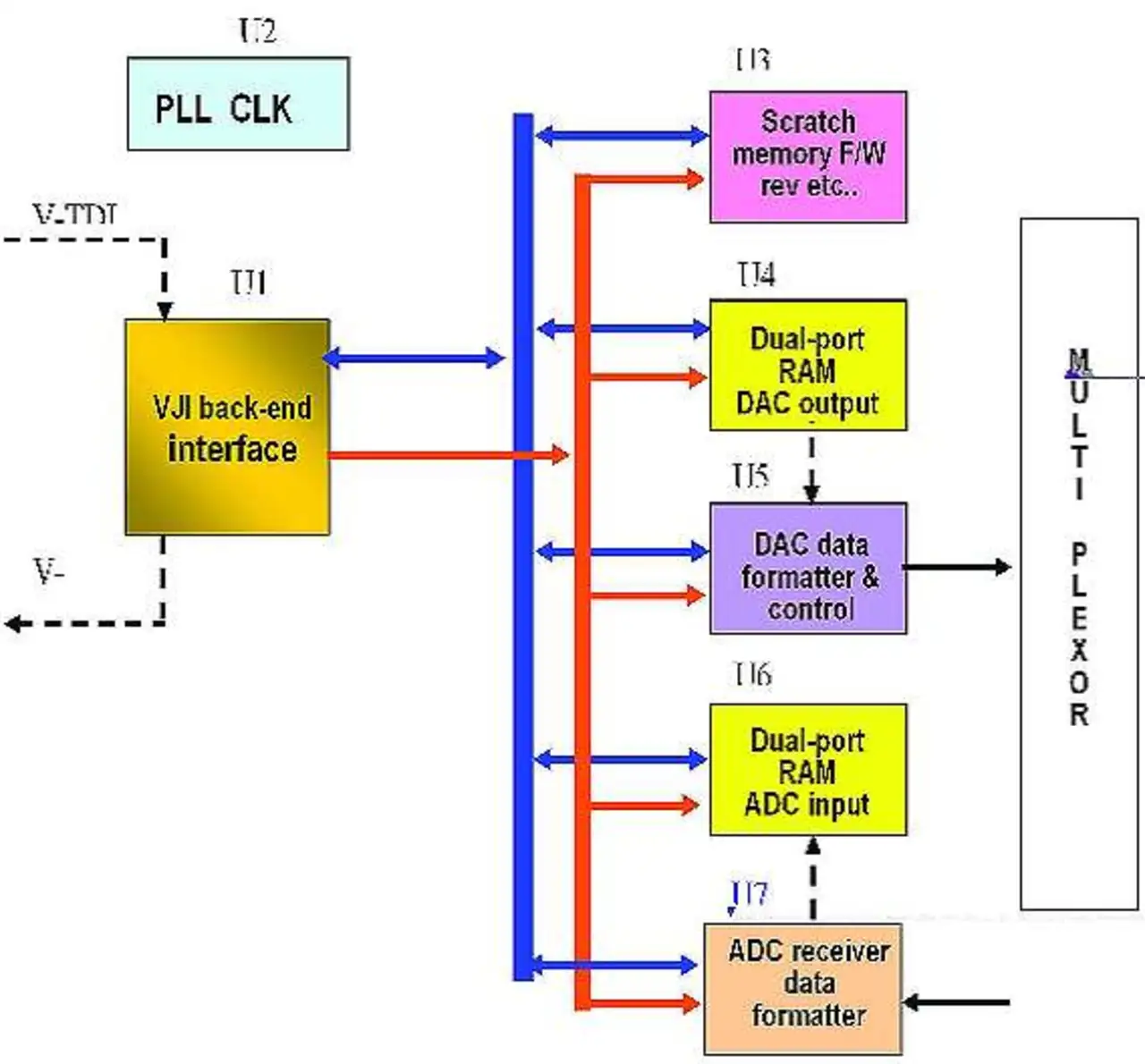

Für diesen ersten BIST-Einsatz wurde das VHDL-Design in sieben Blöcke unterteilt, U1 bis U7.

U1 ist die Schnittstelle zwischen VJI und der BIST-Logik. Sie umfasst ein adressierbares System, das einen 16-Bit-Datenbus und einen entsprechenden Adressbus nutzt.

U2 umfasst die PLL-basierende Taktquelle(n) für die A/D- und D/A-Wandlertests – bei dieser Anwendung liegt die Taktfrequenz bei 33 MHz.

U3 ist ein kleiner Speicherblock, aus dem der Anwender die Versionscodes des BIST-Cores auslesen kann.

U4 ist ein Dual-Port-RAM, das über die interne Busstruktur und die VJI-Schnittstelle geladen werden kann. Der Speicher kann 1 kSample Daten mit einer Auflösung von 12 Bit bei der maximalen A/D-Umwandlungsrate von 33 MHz ausgeben.

U5 formatiert die Ausgangsdaten des Dual-Port-RAM für den parallelen D/A-Wandler. Die VJI-Schnittstelle triggert den Signalausgang und kann Einzel- oder Dauersignale ausgeben.

U6 ist eine Wiederholung des RAM-Blocks, der in diesem Fall die Daten der A/D-Wandlertests aufzeichnet. In diesem Block lassen sich bis zu 1 kSample Daten mit einer Auflösung von 8 Bit speichern.

U7 parallelisiert die seriellen Daten vom A/D-Wandler und schreibt sie in das Dual-Port-RAM. Trigger-Optionen wie Signalpegel und Polarität lassen sich über die VJI-Schnittstelle steuern.

Natürlich gibt es mehr als eine Möglichkeit, um den im FPGA abgelegten Testcode zu laden und auszuführen, aber die meisten dieser Methoden würden den Einsatz zusätzlicher Programmierhardware, Software und möglicherweise weiterer Ressourcen wie FPGA-I/O-Pins erfordern.

Die Verwendung von JTAG als FT-Erweiterung sowohl als Mechanismus zur BIST-Core-Programmierung als auch als Kanal zur Steuerung und Erfassung der Ergebnisse bietet eine Reihe von Vorteilen, wie:

- Kosteneinsparung, da keine bauteilspezifische Zugangshardware notwendig ist und stattdessen die Tester-Hardware vom konventionellen JTAG-Test verwendet werden kann,

- schnelle Programmierung des BIST-Cores (weniger als 3,5 s) durch die Nutzung leistungsfähiger Hardware,

- Routinen, die sich einfach aufrufen und in das bestehende Ausführungsprogramm »Test-Stand« integrieren lassen,

- es sind keine speziellen FPGAPins zur Steuerung der BISTLogik nötig,

- schneller Datenabruf; 150 ms, um 1 kSample Daten vom D/AWandler abzurufen. Diese Rate ist möglich, da die Routinen der HSL-Bibliothek (High Level Scan) in C-Code kompiliert wurden.

Renishaw hat sich zudem mit der Integration in TestStand befasst. Da die HSL-Routinen im DLLFormat vorliegen, mussten diese speziellen Anwendungen für die BIST-Programmierung und die BIST-Aktivierung als »TestStand Step Type« entsprechend den Vorgaben von National Instruments realisiert werden.

Damit lassen sich die BISTFunktionen laden und nahtlos neben bestehenden standardmäßigen JTAG-Anwendungen ausführen. Renishaw kann somit die gewünschten »At Speed«-Funktionstests durch die Verknüpfung des JTAG-FPGAZugangs mit den internen BISTFunktionen ausführen. Außerdem ist es möglich, die entsprechenden Routinen in bestehende Prüfpläne zu integrieren, wodurch keine zusätzliche Schulung der Testentwickler oder des Bedienpersonals erforderlich ist.