Halbleiter-Test

10 Tipps für Boundary-Scan

Fortsetzung des Artikels von Teil 1

10 Tipps für Boundary-Scan (4 - 7)

4. Bypass nichtkonformer Boundary-Scan-Bauteile

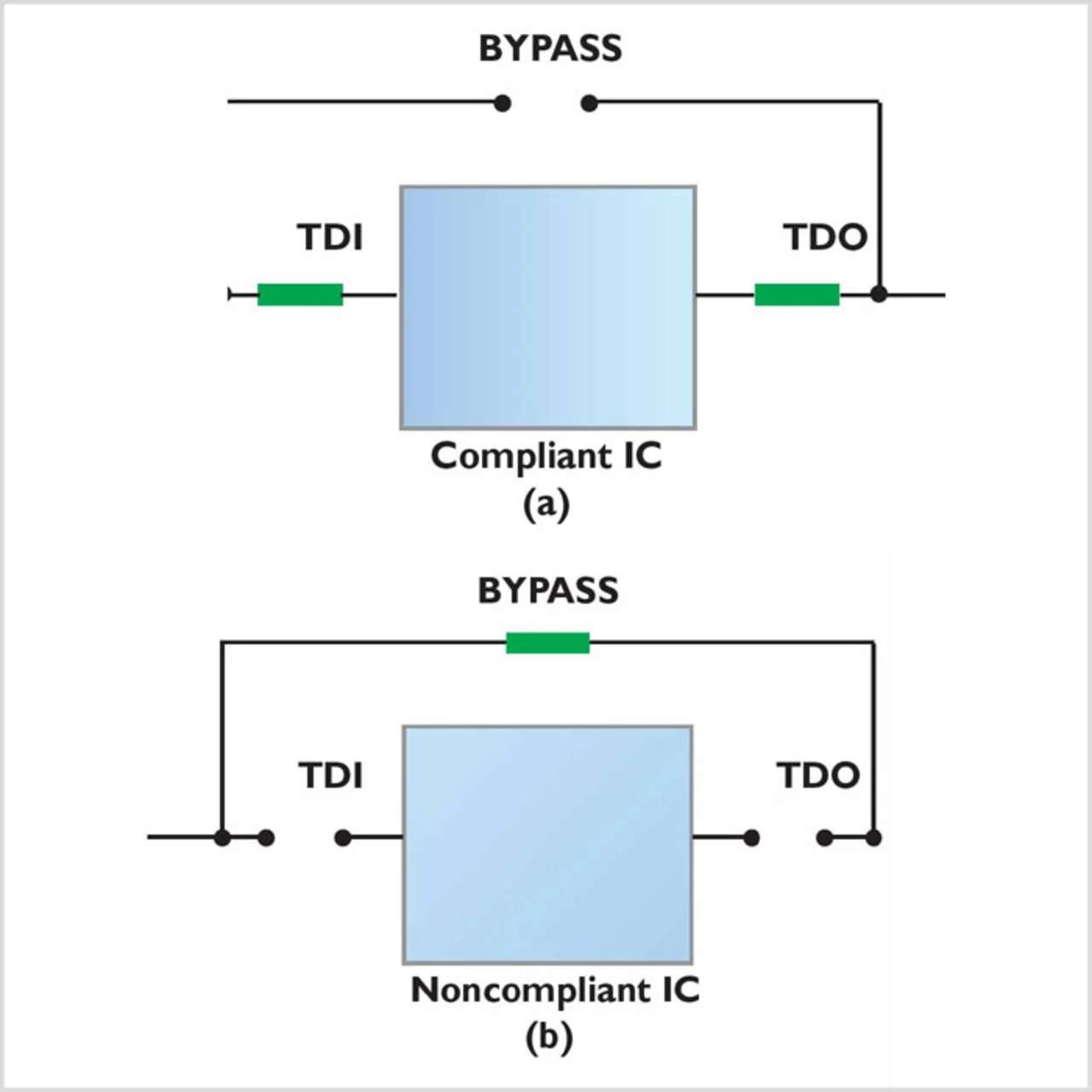

Manchmal ist nicht klar, ob neue Bauteile oder ASICs voll IEEE 1149.1-konform sind, bevor nicht die Implementierung elektrisch verifiziert wurde. In diesem Fall sollten Pads für 0-Ohm-Widerstände oder Kurzschlussbrücken rund um das Bauteil vorgesehen werden (Bild 2a).

Während des Tests sollten die Kurzschlussbrücken vor den TDI-Pins (Test Data In) und nach den TDO-Pins (Test Data Out) entfernt und eine Kurzschlussbrücke in die Bypass-Position gesteckt werden, so dass die Scan-Kette das Bauteil umgeht (Bild 2b).

5. Die Vorteile zusätzlicher I/O-Pins nutzen

In vielen Designs verfügen die verwendeten FPGAs und CPLDs über ungenutzte I/O-Pins, die zur Konfiguration von Logikschaltungen oder zur Aktivierung von Testfunktionen verwendet werden können.

Jobangebote+ passend zum Thema

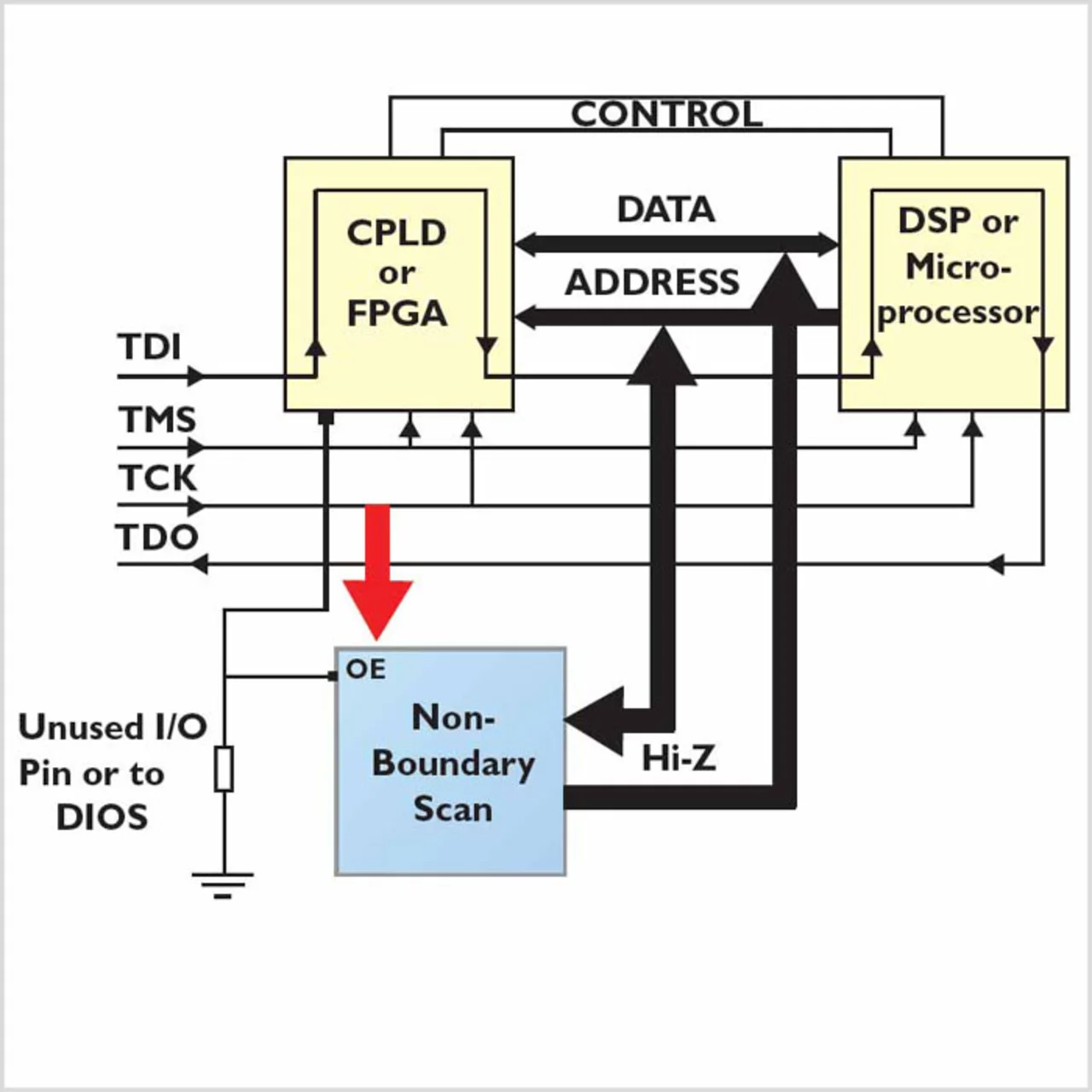

Ein Beispiel hierfür ist eine Schaltung in der ein FPGA und ein Mikroprozessor sowie ein nicht konformer Transceiver einen gemeinsamen Datenbus nutzen (Bild 3). Wenn während des Tests der OE-Eingang (Output Enable) des Transceivers potentialfrei ist (siehe roter Pfeil), können die Bussignale des Transceivers die Signale der Scan-Kette für den Test der FPGA-Prozessor-Verbindungen stören.

Eine derartige Situation kann die Testabdeckung reduzieren. Ein freier FPGA-Ausgang oder ein Ausgang von einem digitalen I/O Scan-Modul (DIOS) kann dann zur gezielten Ansteuerung des OE-Pins des Transceivers verwendet werden und damit diese Ausgänge in einen hochohmigen Status bringen, so dass der Bustest nicht beeinflusst wird. Das Routing dieser zusätzlichen Leiterbahn wirkt sich nicht auf das Design aus. Wenn schließlich das FPGA konfiguriert wird, sollte der Ausgang einfach als ein nicht verbundener Pin definiert werden, so stört dieser nicht die Logikschaltungen des Systems (siehe Tipp 7).

6. Steuerung der Takte bei synchronen Bauteilen

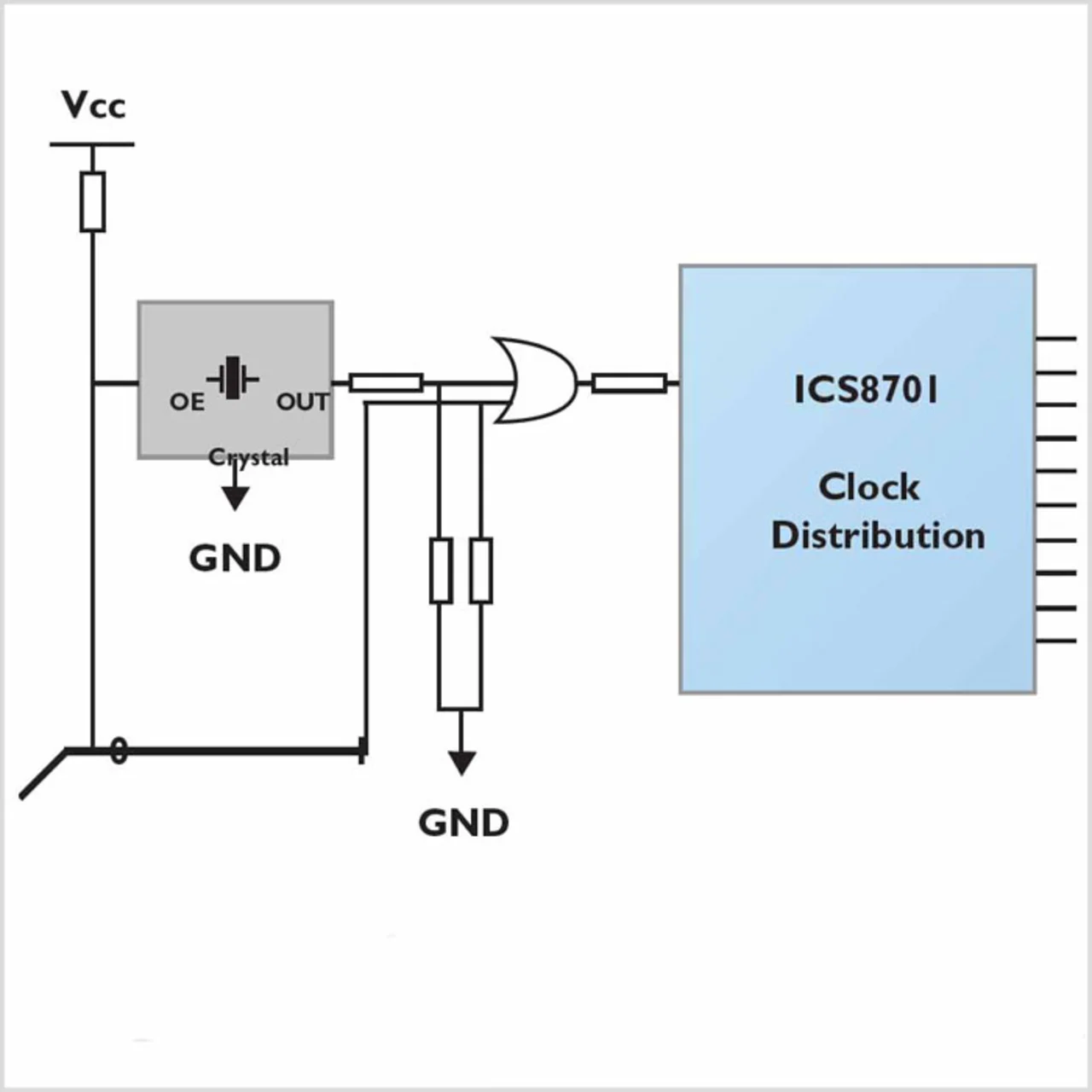

Synchrone Speicher benötigen für Schreib- oder Lesevorgänge ein Taktsignal. Wird während des Design-Prozesses die Testbarkeit nicht berücksichtigt, dann kommt höchstwahrscheinlich ein einfacher Oszillator zum Einsatz, bei dem aber der Boundary-Scan-Test den Takt nicht steuern kann.

Um diese Einschränkung zu vermeiden, sollte ein ungenutzter FPGA-Ausgang verwendet werden, um den Oszillator zu sperren und über ein ODER-Gatter ein Boundary-Scan-Signal anstatt des Oszillator-Signals als Taktsignal für das System aufzuschalten (Bild 4). Damit kann der Boundary-Scan-Test das Taktsignal steuern und synchron auf den Speicher zugreifen.

Wenn dieser Takt ein Taktverteilungs-IC mit einem internen PLL ansteuert, lässt sich ein langsamer Boundary-Scan Takt meist nicht mit dem PLL synchronisieren. Folglich muss die Testschaltung dieses IC umgehen. Der PLL Clock Generator MPC9331 von IDT, zum Beispiel, bietet einen statischen Bypass-Pfad für die integrierte PLL, so dass ein externer Takt synchrone Bauteile steuern kann. Andere Taktverteilungs-ICs verfügen über ähnliche Funktionen.

7. Verwendung von Flash-AutoWrite-Operationen

Konventionelle Anwendungen benötigen einen seriellen Bitstrom, um die ganze Boundary-Scan-Kette um die Einstellungen für die Flash-Speicheradresse, Daten und Steuerleitungen durchzuschieben. In einem zweiten Schiebevorgang durch die ganze Kette wird das WE-Eingangssignal (Write Enable) des Speicher anschließend auf logisch 0 und in einen dritten Schiebevorgang dann wieder zurück auf logisch 0 gesetzt. Somit benötigt ein einziger Schreibvorgang drei Schiebevorgänge durch die gesamte Kette.

Besser ist ein externer Zugang zum WE-Signal des Flash-Speichers, da sich damit die Boundary-Scan-Hardware direkt ansteuern lässt, wenn die Hardware eine AutoWrite-Impulsgenerierung unterstützt. Dann wird nur ein einziger Schiebevorgang durch die Boundary-Scan-Kette benötigt, um die Adresse, Daten und Steuerleitungen einzustellen. Der Boundary-Scan-Controller kann somit das WE-Signal direkt ansteuern, was sehr viel Zeit spart.

Da die Programmierung von Flash-Speichern oftmals zu den zeitaufwändigsten Boundary-Scan-Operationen gehört, sollten hier möglichst kurze Programmierzeiten sichergestellt werden. Beim Boundary-Scan-Verfahren bestimmen zwei entscheidende Faktoren die Effizienz der Flash-Speicher-Programmierung: die Länge der Ketten und die Test-Taktfrequenz (TCK).

Je mehr Bauteile in einer Scan-Kette vorhanden sind, desto länger dauert es, die Bits durch die Kette zu schieben. Um Flash-Speicher zu programmieren, sollten daher alle Boundary-Scan-Bauteile, die nicht für die Programmierung benötigt werden, per BYPASS umgangen oder falls möglich in einen HIGHZ-Modus gebracht werden, wodurch sich die Pfadlänge auf ein 1-Bit-BYPASS-Register reduzieren lässt. Diese Register gehören allerdings immer noch zur Scan-Kette, so dass ihre maximale TCK-Frequenz berücksichtigt werden muss.

- 10 Tipps für Boundary-Scan

- 10 Tipps für Boundary-Scan (4 - 7)

- 10 Tipps für Boundary-Scan (8 - 10)