JTAG-Testintegrität

Den Signalen auf der Spur

Fortsetzung des Artikels von Teil 2

Minimierung der Schleifenfläche II

Schon während der Designphase ist sicherzustellen, dass eine Leiterplatte gründlich und zuverlässig getestet werden kann. Optimierungen in einem PCB-Design lassen sich in zwei Kategorien aufteilen. In Verbesserungen der Signalverbindungen zur und innerhalb der Leiterplatte. Für die erste sollte eine Testvorrichtung geschaffen werden, die den Loop-Bereich minimiert:

- Bei Verwendung von Pins müssen ein Bodentestpunkt und ein TAP-Signal-Testpunkt nahe beieinander liegen. Wenn der Platz auf dem Board begrenzt ist, sollte zumindest ein Bodentestpunkt für jedes TAP-Signalpaar berücksichtigt werden

- Bei der Verwendung von Kopfzeilen, die über Flachbandkabel angeschlossen werden, bedarf es zwischen den einzelnen TAP-Signalen im Flachbandkabel eines Massekerns. Ist die Anzahl der Pins begrenzt, sollten zumindest Masse-Kerne auf beiden Seiten der Taktsignale (wie TCK) vorhanden sein

Es ist ausserdem zu beachten, dass TAP-Signale bis zu Frequenzen von 20 MHz übersteigend takten können. Daher sollten sie wie alle anderen Signale mit ähnlichen Frequenzen behandelt werden:

- Der Signal-Abschluss auf die Signale ist so anzuwenden, wie es in den JTAG DFT-Richtlinien festgelegt ist. Diese folgen den bewährten Standard-Design-Verfahren, wie das Platzieren paralleler Abschlusswiderstände so nahe wie möglich am Empfängerende einer Leitung

- Stichleitungen (stubs) sind zu vermeiden, Puffer verbessern zudem das Signal-Fan-Out

- TAP-Signale sollten über eine kontinuierliche Massefläche geroutet werden. Wenn es darin Unterbrüche gibt, ist die Schleifenfläche vergrössert. Dies macht das Board anfälliger für Unzuverlässigkeiten beim Test

Jobangebote+ passend zum Thema

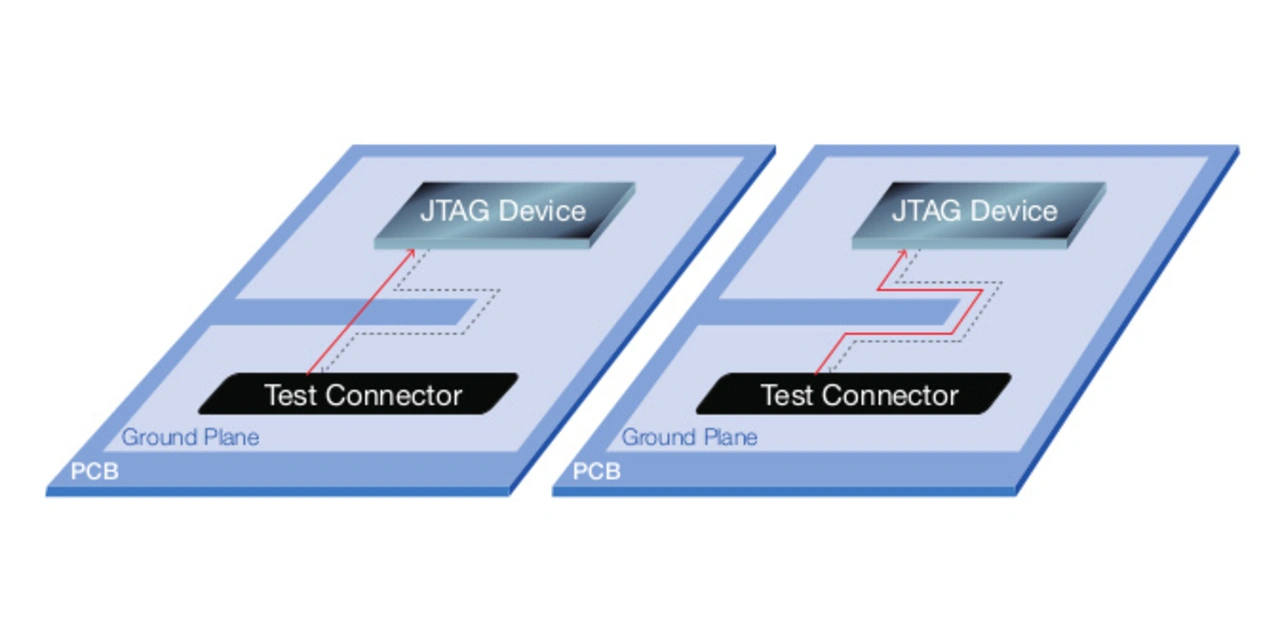

Bild 5a zeigt, wie das Routing von einem TAP-Signalverlauf (rot) über einen Unterbruch in einer Massefläche den Rückstrompfad (schwarz gestrichelt) beeinflussen kann. Dies führt zu einer grösseren Schleifenfläche als ursprünglich erwartet und somit zu einer Verschlechterung der Signalintegrität.

Obwohl die Leiterbahn in Abbildung 5b länger ist, wäre die Gesamtschleifenfläche hier vermindert und so dies die bevorzugte Lösung, sofern die Masse-Platte nicht geändert werden kann.

Die Minimierung der Schleifenfläche wird immer als Faustregel gelten können, ist als solche aber nicht immer anwendbar. Aber die Kenntnis, welche Strecke der Rückstrom eines Signals nimmt, kann eine solide Grundlage bei der Planung von Leiterplatten, der Bestimmung der Pin-outs für Steckverbinder oder das Entwerfen und Erstellen von Testgeräten sein. Wird dies als fester Teil des Entwurfsprozesses berücksichtigt, können teure und zeitaufwendige Verzögerungen im Entwicklungsprozess vermieden werden. Sofern verfügbar, sollten die DFT-Richtlinien eingesehen werden, weil diese zusätzliche Informationen enthalten, welche die Testbarkeit von Prüflingen und die Zuverlässigkeit dieser Tests weiter verbessern.

- Den Signalen auf der Spur

- Minimierung der Schleifenfläche I

- Minimierung der Schleifenfläche II

- Fragerunde mit Stephen Love - JTAG-Basics

- Fragerunde mit Stephen Love - JTAG-Testdesign