Cypress

FPGAs per USB konfigurieren

Fortsetzung des Artikels von Teil 1

Arten der Konfiguration von FPGAs

Zum Konfigurieren können die FPGAs entweder in den Master-Modus oder den Slave-Modus geschaltet werden. Im Master-Modus erzeugt das FPGA das Taktsignal für die Konfiguration und es steuert die Übertragung der Konfigurationsdaten. In diesem Modus übernimmt das FPGA gewöhnlich den Bitstream zur Konfiguration aus nicht flüchtigem Speicher, z.B. SPI, Flash oder EPROM. Beim Einsatz von SPI Flash fungiert das FPGA als SPI-Master, wobei die Konfiguration aus dem SPI Flash übernommen wird. Eine andere Möglichkeit ist, dass das FPGA die Konfigurationsdaten aus einem EPROM lädt. Nicht-flüchtiger Speicher wie EPROM kann intern oder extern vorgesehen werden, befindet sich aber normalerweise außerhalb des FPGA.

Jobangebote+ passend zum Thema

Im Slave-Modus kann das FPGA mit Hilfe externer intelligenter Bauteile, z.B. Mikrocontrollern, Mikroprozessoren und digitalen Signalprozessoren bzw. über eine JTAG- oder USB-Schnittstelle konfiguriert werden. Die drei gebräuchlichsten Verfahren, die bei intelligenten Bauteilen wie Mikrocontrollern, Mikroprozessoren und DSP verwendet werden, um die Konfigurationsdaten zu übertragen, sind die Betriebsarten synchron seriell, SPI Slave und parallel.

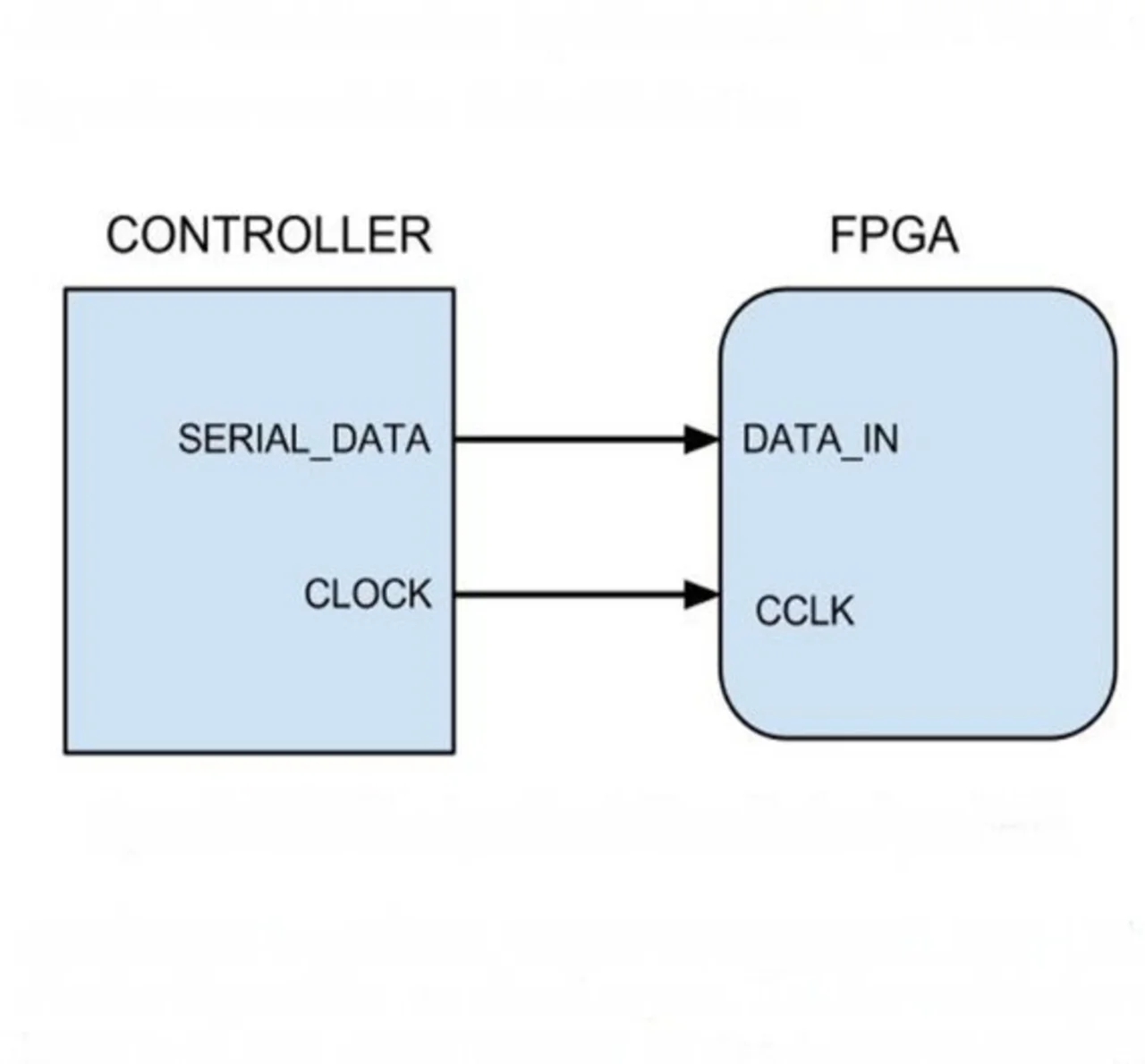

Synchron-serielle Schnittstelle: Bei diesem Verfahren werden gewöhnlich zwei Leitungen – Daten und Takt – verwendet, um die Konfiguration zu übertragen. Bei der aufsteigenden Flanke des Taktsignals werden die Datenbits der Konfiguration in das FPGA übernommen.

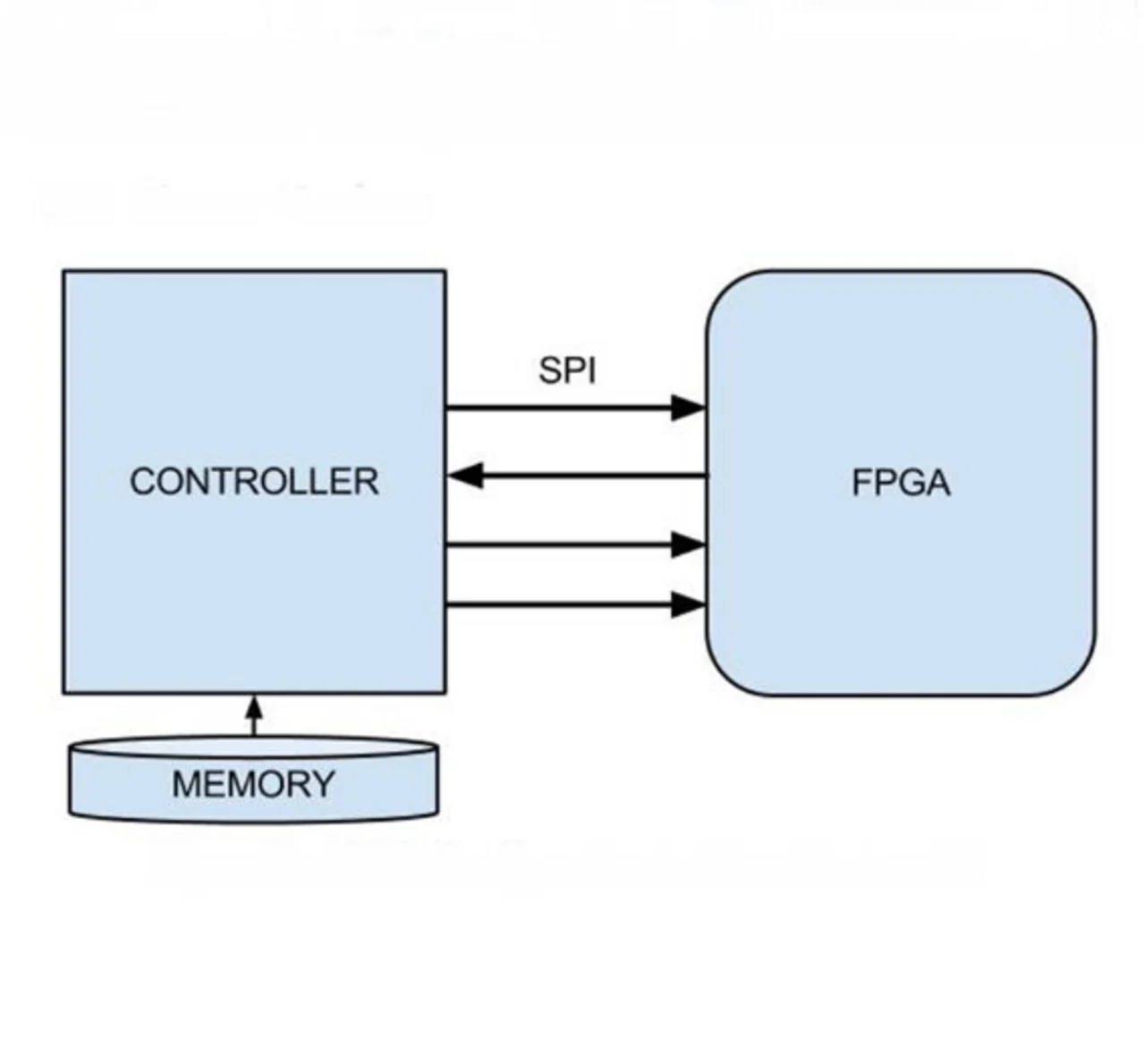

SPI Slave-Modus: Hierbei arbeitet das FPGA als SPI Slave und ein externer Mikroprozessor, Mikrocontroller oder DSP als SPI Master. Der Prozessor bzw. der Controller lädt die Bitstream-Daten zur Konfiguration aus einem externen Speicher über die SPI-Leitungen.

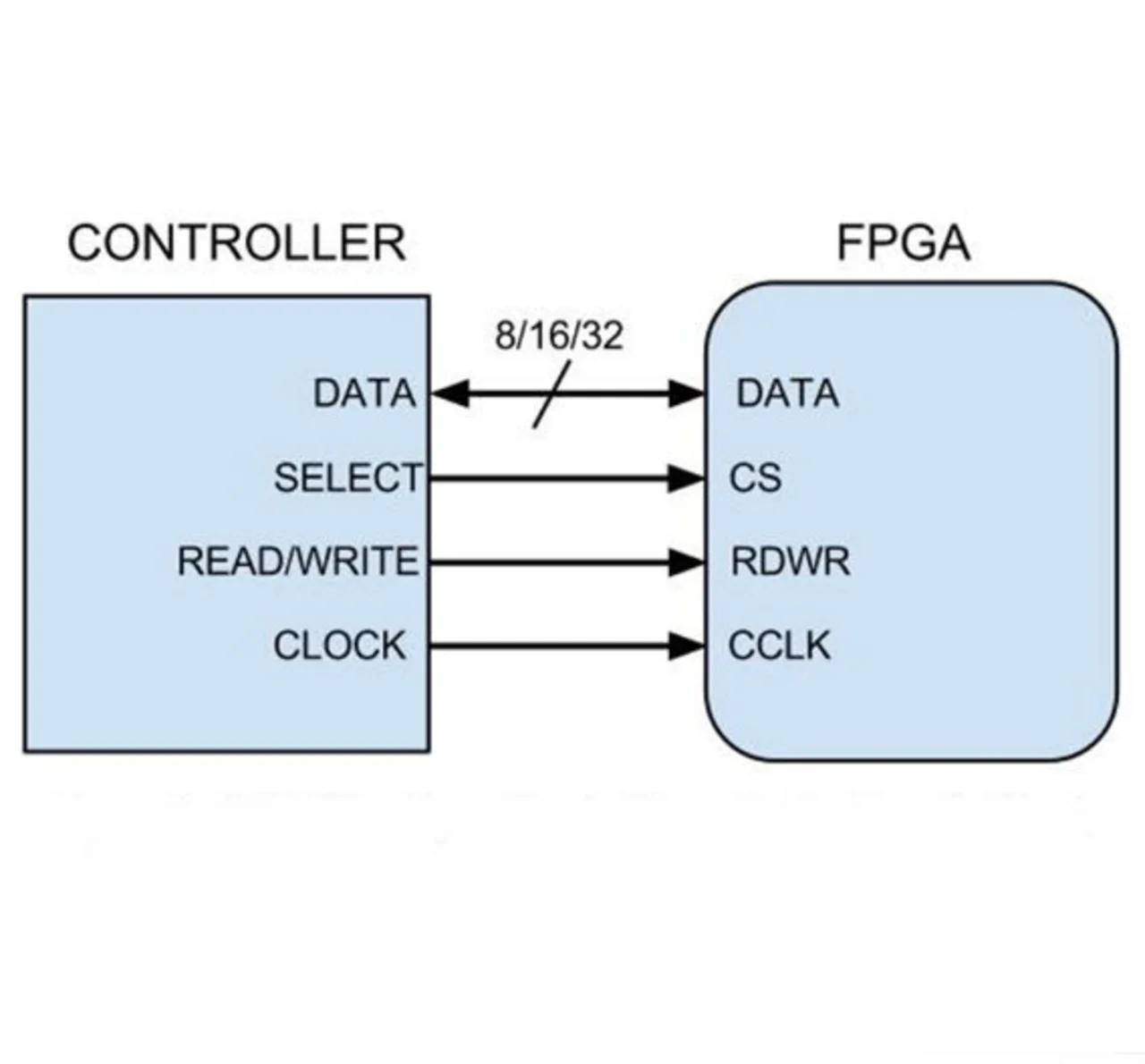

Paralleler Modus (8, 16 oder 32 Bit): Bei den meisten FPGAs besteht die Option, für die parallele Übertragung der Konfigurationsdaten zwischen 8, 16 und 32 Bit auszuwählen. Dies ist eines der schnellsten Verfahren zur Übertragung der Konfigurationsdaten.

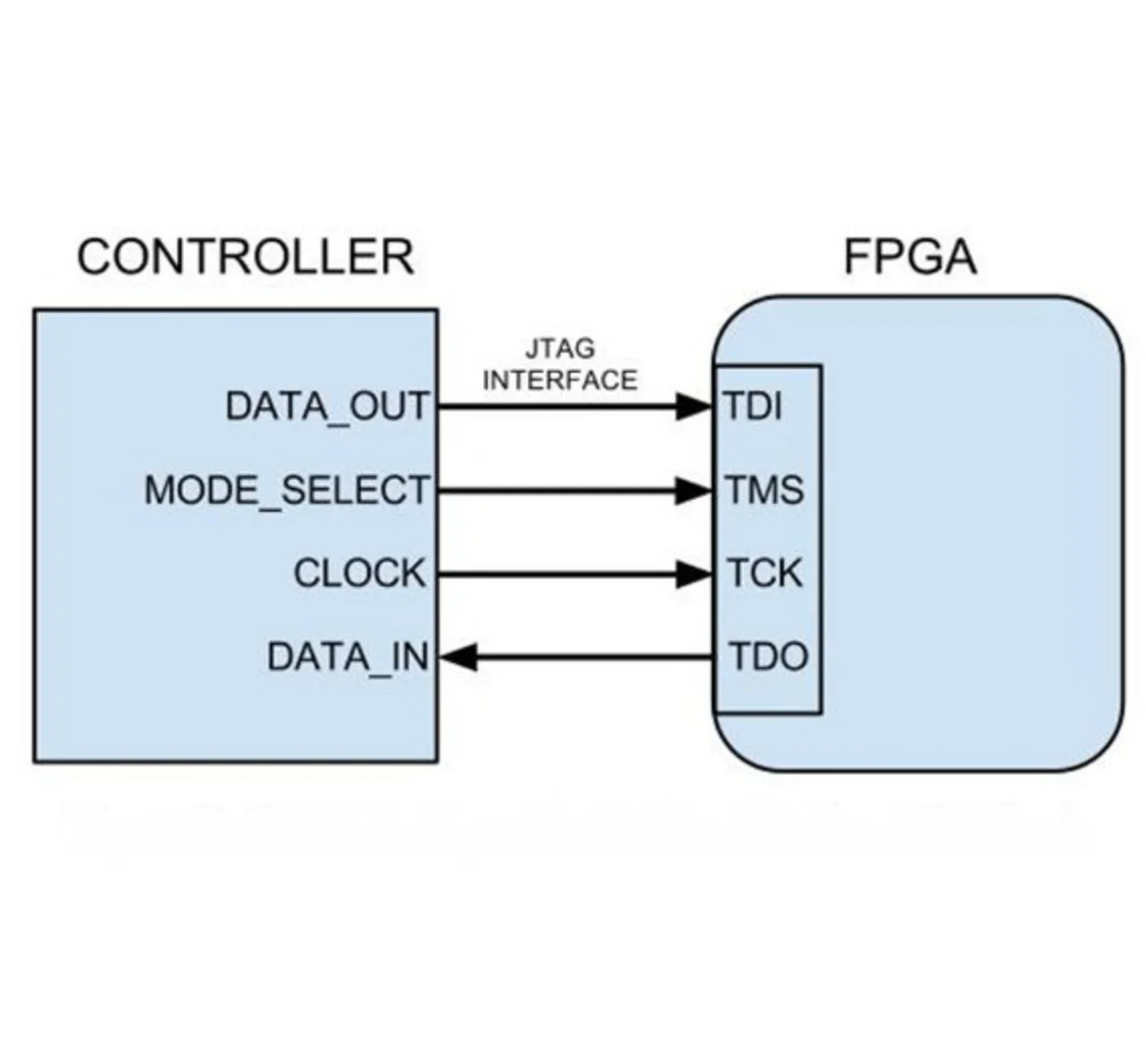

Konfiguration über die JTAG-Schnittstelle: Die JTAG-Schnittstelle ist eine vier- oder fünfpolige serielle Schnittstelle. Die fünf Leitungen sind: TDI (Test Data In), TDO (Test Data Out), TCK (Test Clock), TMS (Test Mode Select) und TRST (Test Reset). Der Anschluss TRST ist optional. JTAG wird verbreitet zum Debugging von Hardware für Boundary-Scan-Tests eingesetzt. Diese Schnittstelle kann auch zur Programmierung der Konfiguration benutzt werden.

- FPGAs per USB konfigurieren

- Arten der Konfiguration von FPGAs

- Konfiguration eines FPGAs über eine USB-Schnittstelle