Zwitter aus MCU und SoC

NXP liefert ersten i.MX mit Cortex-M7

Man nehme einen i.MX-SoC mit Apps-Prozessor und ersetze ihn durch einen für MCUs entwickelten Cortex-M7. Das Ergebnis ist eine Art Zwitter, den NXP Crossover-Prozessor nennt und der Rekordwerte bei Rechenleistung und Energieeffizienz liefert. Hier ist unsere Analyse des i.MX RT1050.

Die Zutaten für den mit 600 MHz getakteten i.MX RT1050 sind folgende: Man nehme einen i.MX 6ULL mit dem Applikationsprozessor Cortex-A7, ersetze diesen durch einen Cortex-M7 und fertige den Chip statt in einem Flash-Prozess in einem 40-nm-CMOS-Prozess. Das Ergebnis ist eine Rechenleistung von 3020 CoreMark, welche den bisherigen Top-Cortex-M7-Controller, den 400-MHz-STM32H7 von STMicroelectronics [1], um 50 % übertrifft, sowie eine Leistungsaufnahme im aktiven Modus von nur 110 µA/MHz bei 3,3 V aufweist – weniger als die Hälfte der 263 µA/MHz des STM32H7. Tatsächlich kommt der RT1050 von der absoluten Rechenleistung sogar an den mit Cortex-A7-Applikationsprozessor ausgestatteten und mit 900 MHz getakteten i.MX 6ULL heran, da der Cortex-A7 mit 3 CoreMark/MHz deutlich unter den 5 CoreMark/MHz des Cortex-M7 liegt.

NXP positioniert den RT1050 als eine Alternative zu Cortex-A-basierten Anwendungsprozessoren und zielt auf Embedded-Geräte ab, die einerseits mit hochauflösenden Displays ausgestattet sind und andererseits geringe Leistung aufnehmen und eine schnelle Interrupt-Latenzzeiten brauchen, letztere sind Eigenschaften typischer Mikrocontroller. Der Nachteil gegenüber einem Cortex-A-SoC ist natürlich, dass schon auf Grund der nicht vorhandenen MMU (Memory Management Unit) kein Linux-Betriebssystem ausgeführt werden kann. Insofern dürfte der Wettbewerb in erster Linie mit herkömmlichen Hochleistungs-MCUs ausgefochten werden, als da neben dem STM32H7 noch mit Abstrichen der STM32F7 (300 MHz, 1082 CoreMark) sowie Microchips SAME70 (300 MHz, 1500 CoreMark) zu nennen wären. Diese Controller finden sich unter anderem in industriellen Anwendungen, Medizingeräten oder Verkaufsautomaten, die allesamt grafische 2D-Benutzerschnittstellen haben.

Cortex-M7 vs. Cortex-A7

Der Quasi-Austausch des Cortex-A7 gegen den Cortex-M7 hat unterschiedliche Auswirkungen. Im positiven Sinn reduziert sich die Interrupt-Latenz von Hunderten von Taktzyklen auf 12 Taktzyklen oder 20 ns, was den RT1050 für Echtzeitanwendungen brauchbar macht. Durch den Cortex-M7 kann der Programmierer dessen DSP-Erweiterungen nutzen, welche dem A7 fehlen, dem M7 fehlen dagegen neben der MMU und damit Linux auch die Neon-SIMD-Instruktionen. Gemeinsam ist den beiden Chips RT1050 und 6ULL die Unterstützung von MQX-RTOS, was aber beim 6ULL eher selten eingesetzt wird.

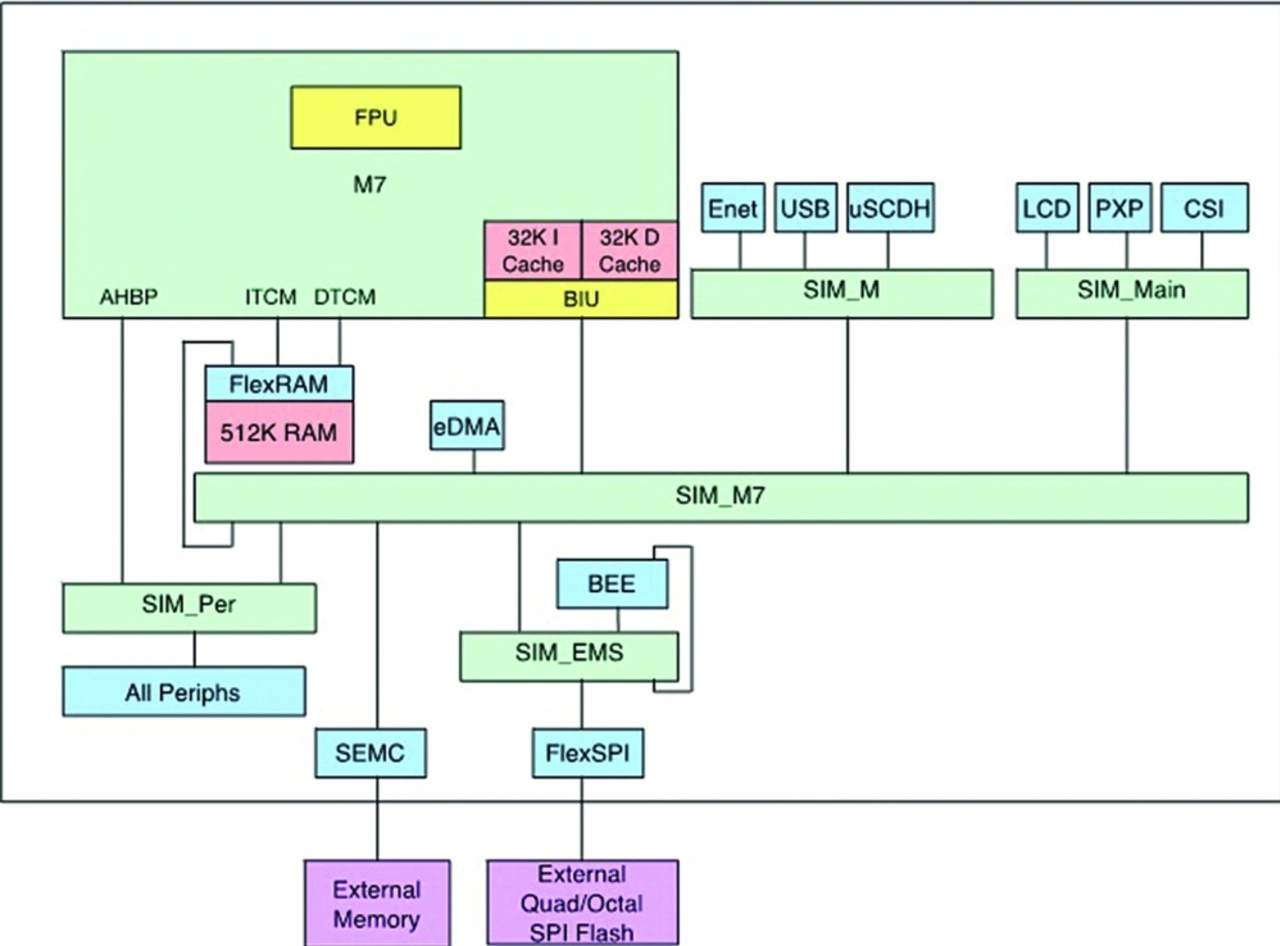

Jobangebote+ passend zum Thema

Der RT1050, der in seiner industriellen Ausführung für einen Temperaturbereich von -40 °C bis +105 °C qualifiziert ist, ist auf maximale Energie- und Kosteneffizienz designt worden. Er kommt in einem Low-Cost-Package 10 mm × 10 mm BGA mit 0,65 mm Pitch (130 GPIOs) daher – was 2- oder 4-Schicht-PCB-Designs ermöglicht) und weist einen limitierten Speicher auf dem Chip auf. Neben den jeweils 32 KB großen Caches des Cotrex-M7 für Daten und Befehle sind dies 512 KB SRAM, die entweder für allgemeine Zwecke oder insgesamt oder teilweise in 32-KB-Portionen als TCM (eng angebundener Speicher, tightly coupled memory) mit einem Taktzyklus Zugriffszeit konfiguriert werden können. Dies ist die Hälfte vom STM32H7, dessen 1 MB SRAM zudem mit fehlererkennenden beziehungsweise korrigierenden Codes (ECC) geschützt sind. Allerdings kann der STM32H7 für zeitkritische Routinen von seinen 1 MB SRAM nur 64 KB für Befehls-TCM und 128 KB für Daten-TCM nutzen. Ein Embedded-Flash-Speicher (2 MB beim STM32H7, ebenfalls mit ECC) fehlt beim RT1050 natürlich komplett, was den Chip klein hält und damit preiswert macht. Kritische Routinen, bei denen ein Zugriff auf externen Speicher zu langsam wäre, müssen daher wohl oder übel in den TCM geladen werden, sodass nur ein kleiner Teil des On-Chip-SRAM zur Datenspeicherung übrig bleibt. Laut NXP reduziert die Kombination aus L1-Cache und TCM-Zugriff die Cache-Miss-Rate des RT1050 für die meisten Anwendungen auf weniger als 2 %. Bild 1 zeigt die Architektur des RT1050. Abgesehen von der Beseitigung der DDR-Unterstützung behält der neue Prozessor die gleichen externen Speicherschnittstellen wie der 6ULL bei.

Externer NOR- oder NAND-Flash-Speicher und SDRAM werden beim RT1050 über eine Quad-SPI-Schnittstelle angebunden, welche eine sogenannte Bus-Verschlüsselungs-Engine aufweist. Dies bedeutet, dass »on-the-Fly-Daten«, die mittels AES-128 verschlüsselt im externen Speicher liegen, beim Lesen ohne Wartezyklen entschlüsselt werden. Aus Kostengründen arbeitet der Chip nur mit 8-/16-bit-Ports, was neben einer geringeren Bandbreite auch einen kleineren Speicher-Adressraum bedeutet als bei den 32-Schnittstellen der Konkurrenz.

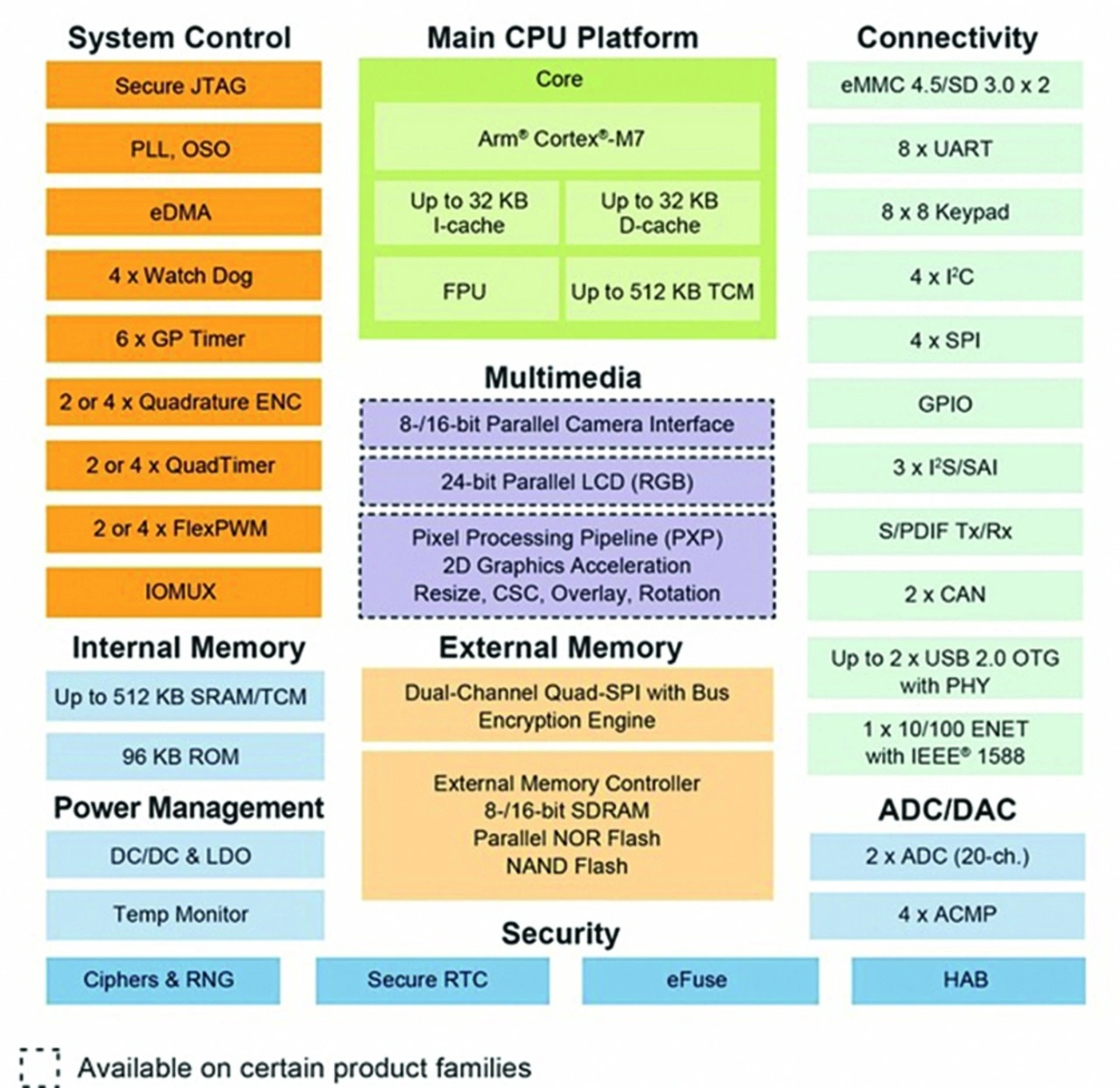

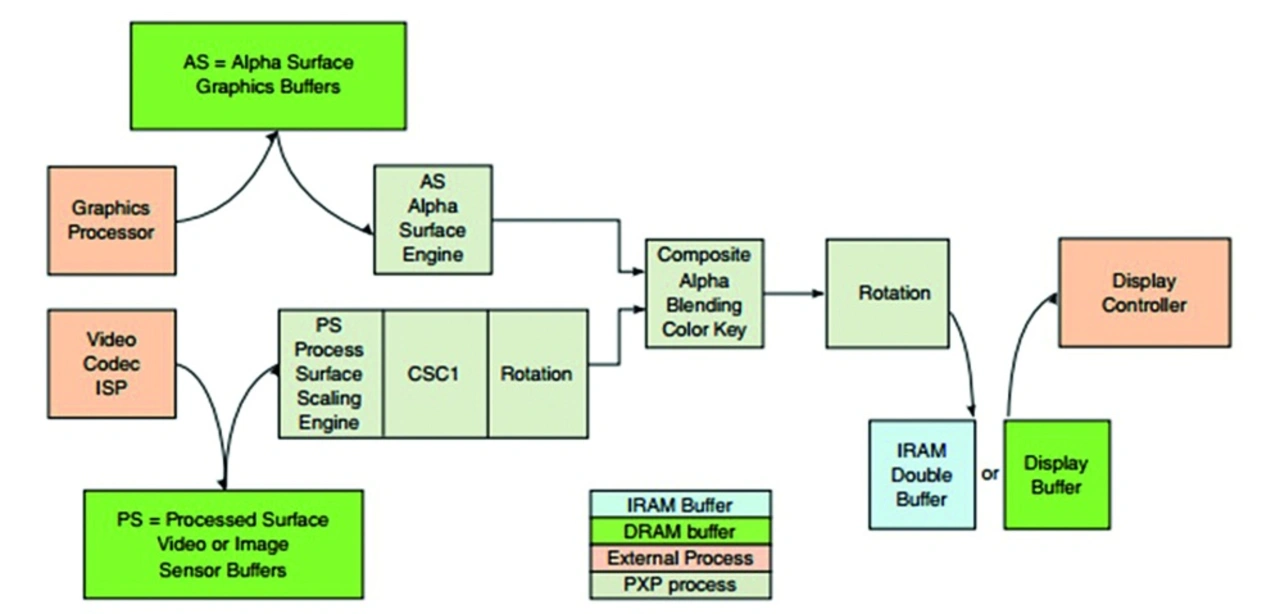

Der RT1050 bietet dieselben Konnektivitätsschnittstellen und Systemsteuerungsfunktionen wie sein Cortex-A-Pendant. Wie Bild 2 zeigt, enthält der Chip NXPs bekannte generische 2D-Grafik-Engine (PXP, Pixel Processing Pipeline) sowie einen LCD-Displaycontroller, der bis zu WXGA-LCDs (1366×768 Pixel) bei 60 Frames/s treiben kann. Daten können dabei parallel bis zu 24 bit Datenbusbreite übertragen werden, möglich sind auch 8, 16 und 18 bit. Tabelle 1 zeigt die unterstützten Auflösungen. Bild 3 zeigt die Architektur der Grafikengine PXP. Sie liefert unter anderem eine Farbraumkonvertierung von YUV nach RGB, auf- und abskalieren von Bildern mit bilinearen Filtern, Bildrotationen um 90, 180 und 270 Grad, vertikale und horizontale Spiegelungen des Bildes sowie Chroma Keying, ein visueller Effekt beziehungsweise eine Postproduktionstechnik, bei der eine Chrominanz zum Freistellen von Bildmaterial verwendet wird.

Die Herstellung in einem standardmäßigen 40-nm-CMOS-Prozess reduziert die Kosten im Vergleich zur Embedded-Flash-Technologie, wodurch NXP den RT1050 zu einem niedrigeren Preis anbieten kann als seine Konkurrenten ihre Mikrocontroller. Der RT1050 kostet bei einer Abnahme von 10.000 Stück nur 2,98 Dollar, im 2. Quartal 2018 kommt mit dem RT1020, der maximal mit 500 MHz getaktet werden wird, ein noch kostengünstigeres Modell auf den Markt: Es wird lediglich 2,18 USD bei einer Abnahme von 10.000 Stück kosten. Dafür hat er nur 16 KB/16 KB Cache für den Cortex-M7 und 256 KB SRAM. Seitens der Peripherie ist er mit nur 2 statt 4 Flex-PWMs ausgestattet, mit 2 statt 4 Quad-Timern, 2 statt 4 ENCs und nur 1 statt 2 High-Speed-USBs. PXP, LCD-Schnittstelle und Kamera-Schnittstelle fehlen, der RT1020 adressiert somit Anwendungen ohne grafische Benutzerschnittstelle. Der Chip wird entweder im 144 LQFP (20 mm × 20 mm) oder 100LQFP (14 mm × 14 mm) mit jeweils einem 0,5 Pitch geliefert.

Integrierte Stromversorgung

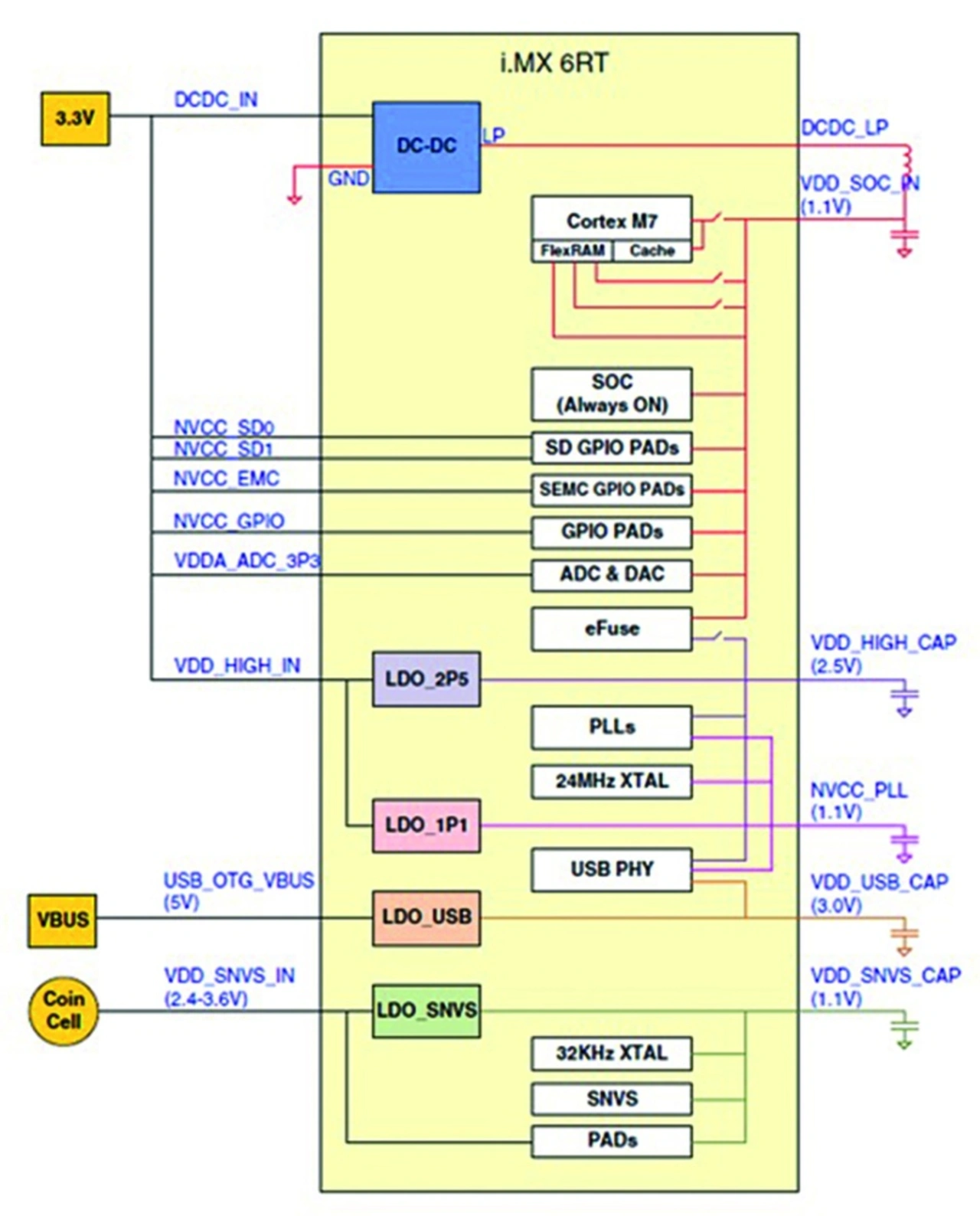

Kostensparend wirkt sich auch der On-Chip-DC-DC-Wandler in der Stromversorgung des Chips aus, die mit einem einzigen 3,3-V-Eingang leben kann. Neben dem DC-DC-Wandler finden sich noch vier integrierte Low-Drop-Längsregler (LDO) auf dem Chip. Bild 4 zeigt eine mögliche Beschaltung des RT1050.

Der Chip benötigt bei seiner maximalen Taktfrequenz von 600 MHz und einer Versorgungsspannung von 3,3 V nur 200 mW, verglichen mit mehr als 1 W für den i.MX6 ULL mit 900 MHz. Diese Tatsache ist für Entwickler batteriebetriebener IoT-Geräte sowie für medizinische Geräte und industrielle Automatisierungssysteme sehr attraktiv.

Während also der Chip im aktiven Modus auf hervorragende Werte bezüglich der Stromaufnahme kommt, erhöht die Verwendung von Transistoren mit höherer Schaltgeschwindigkeit jedoch die Leckströme, weshalb die Stromaufnahme im Standby 15 µA beträgt gegenüber nur 4 µA für den STM32H7. Wie Tabelle 1 zeigt, weisen die beiden Chips jedoch ansonsten ähnliche Merkmale auf. Der i.MX RT1050 weist den doppelten Cache des STM32H7 auf, wie schon beschrieben ist bei ST das SRAM doppelt so groß. Der STM32H7 verwendet kleinere 64 KB- und 128 KB-Befehls-/Daten-TCMs, diese sind aber nur ein kleiner Teil des insgesamt 1 MB großen SRAMs. Die verbleibenden 864 KB sind für allgemeine Zwecke verfügbar. Damit werden insbesondere bei umfangreichen Anwendungen die Zugriffe auf externen Speicher reduziert.

| Auflösung | Breite | Höhe | Mega-pixel |

|---|---|---|---|

| VGA | 640 | 480 | 0,31 |

| PAL | 720 | 480 | 0,36 |

| WVGA | 800 | 480 | 0,38 |

| NTSC | 720 | 576 | 0,41 |

| SVGA | 800 | 600 | 0,48 |

| WSVGA | 1024 | 600 | 0,61 |

| XGA | 1024 | 768 | 0,79 |

| HD720 | 1280 | 720 | 0,92 |

| WXGA | 1366 | 768 | 1,05 |

Tabelle 1: Unterstützte Auflösungen der LCD-Schnittstelle. Die typische Pixelrate beträgt 27-74,25 MegaPixel/s.

Vergleicht man die Grafik-Engines, so steht NXPs PXP STs sogenannter Chrom-ART-Beschleuniger gegenüber. Chrom-ART ist ein Hardware-Beschleuniger für 2D-Grafikoperationen, der in Grafik-Stacks integriert und für den Software-Entwickler somit unsichtbar ist. Es handelt sich im Grunde genommen um eine 2D-DMA-Engine, welche schnelle Datenkopier-Operationen zwischen zwei Ebenen mit Pixel-Konversion als auch Blending-Operationen ermöglicht. Er führt Bildfüll- und Bildmischoperationen sowie Überlagerungen aus, einschließlich Text und Bildern. Der integrierte JPEG-Codec von ST ist eine leistungsstärkere Engine für das Abspielen von Motion-JPEG-Videos (MJPEG) und bietet außerdem Komprimierungsfunktionen, um die Bandbreite für Bilder von der Kameraschnittstelle zu reduzieren.

Zwischen MCU und Applikationsprozessor

Mit seiner i.MX RT-Serie möchte NXP eine neue Low-Cost/High-Performance-Kategorie zwischen traditionellen MCUs und Anwendungsprozessoren definieren. Statt aus dem On-Chip-Flash-Speicher wird der Programmcode aus externem Speicher ausgeführt beziehungsweise teilweise aus den TCMs, wenn er zeitkritisch ist. Dieser Ansatz reduziert den Kostenvorteil des Chips an sich, hat aber auch Vorteile, zum Beispiel dass 2 MB externer NOR-Flash bis zu 60 % schneller programmiert werden kann als eine MCU mit 2 MB embedded-Flash. Obwohl die NXP- und ST-Prozessoren größtenteils ähnliche Funktionen bieten, ist der RT1050 für Low-Power-Designs von großem Vorteil. Der eingebaute DC-DC-Wandler ermöglicht es, 40 % weniger Energie zu verbrauchen, wenn er mit der gleichen Frequenz wie die ST-MCU betrieben wird. Kunden, die sicherheitskritische Industriesysteme bauen, dürften jedoch den STM32H7 wegen seiner ECC-geschützten Speicher bevorzugen. Der RT1050 wird Entwickler ansprechen, die mit der RTOS-Programmierplattform der MCU vertraut sind, die auch auf dem i.MX6 ULL läuft. Die beiden Produkte verwenden das gleiche Herstellungsverfahren und liefern im Wesentlichen die gleiche Rechenleistung. Die kleinere Cortex-M7-CPU wird im Vergleich zum Cortex-A7-Äquivalent nur marginale Kosteneinsparungen bringen, da SRAM und I/Os den größten Teil des Chipbereichs ausmachen. Anwendungen, die auf Linux oder Android aufsetzen, können nicht auf dem Cortex-M7-Prozessor laufen. Entwickler von RTOS-basierten Systemen hingegen werden sich aufgrund seiner Kombination aus niedrigen Kosten und niedriger Stromaufnahme für den RT1050 entscheiden.Auch wenn NXPs Ziel klar darin besteht, am oberen Ende der MCU-Anwendungen STMicroelectronics Marktanteile abzunehmen, könnte damit eine unangenehme Nebenwirkung verbunden sein: Die Kannibalisierung des eigenen i.MX6 ULL-Geschäftes.

| NXP i.MX RT1050 | ST Microelectronics STM32H753xl | |

|---|---|---|

| CPU | ARM Cortex-M7 | ARM Cortex-M7 |

| CPU fmax | 600 MHz | 400 MHz |

| L1-Cache Befehle/Daten | 32/32 KB | 16/16 KB mit ECC |

| SDRAM/TCM | 512 KB | 1 MB mit ECC |

| Flash on Chip | - | 2 MB mit ECC |

| Speicherschnittstellen | 8/16 bit parallel SDRAM/SLC NAND mit ECC, NOR | 32 bit parallel NOR, NAND, PSRAM, SRAM, SDRAM, LPSDR SDRAM |

| SPI | 1× Quad | 2 × Quad |

| eMMC/SD-Schnittstellen | 1 | 2 |

| Display-Controller | bis zu WXGA-LCD 1366×768 Pixel | bis zu XGA TFT LCD (1024×768 Pixel) |

| Grafik | PXP 2D-Hardware-Engine | Hardware 2D-Chrom-ART und JPEG-Codec |

| CAN | 2 | 2 FD |

| Ethernet | 100 Mbit Ethernet MAC | 100 Mbit Ethernet MAC |

| PWM | 4 × FlexPWM | 2 |

| USB 2.0 | 2 | 2 |

| SDIO | 2 | 2 |

| A/D-Wandler | 2 jeweils 12 bit Auflösung | 3 jeweils 14-16 bit Auflösung |

| Rechenleistung (CoreMark) bei fmax | 3037 | 2020 |

| Stromaufnahme CPU aktiver Modus bei fmax | 66 mA | 105,2 mA |

| Stromaufnahme CPU Standby | 15 µA | 4 µA |

| Energieeffizienz (CoreMark/Iaktiv) bei fmax | 46 CM/mA | 19,2 CM/mA |

| Massenfertigung | seit 4. Quartal 2017 | seit 4. Quartal 2016 |

| Fertigungsprozess | 40 nm CMOS | 40 nm eFlash |

| Listenpreis bei Abnahme von 1000 Stück | 4,01 USD | 8,17 USD |

Vergleich zwischen NXPs i.MX RT1050 Crossover-Prozessor und ST Microelectronics STM32H753xl Mikrocontroller. Der RT1050 ist billiger und energieeffizienter, da er in einem Standard-40-nm-CMOS- statt in einem Embedded-Flash-Prozess gefertigt wird. Den fehlenden Flash-Speicher on Chip muß er mittels externem Speicher bzw. den TCMs für kritische Programmteile kompensieren.

Referenz

Riemenschneider, F.: 40-nm-STM32H7 bringt ARMs Cortex-M7 auf 400 MHz. http://www.elektroniknet.de/design-elektronik/halbleiter/40-nm-stm32h7-bringt-arms-cortex-m7-auf-400-mhz-134910.html

- NXP liefert ersten i.MX mit Cortex-M7

- »Außer Siliziumnitrid-Flash gibt es quasi keine Optionen!«