FPGAs: Arria II GX, ECP-3 und Spartan-6 LXT im Vergleich

Fortsetzung des Artikels von Teil 1

FPGAs: Arria II GX, ECP-3 und Spartan-6 LXT im Vergleich

Alle FPGAs unterstützen dank ihrer 3,X-Gbit/s-Transceiver Protokolle wie PCI-Express Gen1 (Gen.2 benötigt 6,5-Gbit/s-Transceiver), Gigabit-Ethernet, CPRI für LTE, WiMAX, GPON, XAUI oder Triple-Speed SDI. Was die Preise angeht, gibt es Unterschiede: Die Spartan-6-FPGAs liegen bei 10 000 Stück Abnahme zwischen 3 und 55 Dollar, die Altera-Bausteine beginnen erst mit 15 Dollar bei 100 000 Stück Mindestabnahme. Lattice hat bislang nur Preise für das obere Ende genannt, das größte FPGA wird 50 Dollar bei einer Marge von 25 000 Stück kosten.

Jobangebote+ passend zum Thema

Schwierig ist die Einschätzung der Leistungsaufnahme, da es hierzu keine offiziellen Vergleichszahlen der Hersteller gibt und diese natürlich extrem vom Design abhängt. Sowohl Altera als auch Lattice und Xilinx sagen, dass die Leistungsaufnahme gegenüber den Vorgängergenerationen um 50 % gesenkt werden konnte, was bedeutet, dass ein ECP3 mit 150 K Logik-Elementen, einem zu 70 % aktiven und zu 30 % statischen Modus bei 85 °C ca. 1,5 W aufnehmen und damit leicht unter dem Arria II GX und Spartan 6 LXT liegen würde. Grund für diese Einsparungen sind, dass bei Lattice die Logik-Elemente mit speziellen (und damit langsameren) Low-Leakage-Transistoren aufgebaut sind, während DSP-Slices, Speicher-Schnittstelle usw. aus auf maximale Geschwindigkeit getrimmten Transistoren bestehen.

Für die oben genannten Zielgruppen spielen in vielen Fällen auch die Soft-Core-Prozessoren eine Rolle. Bei Flachbildschirmen ist es für eine dynamische Steuerung der Hinterleuchtung in Echtzeit z.B. hilfreich, eine Speicher-Management-Einheit (MMU) zur Verfügung zu haben. Der MicroBlaze 7 von Xilinx ist der einzige Soft-Core, der überhaupt eine Speichermanagement-Einheit enthält (s. Sonderheft Elektronik Embedded, Febr. 2008, S. 30ff.).

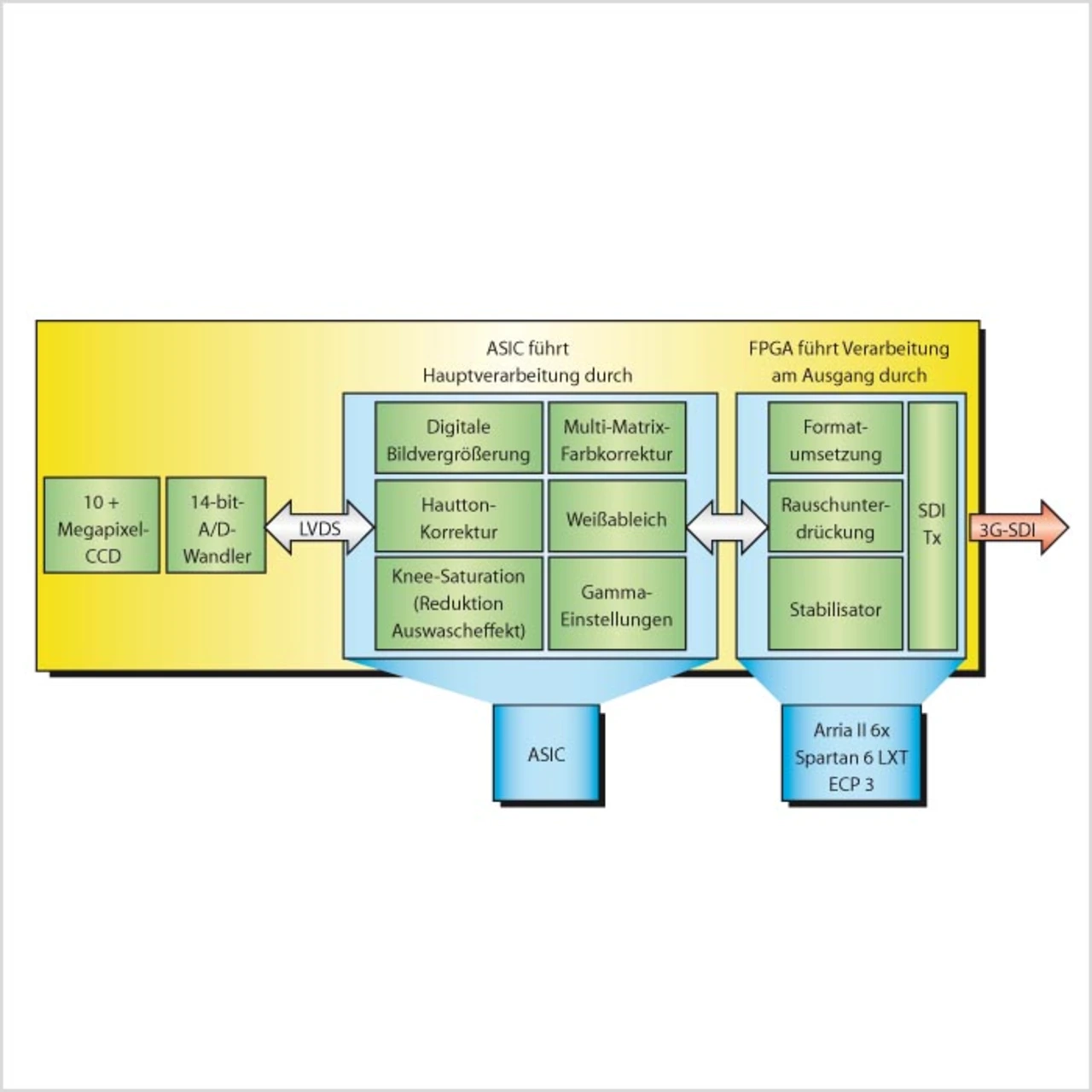

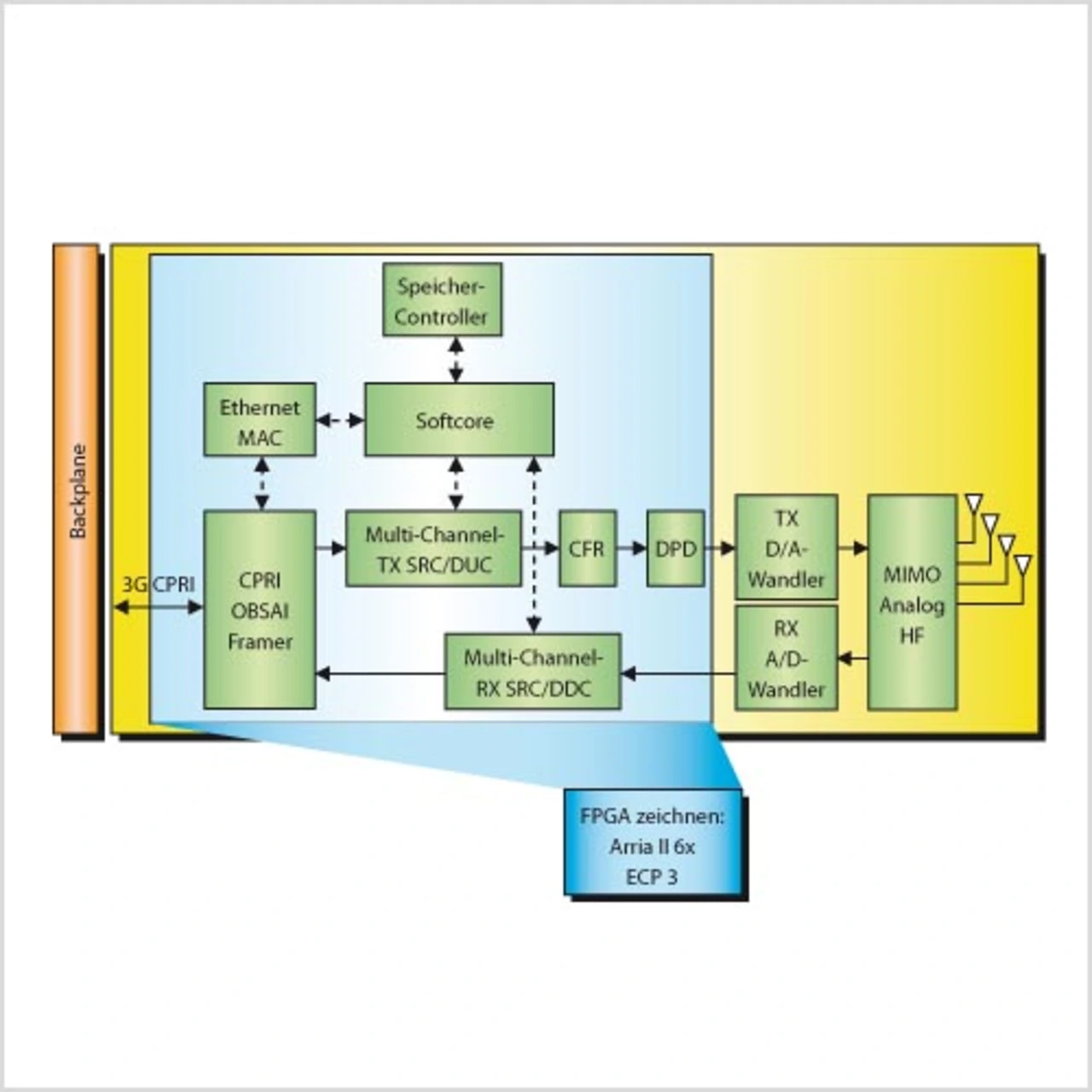

Bild 1 und Bild 2 zeigen zwei Beispiel-Applikationen. In Bild 1 ist die Bildverarbeitung mit einer professionellen 1080p-Kamera dargestellt, die dank des FPGA flexibel an unterschiedliche Formate angepasst werden kann. Die Minimalanforderungen an ein solches Design sind 50 K Logik-Elemente, zwei 3G-SDI unterstützende Transceiver und eine Leistungsaufnahme von weniger als 4 W. Bild 2 zeigt ein Remote-Radio-Head-System. RRH, steht beim Mobilfunk für die außentaugliche, allwetterfeste Montage von Spannungsversorgung, Sende- und Empfangsbaugruppe (Transceiver), Endverstärker und Duplex-Filter an den Antennenmast. Die Kommunikation mit der Basisstation erfolgt meist über eine Glasfaserverbindung. Hier sind 100 K Logik-Elemente, zwei 3-Gbit/s-Transceiver (CPRI), ein Transceiver für Gigabit-Ethernet und eine Leistungsaufnahme von weniger als 5 W erforderlich.

Beide Applikationen können sicher mit Bausteinen aus der Arria-II- und ECP3-Familie aufgebaut werden, mit dem Spartan-6-FPGA dürfte die Implementierung des RRH schwierig werden, da 192 Multiplizierer nicht ausreichen dürften. Dennoch gibt es auch für das Spartan-6-FPGA genug Applikationen, z.B. im Bereich Car-Infotainment, wo es auch auf den Soft-Core ankommt – und da liegt Xilinx ja ganz weit vorne. fr

Siehe auch:

Datenraten bis zu 8,5 Gbit/s

- FPGAs: Arria II GX, ECP-3 und Spartan-6 LXT im Vergleich

- FPGAs: Arria II GX, ECP-3 und Spartan-6 LXT im Vergleich