Prozessorkarte zur Verarbeitung rechenintensiver Echtzeit-Modelle

FPGA entlastet Hauptprozessor von I/O-Verarbeitung

Fortsetzung des Artikels von Teil 2

Lösungen aus Standard-PCs für Echtzeit-Systeme nicht optimal

Der Vorteil des PCI- bzw. PCI-X-Busses als Schnittstelle zur I/O besteht darin, dass man mit Standard-Mainboards arbeiten kann. Aufgrund der Systemtopologie gängiger x86-Systeme (CPU – Northbridge – Southbridge – PCI) ergab sich bei den Messungen für einen einzelnen Lesezugriff eine minimale Latenzzeit von 800 ns. PCIund PCI-X-Bus verfügen zwar über eine hohe Übertragungsbandbreite und können große Datenmengen übertragen, allerdings sind die Busse nicht auf eine möglichst kurze Latenzzeit optimiert. Daher sind sie für ein Echtzeit- System mit den geforderten, extrem kurzen I/O-Latenzzeiten eher ungeeignet.

Zur Anbindung der I/O an die DDRSchnittstelle eines x86-Systems wäre eine Emulation des DDR-Speichers notwendig. Leider bietet dieses Interface keine Möglichkeit, I/O-Wait-Zyklen zu realisieren, die für den I/O-Bus benötigt werden. Zeitaufwendiges Polling wurde zugunsten der Leistung verworfen. Weiterhin stellt sich die Frage der Langlebigkeit des DDR-Interfaces, denn die Speicher-Schnittstelle in x86-Systemen vollzieht technische Neuerungen in kurzen Abständen (SDRAM – DDR-SDRAM – DDR2 – DDR3). Für eine langfristig verfügbare Lösung ist diese Möglichkeit deshalb ungeeignet.

Die bei der Prozessorkarte DS1005 bewährte Lösung, I/O direkt an den Frontside-Bus des Prozessors anzuschließen, wurde zuletzt näher untersucht. Anhand von Einzelmessungen konnte bei einem Intel Pentium 4 nachgewiesen werden, dass dieser Weg zu einer sehr leistungsfähigen Lösung führt. Da die Spezifikation des Frontside- Busses dieses Prozessors jedoch nicht verfügbar ist, konnte man diesen Weg nicht weiter verfolgen.

Jobangebote+ passend zum Thema

Halbierung der Latenzzeit durch Hypertransport

Ende 2002 wurden Details zur Architektur der ersten AMD-Opteron-Prozessorgeneration veröffentlicht. AMD ersetzte den veralteten Frontside-Bus durch die schnellere Hypertransport- Technologie, die vom Hypertransport- Konsortium standardisiert wird und deren Spezifikation öffentlich zur Verfügung steht. Dadurch kann dSPACE die I/O durch den Einsatz von FPGAs direkt an den Prozessor anschließen. Die Verfügbarkeit von Hypertransport- IP-Cores für FPGAs unterstützt diesen Weg zusätzlich. Erste Untersuchungen mit der Open-Core-Plus-Version des Altera Hypertransport Megacores hatten ergeben, dass sich auf diese Weise die I/O-Latenzzeit gegenüber PCI bzw. PCI-X um mehr als die Hälfte reduzieren lässt.

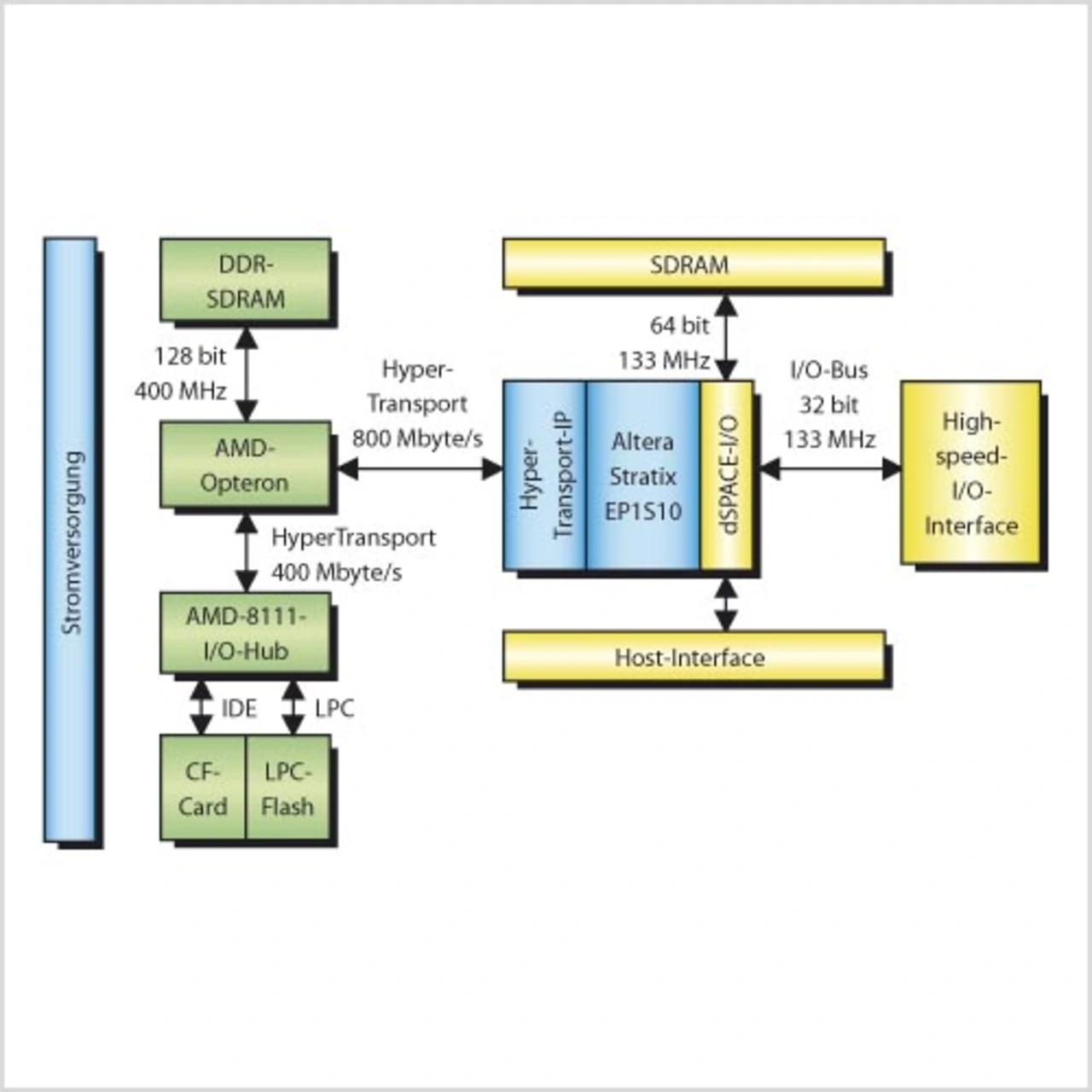

Neben dem standardisierten und offenen Hypertransport-Bus bietet der Opteron-Prozessor gegenüber anderen x86-Prozessoren einen weiteren wesentlichen Vorteil. Das in den Opteron- Prozessor integrierte Speicher- Interface erlaubt dem Prozessor den zeitgleichen Zugriff auf den Hauptspeicher während eines I/O-Zugriffs. Diese Vorteile – hohe Rechenleistung, gepaart mit einer direkten I/O-Anbindung an den Frontside-Bus – haben zu der Entscheidung geführt, das neue Prozessorboard DS1006 (Bild 2) mit dem AMD-Opteron-Prozessor zu entwickeln.

Um die Entwicklungszeit zu minimieren und das Prozessorboard DS1006 möglichst schnell auf den Markt bringen zu können, wurde bei diesem Projekt verstärkt auf die Integration bestehender Komponenten gesetzt. In der Konzeptphase ist die gesamte Architektur des Boards in klar abgegrenzte Komponenten mit sauberen Schnittstellendefinitionen gegliedert worden. Durch dieses Vorgehen konnte man die Komponenten größtenteils unabhängig voneinander entwickeln und testen. Bewährte Implementierungen aus vorherigen dSPACE- Designs und von externen Anbietern ließen sich problemlos integrieren. Beispielkomponenten sind der Hypertransport-Megacore von Altera und der bestehende High-speed-I/OBus von dSPACE.

- FPGA entlastet Hauptprozessor von I/O-Verarbeitung

- Trotz schnelllebigem PC-Markt: Vermeidung häufiger Redesigns

- Lösungen aus Standard-PCs für Echtzeit-Systeme nicht optimal